新型高分辨率LCD控制器的设计与实现*

2011-03-21陈重李浩陈曦

陈重,李浩,陈曦

(电子科技大学电子科学技术研究院,四川成都611731)

随着电子技术的发展,大屏幕LC D显示器越来越多地成为各种电子设备的显示终端。但是现有的大部分嵌入式处理器,因为其自身的总线速率限制了驱动大屏幕LCD的能力。例如自带LCD控制器的ARM嵌入式处理器(三星的2440),其系统总线的时钟频率最高只能达到133 MHz[1],除了要传输显示LCD屏的数据外,系统总线还要提供其他设备的数据吞吐,所以它的数据传输量只能满足小屏幕的显示,无法满足高分辨率屏幕的数据显示。

市场上有很多专用的LCD控制芯片,但是其价格较高、配置不灵活。因此,本文基于能够高速运行的FPGA[2]为处理核心,以SDRAM作为显示缓存,设计LCD控制器,既能够将ARM的系统总线上的显示数据取出,并驱动大屏幕显示数据,又能够解决专用芯片的弊端。成功地解决了嵌入式处理器在驱动大屏幕LCD时的资源紧张问题,并可提供清晰稳定的图像显示。

1 架构选择及硬件实现

1.1 架构分析选择

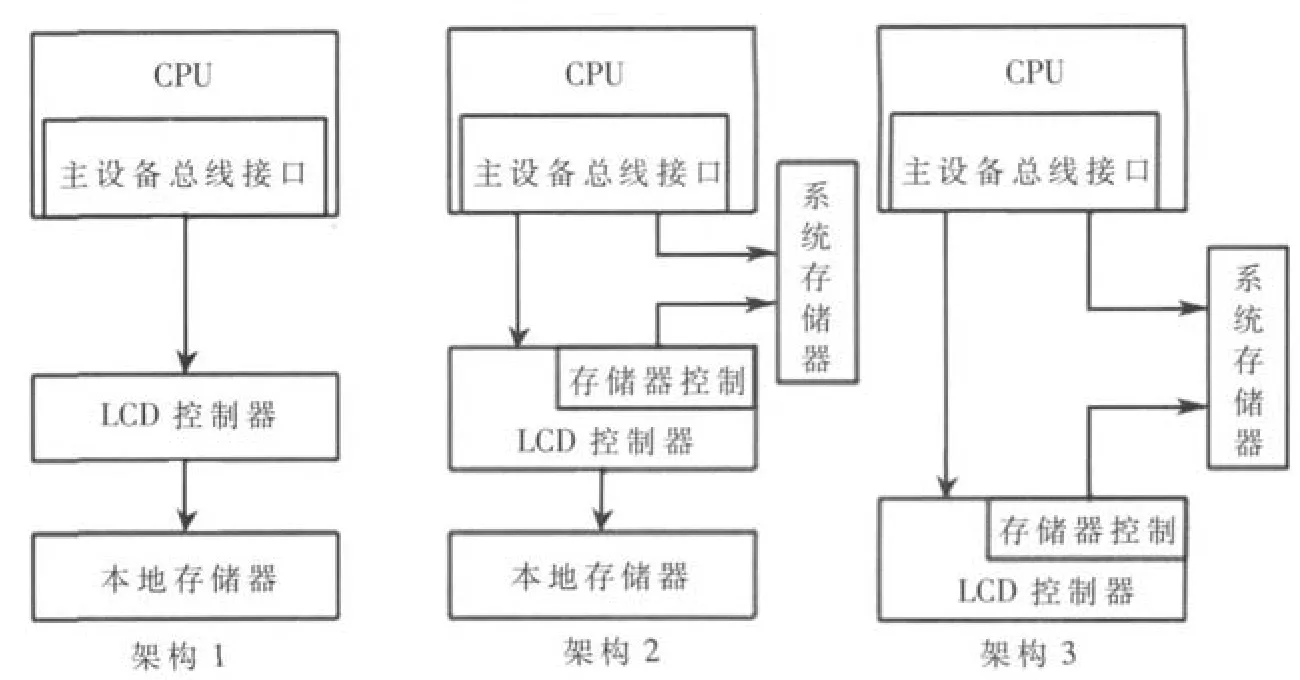

根据嵌入式处理器的工作原理,有三种架构形式可以实现LCD控制器的设计[3],如图1所示。架构2和架构3采用了与CPU共用显示存储器的方式,在显示过程中,CPU和LCD控制器需要间断地释放对共用存储器的访问,以完成刷新数据和更新数据在存储器中的交互。这两种架构中,CUP对存储器的访问会直接影响到显示数据的更新及LCD显示器的显示效果。尽管架构2增加了本地存储器,提高了系统性能,但是同样受到架构模式的制约。而架构1避免了共用显示存储器的模式,将LCD控制器作为总线上的一个外设,CPU将需要更新显示的数据通过存储器接口发送给总线上的LCD控制器,LCD控制器控制LCD显示。本文系统即采用了架构1形式的架构。

图1 系统架构图

1.2 系统硬件设计

基于架构1设计了图2所示的硬件结构。整个系统以FPGA对更新数据和刷新数据的仲裁处理为核心,配合SDRAM的操作及显示数据的传输标准转换(LVDS转换)完成其大屏幕显示器驱动的任务,实现显示功能。LVDS转换芯片与外围LCD屏幕连接,将FPGA产生的RGB等信号转换成高速差分串行输出信号。LCD显示器接口如图4所示。

图2 LCD控制器硬件结构图

XC6SLX45是XILINX公司新推出的一款FPGA,属于SPARTAN6系列,具有很高的性价比优势。利用FPGA配置灵活的特点,在硬件方面FPGA主要实现四个接口:CPU接口、SDRAM接口、FPGA配置接口和LCD接口。其中,SDRAM接口[4]和LCD接口都是常用的标准接口,这里不再赘述。FPGA的配置接口用于对FPGA的被动串行配置,采用FPGA的这种配置方式可以很好地提高该控制器的可移植性,又可以节省FPGA的配置芯片的成本。LCD控制器通过CPU接口连接到AMBA总线上[5],并以存储器的方式被嵌入式处理器访问。

HY57V283220是一款32 bit数据总线宽度的SDRAM,采用32 bit的数据总线能够很好地提高本控制器的数据处理速度和其驱动能力。DS90C38是一款通用的大屏幕LCD显示器LVDS接口转换芯片,可以适用于大部分差分接口的LCD显示器,设计中,可以很好地将FPGA产生的RGB格式的数据转换成高速串行差分数据格式。

1.3 硬件接口电路设计

控制器与CPU的接口是ARM的存储器访问接口,接口采用异步通信方式并由26 bit地址线、32 bit数据总线接入读写片选线组成,其接入接口硬件图如图3所示。

显示屏接口采用标准的大屏幕LVDS接口,通过

图4 LCD显示器接口

2 FPGA软件设计

FPGA软件模块及功能示意图如图5所示,其软件设计分为4个模块:(1)DCM时钟管理模块。主要功能是利用FPGA内部DCM产生其他模块所需的时钟;(2)接收模块。主要用来接收CPU发送来的需要更新的显示数据,作适当处理后进行数据缓存;(3)显存管理模块。主要用来解决CPU写入数据和LCD显示器读出数据之间的冲突;(4)LCD驱动模块。主要用于产生LCD显示器需要的时序。

图5 FPGA软件模块划分及功能示意图

2.1 接收模块

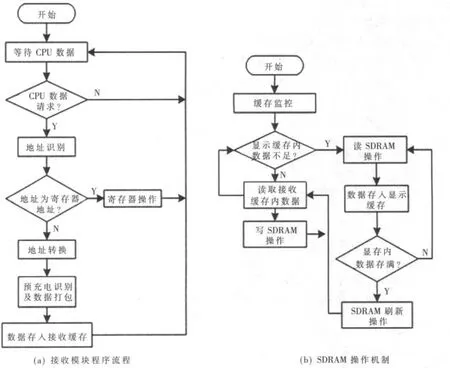

接收模块的程序流程图如图6(a)所示。系统上电复位后,接收模块进入等待接收数据状态,当有来自CPU的数据请求时,接收模块通过CPU接口通信协议接收数据,数据包括显示数据和存储地址。接收数据后,首先对地址进行译码。地址分为显示数据地址和寄存器地址:当地址为寄存器地址时,接收数据对寄存器进行操作,用来对LCD屏的属性进行配置和控制,以增强LCD控制器对不同LCD屏的兼容性;当地址为数据地址时,将CPU传递的线性地址译码为SDRAM写入操作的bank地址、行地址和列地址。地址译码后,将地址和数据进行封包组帧,并且加入自动预充电标志位,以提高SDRAM的写入数据速度。判断预充电标志位是否有效的依据是:数据地址是SDRAM的“行末”地址、后一个数据不与当前数据的行地址相同,然后将封号帧的数据依次传入接收缓存(FIFO)中,等待显存管理模块的读取。数据的帧格式如表1所示。

表1 数据帧格式

2.2 显存管理模块

显存管理模块分为:SDRAM接口模块和SDRAM控制模块。SDRAM接口模块根据SDRAM的操作时序建立SDRAM访问接口;SDRAM控制模块仲裁CPU的显示更新数据和LCD的显示刷新数据在SDRAM中的读写操作,其操作机制如图6(b)所示。系统上电复位后进入监控状态,然后进入SDRAM读操作状态,将LCD显示缓存中存入一定量的显示数据后,管理模块进行N次的SDRAM刷新操作,刷新结束后显存管理模块将一直监视接收缓存,直到显示缓存中数据不足时则循环进行读操作。

SDRAM是动态存储器,合理的操作机制可以提高SDRAM的读写速度。本控制器在SDRAM的操作上引入了如下机制以提高系统的性能:

(1)读写操作分开独立连续进行:将SDRAM中数据连续读出固定个数的数据,然后进入连续写入状态。

(2)连续两个数据不同行时,采用自动预充电读写操作,同行则不进行预充电操作。

(3)在空闲状态进行手动刷新SDRAM,

本系统的读操作是周期进行的,在每次读操作后进行固定周期数的刷新操作,既保证了刷新次数,又节省了刷新时间。

(4)采用32 bit的SDRAM,以增加位宽换取速度。

2.3 LCD驱动模块

该模块根据LCD标准的时序要求产生行时钟、场时钟和数据使能信号,并且配合像素时钟将LCD显示缓存中的32 bit数据以16 bit读出。

图6 主要软件模块程序流图

3 实验验证

本设计采用的SDRAM的工作时钟为133 MHz,为了减少异步时钟造成的问题,FPGA的系统工作时钟也采用了相同频率的工作时钟,并且成功地应用于某船载导航雷达的现实界面的实现上。在雷达图像显示中,ARM与LCD控制器之间的数据量为30 MB/s,屏幕采用了日立公司TMS150XG1-10TB型号的TFT-LCD显示器,LCD屏幕的分辨率为1 024×768,像素时钟为65 MHz。实验结果证明,LCD控制器的工作性能良好,屏幕显示清晰稳定。利用chipscope抽取主要的数据如图7所示。抽取结果显示,接收到的ARM数据经过组帧最后正确地产生了用于显示的数据。

图7 关键信号抽取图

本文介绍了新型高分辨率LCD控制器,解决了大屏幕显示所需的高刷新率和高更新率问题。同时,多个内部寄存器使其支持各种型号的LCD显示器,并已成功地驱动了15英寸的LCD显示器。

[1]ELECTRONICS S.S3C2440A 32-bit CMOS microcontroller user′s manual(R).2004.

[2]王顺利,戴明,孙丽娜.基于FPGA的一种新型8通道数据采集系统[J].电子技术应用,2009,35(11).

[3]MOTION S.SM502 mobile multimedia companion chip Databook(R).2006.

[4]李卫,王杉,魏急波.SDRAM控制器的FPGA设计与实现[J].电子工程师,2004,30(10).

[5]曹志香,桑爱兵,丁黄胜,等.基于AMBA总线的嵌入式彩色LCD控制器的设计及FPGA实现[J].电子器件,2004,27(1).