无铅电子元器件的锡须风险评估与对策分析

2011-03-20聂国健郑敏贵周军连

聂国健,郑敏贵,周军连

(工业和信息化部电子第五研究所,广东 广州 510610)

1 引言

随着环境保护意识的不断提高,执行可持续发展战略,开展环保设计,实施绿色制造等成为当今社会发展的主题。自欧盟的环保指令发布以后,有毒有害物质在电子产品的生产过程中被限制使用,电子元器件逐渐由传统的有铅转变为无铅。无铅电子元器件已在全球商业和军事市场获得了全面应用,但随之也带来了新的可靠性问题,最为典型的就是 “锡须 (tin whiskers)” 现象。

锡须是电子电路板上的一种常见现象,它是从锡金属表面自然生长出来的发丝状晶须。锡须生长会连接相邻电路,导致短路故障。传统的防范锡须生长的方法是在覆盖材料和焊锡中加入铅,以抑制锡的生长。而无铅电子元器件正因为限制使用铅材料,使得锡须现象更为突出,与之相关的可靠性问题也备受关注。

本文就无铅电子元器件的锡须现象进行机理分析,并探讨了风险评估的方法以及防范和减缓措施。

2 锡须的产生机理

锡、镉、锌、锑、铟是晶须生长的常见金属,铅、铁、银、金、镍则很少。一般而言,锡须现象易出现在相对软和延展性好的材料上,特别是低熔点金属。

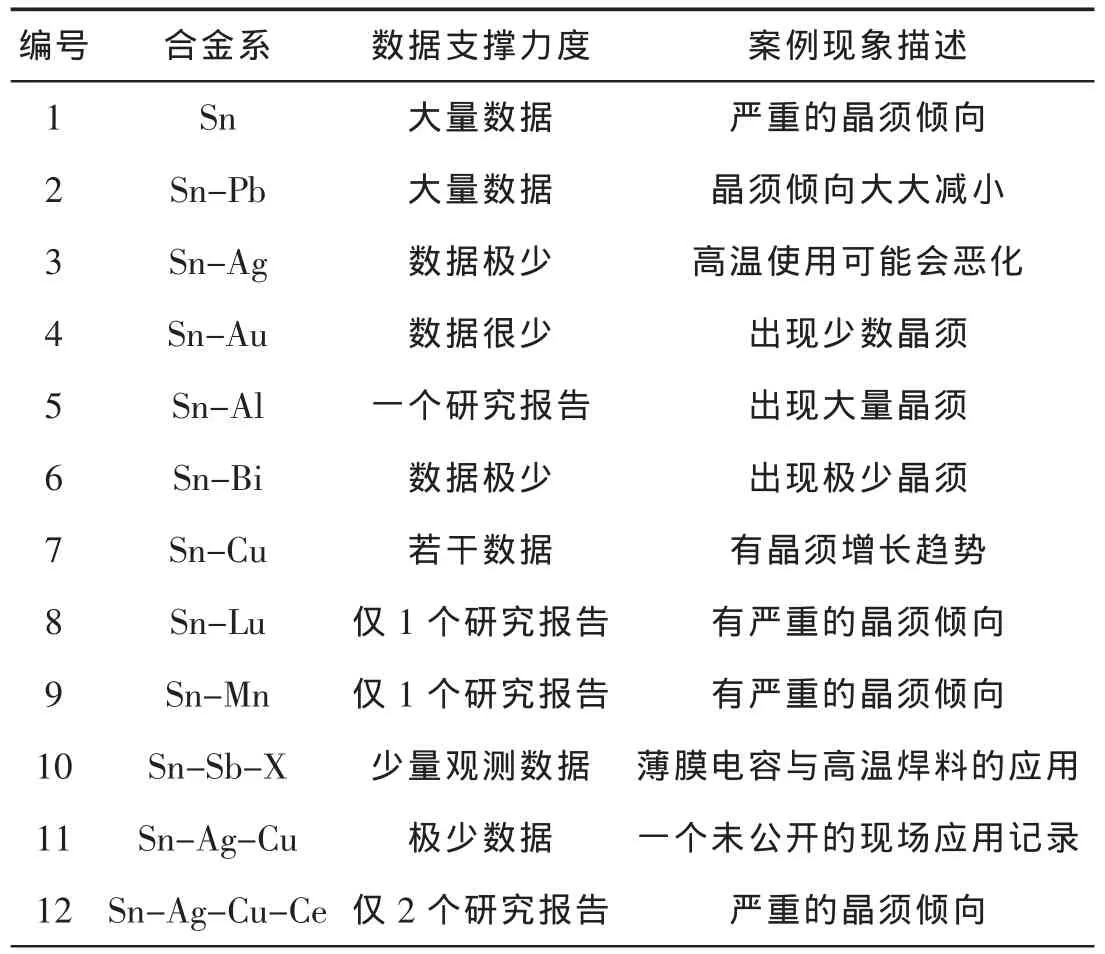

锡须是一种单晶体结构的导电体,形成于金属镀层的表面,其形貌和尺寸随锡合金组分的不同而不同,一般有直线型、扭曲型、沟状型和交叉状型等。不同锡合金的晶须现象及其典型图例如表1和图1所示。

表1 Sn-X合金的晶须案例

图1 Sn-X合金晶须的SEM图

国内外学者通过大量的实验研究,提出了如下几种锡须生长机制:

a)重结晶机制

该机制认为晶须的形成和生长是从重结晶的晶粒上生长出来的。Glazunova和Kudryavtsev[1]用镀层热处理后的晶粒生长被抑制的现象证明镀层晶粒的再结晶对晶须生长有重要的影响作用。Kakeshita[2]等发现细晶粒Sn镀层中的位错环数量比粗晶粒Sn镀层中多,并据此推测晶须是在再结晶晶粒上长出来的。

b)氧化层破裂机制

该机制认为锡原子趋向于从高应力区运动向低应力区,从而形成晶须生长的压应力梯度。晶须从表面氧化层薄弱的破裂处长出,局部压应力得到释放。例如:Cu6Sn5金属间化合物 (IMC)的形成,是Cu/Sn镀层结构中晶须生长的内部压应力。当表面锡氧化物存在缺陷或裂隙时,在内部应力的作用下,锡被挤压出而形成锡须。

c)位错运动机制

该机制认为扩散运动产生的位错是晶须生长的源头。晶须邻近区域的表面的氧化过程而产生反向表面张力,降低表面自由能,为其生长提供驱动力。有研究得出这样的结论:晶须轴与位错的柏氏矢量平行。有学者则提出了晶须形成和生长的螺旋位错模型,每个到达表面的完整位错环都使表面增加一个柏氏矢量的厚度。

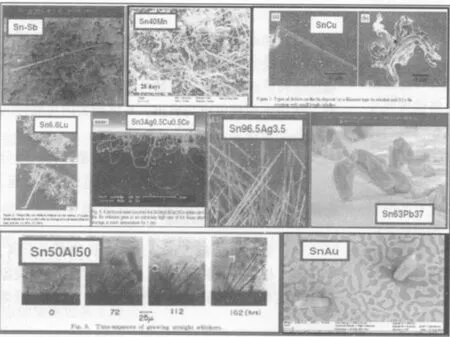

基于上述机制,内部应力是锡须形成和生长的主要驱动力,其机理如图2所示。

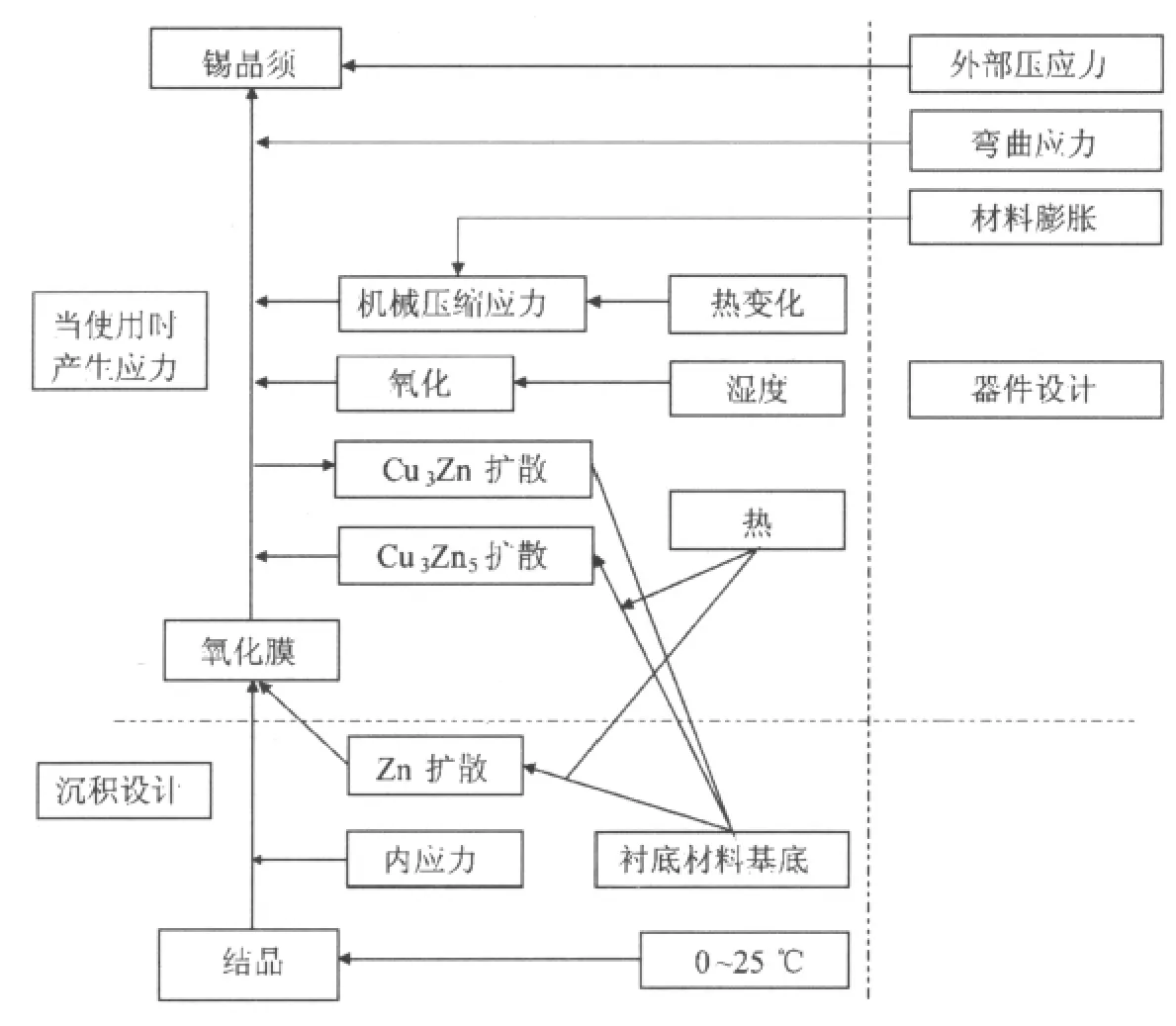

因此,电子元器件金属镀层表面锡须的形成原因与其制备工艺和使用过程密不可分。任意缺陷的引入或局部内应力的形成,都可能成为锡须生长的潜在诱因。与锡须生长有关的潜在因素包括:镀层的电镀化学工艺、镀层特性、基片特性、外部应力、组装工艺以及存储环境条件 (见图3)。其中,电镀条件、镀层厚度、基体材料、晶粒结构以及存储环境条件尤为敏感,对锡须的生长速率具有决定作用。

图2 锡须生长机理

图3 锡须形成因素

3 锡须风险分析

锡须是一种导电金属,电子元器件中锡须的生长容易形成潜在通路,引发电气故障。综合而言,锡须生长引起的潜在风险主要表现为以下几个方面:

a)永久性短路

当锡须长到足以桥接两个不同的导体,并且在低电压、高阻抗电路中电流不足以熔断锡须时,便形成了永久性的短路。当锡须的直径较大时,这种现象较为常见。

b)短暂性短路

当锡须直径较小时,通过的短路电流超过其所能承受的电流 (一般为30 mA),锡须将被熔断,形成间断的短路脉冲,这种情况一般较难被发现。

c)残屑污染

当器件受到机械冲击或震动时,可能造成锡须从镀层表面脱落,形成残屑。一旦这些残屑导电物质颗粒自由运动,将会干扰敏感的光信号或微机电系统(MEMS)的正常运行。此外,残屑也可能造成桥接短路。

d)真空金属蒸汽电弧

在真空 (或低气压)条件下,当锡须传送较大的电流 (几个安培)或电压 (大于12 V)时,锡须将蒸发成离子而产生电弧放电,传送电流可高达200 A。电弧依靠镀层表面的锡来维持,直到消耗完毕或停止电流输入为止。这种现象容易发生在保险管等器件内或线路断开时,曾有一商业卫星因发生此类问题而导致卫星偏离轨道。

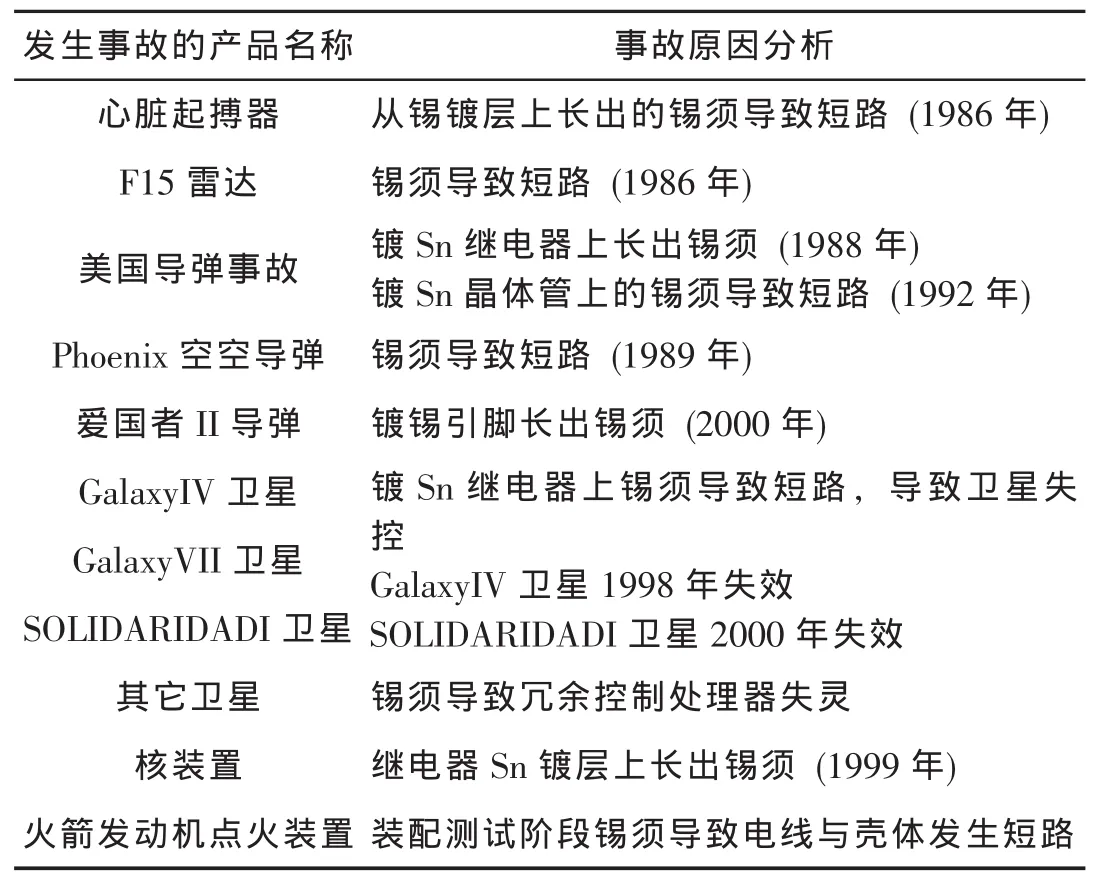

随着电子产品的小型化和高密度集成化,电子元器件的引脚间距越来越小,锡须故障率将越来越高,晶须风险成本也将进一步扩大,特别是在高可靠性要求的应用领域,如:医疗、军事和航天航空等,风险代价将更加昂贵。表2是部分典型高风险代价的锡须事故例子。

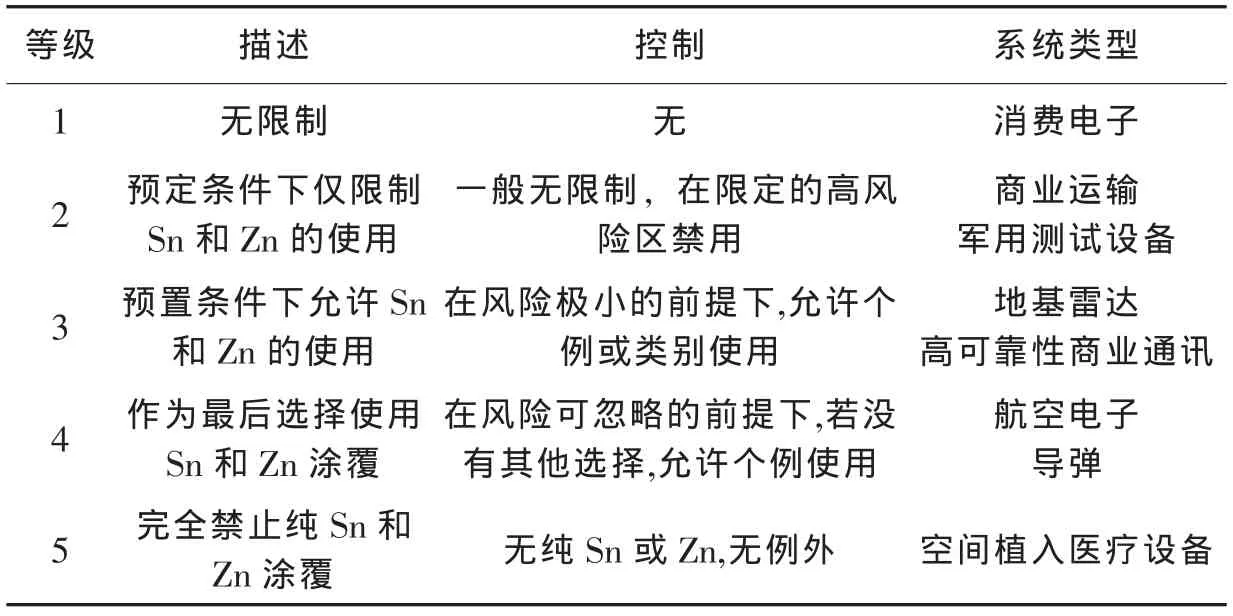

考虑到电子设备系统成本和任务关键性程度的不同,Pinsky和Lambert[3]提出了锡须生长的等级划分准则,以区分不同应用类型的锡使用要求,供电子设备制造商或使用者参考选用。划分准则总共包括5个容忍等级,典型的应用系统类型如表3所示。

表2 典型的高风险锡须事故

表3 锡须容忍等级划分

4 锡须风险对策

在无铅电子产品中,锡须风险所带来的损失具有不可预测性,使得锡须的生长控制与风险防范变得尤为重要。总体而言,应对锡须风险的策略应包括研制阶段的技术预防和使用阶段的管理控制两个方面。

从锡须形成机理方面考虑,研制阶段抑制锡须生长的技术途径包括:

a)引入阻挡层

当使用的基体材料为黄铜时,会加速锡须的生长,同时锡与基体材料形成的IMC也会加速锡须的生长。因此,在使用纯锡镀层时使用镍作为下镀层 (阻挡层),可有效地阻止铜向纯锡镀层扩散,消除内应力,预防锡须生成。

b)采用 “暗锡”镀层

研究表明,晶粒越小越有利于锡须生长。暗锡镀层的晶粒尺寸比亮锡更大,一般大于1 μm,镀层的内应力更小,锡须生长的几率也就更低。

c)使用较厚的纯锡镀层

研究报告表明,纯锡镀层越厚,锡须生长的几率越低,一般要求达到10 μm以上,但厚度的增加会增加器件成本。

d)采用热浸镀层

热浸镀层的内部应力较小,可减缓锡须生长。

e)加镀保护层

采用聚合物等在纯锡镀层表面制作共形保护层,抑制锡须生长。

f)进行退火处理

将纯锡镀层进行回流熔化或烘烤处理 (在惰性气体中),释放其内部应力,可减缓锡须生长。

g)防止镀层在空气中暴露

空气中的潮气以及氧气的氧化作用,都是锡须生长的助长因素,尽可能地减少空气中的曝晒,有利于减缓锡须生长。

h)防止机械冲击或刮擦

外界机械冲击或刮擦均会在镀层表面形成薄弱区域,在内应力的作用下,锡须便易以从这些薄弱区域中生长出来。

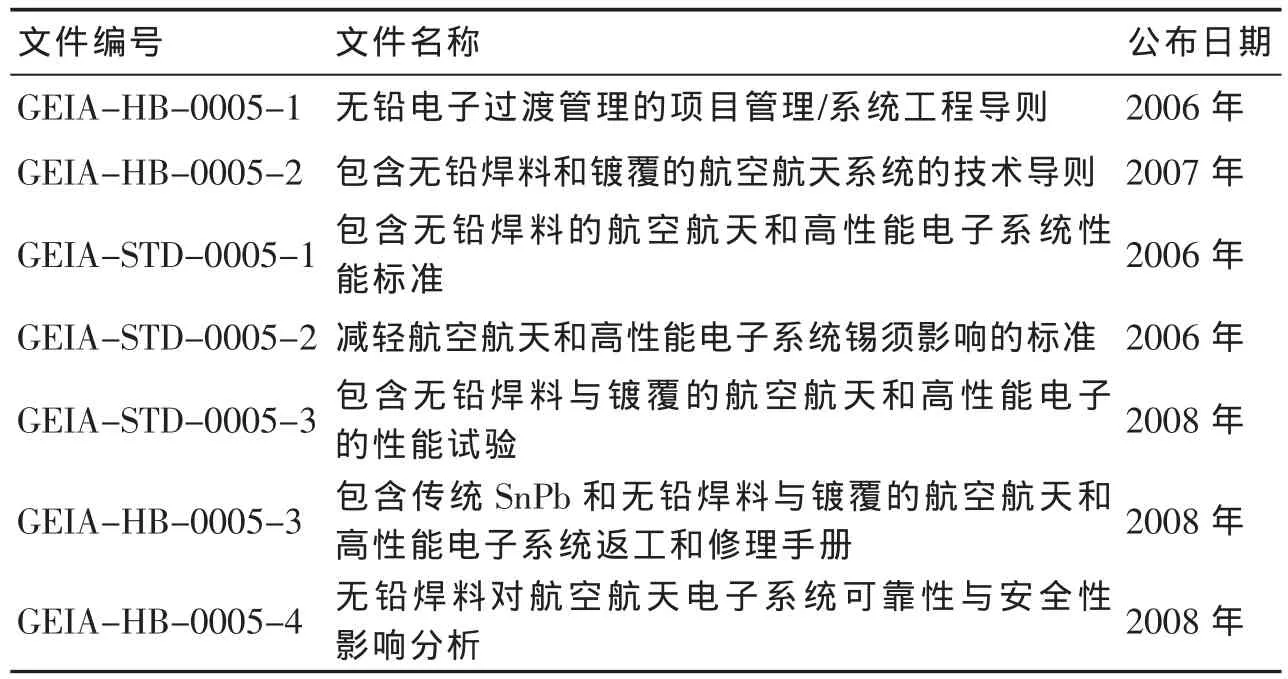

目前国际上针对电子元器件无铅技术应用的指导文件主要是政府电子与信息技术学会GEIA 0005系列标准,详细介绍如表4所示。

表4 GEIA 0005系列标准

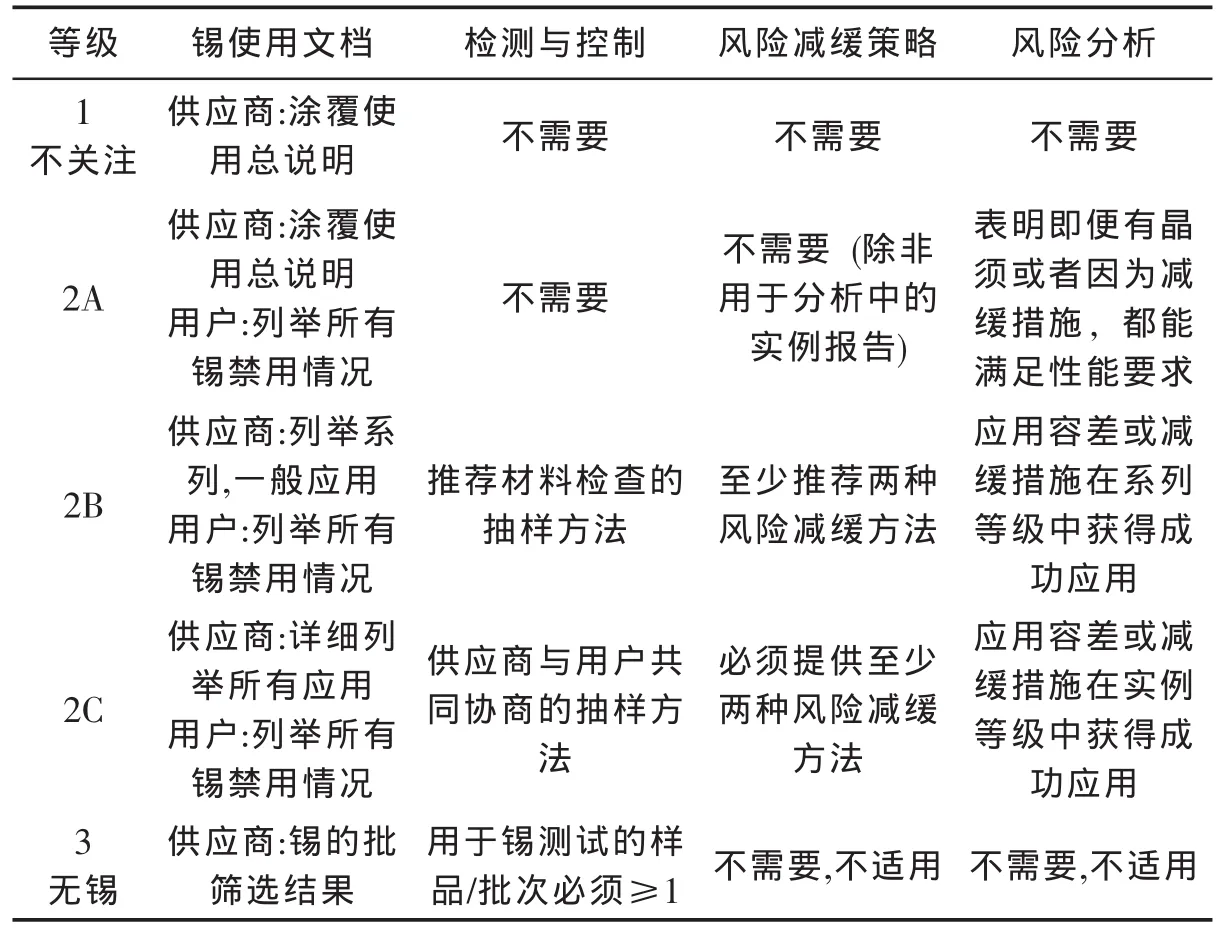

其中,GEIA-STD-0005-2规定了航天航空和高性能电子系统的锡控制等级[4],同时限定相应的检测控制和风险减缓要求。比如,对于2C等级的锡使用,供应商与用户双方需共同协商执行抽样检查,并且至少必须提供两种有效的风险减缓措施,如表5所示。

表5 GEIA-STD-0005-2锡控制等级要求

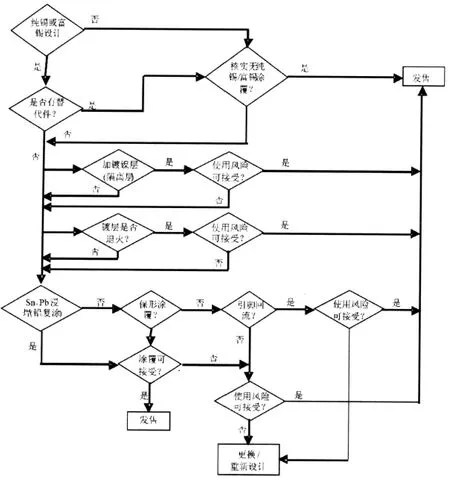

图4 锡须风险控制流程

风险减缓策略并不能完全消除或者从实质上阻止锡须生长。事实上,对于SnPb涂覆的器件同样有锡须生长的文献报道,只是发生的概率很低。此外,对于不同的应用对象,实施的风险减缓策略也会不尽相同。由于锡须生长现象不可避免,提前预防,加强管理控制尤为重要。为此,Osterman[5]等人提出了锡须风险减缓控制程序,为设备制造商锡须风险管理控制提供指导依据,如图4所示。该控制流程同样适用于高风险领域的使用管理控制,是军用、航天航空领域无铅应用风险规避的有效方法。

5 结束语

全球电子产品的全面无铅化,使锡须风险问题成为厂商和用户重点关注的难题。特别是在高质量、高可靠性要求的应用领域,锡须的风险问题更为严重。就目前情况而言,锡须生长现象固然不可彻底消除,但是,通过合理的管理控制和正确的技术应用,在减缓锡须生长、延长产品使用寿命方面依然可以获得较高的成效。然而,对于高风险成本的航空、航天、军用领域,加强无铅电子元器件使用控制仍是第一选择,要真正实现无铅技术在该领域的高可靠应用依旧任重道远。

[1] GLAZUNOVAV K,KUDRYAVTSEVN T.An investigation of the conditions of spontaneous growth of filiform crystals on electrodeposit coatings[J].Translated from Zhurnal Prikladnoi,1963,36(3):543-550.

[2] KAKESHITA T, KAWANAKA R,HASEGAWA T.Grain size effect of electroplated tin coatings on whisker growth [J].Journal of Material Science,1982,17(9):2560-2566.

[3] GEIA-STD-0005-2-2006,Standard for mitigating the effectsoftin whiskerin aerospace and high performance electronic systems[S].

[4]PINSKY D,LAMBERT E.Tin whisker risk mitigation for high-reliability systems integrators and designers [R].Tewksbury:Technical Report of Raytheon,2004.

[5] OSTERMAN,M.Mitigation strategies for tin whiskers[R].Maryland:White Paper of CALCE EPSC,Release 1.0,2002.