基于ADF4106的锁相环设计

2011-03-16丁新强秦开宇韩尧

丁新强,秦开宇,韩尧

(电子科技大学空天科学技术研究院,成都611731)

0 引言

在各种现代通信系统中,频率合成所需要的高稳定度,高纯度,低相噪的频率源是至关重要的。目前频率源大部分都是利用锁相环来实现的,锁相环频率合成具有高稳定和高精度的性能,而且成本低,功耗低。本设计利用锁相环原理,实现了在3.6GHz高稳定度、高质量的频率信号。

1 系统总体设计

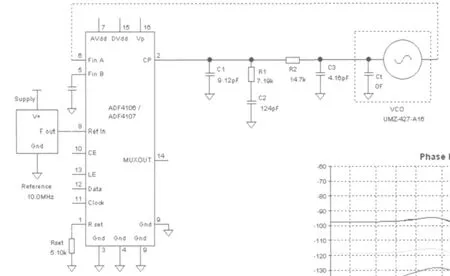

系统原理图如图1所示,主要由晶体振荡器(10MHz)、鉴相器(ADF4106)、环路滤波器和VCO(UMZ-427-A16)组成。VCO的频率范围在3550MHz-3630MHz,经过ADF4106内部的分频器进行360分频,分频器输出10MHz左右的信号与10MHz参考信号进行鉴相,鉴相后的相位误差通过环路滤波器滤除高频杂波后,控制VCO频率输出,最终使频率精确的锁定在3.6GHz。

图1 系统原理图

2 关键器件的选取

2.1 振荡器的选择

压控振荡器是锁相环频率合成器的关键器件,其本身的性能指标对频率合成器性能的影响极大。系统对输出射频信号的的相噪指标是≤-95dBc/Hz@20kHz,因此要求VCO的相噪指标在同等条件下要优于-105dBc/Hz。而UMC公司的型号为UMZ-427-A16的VCO相噪典型值在频偏10KHz时就达到了-105dBc/Hz,相噪指标满足要求,且3.6GHz近似在其输出频段的中心位置,线性度较好,故选用之。

2.2 环路滤波器的选择

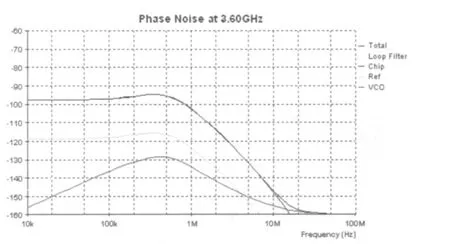

为了获得较好的相噪指标,本设计采用无源低通滤波器,因为无源滤波器不含有源器件,引入的噪声较有源滤波器更少些。滤波器的参数经过软件ADIsimPLL3.0的多次仿真,并与实际电路调试相结合,得到一组最佳参数,使环路处于最佳工作状态。如图2所示,本设计采用的是三阶低通RC滤波器:

图2 三阶低通RC滤波器

闭环相位噪声的仿真图如图3所示,可以看出总体相位噪声在-95dB/ Hz以下。

图3 闭环相位噪声仿真图

2.3 鉴相器的工作方式

本设计选择ADF4106作为鉴相器,它主要由以下几部分构成:低噪声数字鉴相鉴频器(PFD)、高精度且可编程设置电流的电荷泵、可编程参考分频器R和可编程计数器A和B、双模前置分频及测试信号输出多路选择器等。由于鉴相器芯片内部集成有可编程分频器,因此不需要外部可编程分频器,简化了电路设计,同时也节省了电路板空间。芯片有一个三线控制接口可直接与控制器相连,可由控制器通过此接口修改芯片内部的相应寄存器,实现芯片内参数变量值的修改。程序设计简单可靠,且还可编程多路选择器将芯片内部的信号引出到芯片外部,方便电路调试。芯片功能原理图如图4所示。

3 测试效果及分析

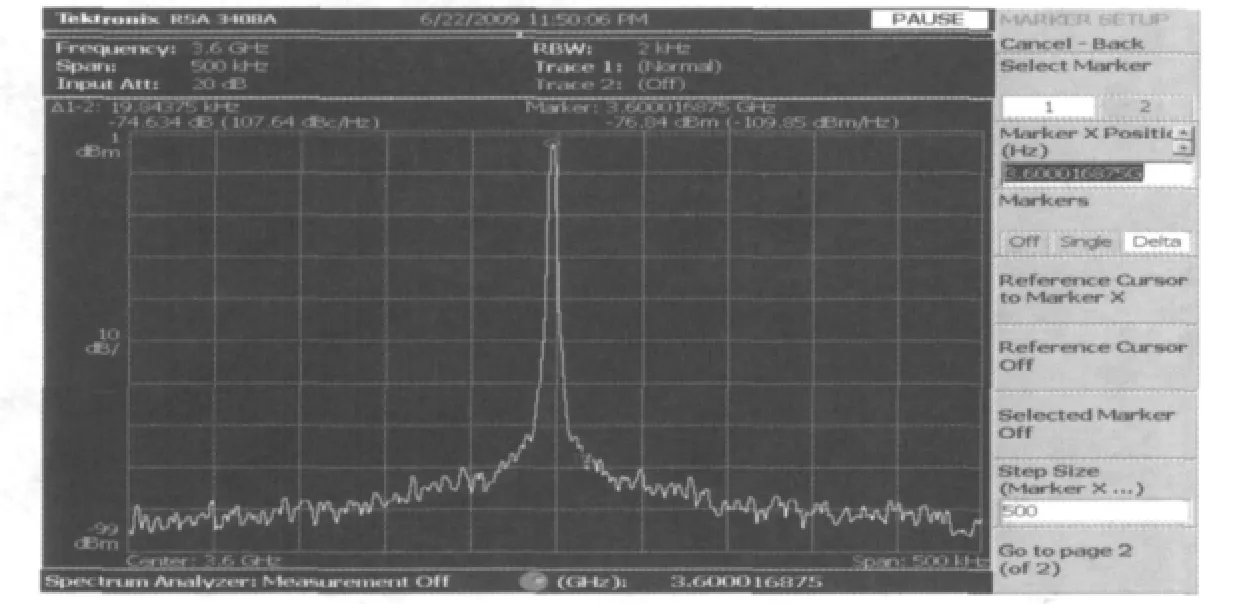

用谱仪对VCO输出频率进行测试,测试结果如图5所示,频率无杂散、稳定性好,相噪在频偏20kHz处达到-107dB/Hz,优于预期仿真效果,满足了整机系统对本模块的要求。

图4 ADF4106 功能原理图

图5 3.6GHz频谱测试图

4 结束语

本文利用锁相环基本原理,实现了基于ADF4106的锁相环频率合成,该方案的优点是频率杂散小,相噪低,稳定性好,经过实际测试,结果显示频率精度高,无杂散,相噪指标优于系统整机要求。

[1] 郑继万,万心平,张厥盛.锁相环路原理与应用[M].北京:人民邮电出版社,1984:14-15.

[2] 远坂俊昭. 锁相环(PLL)电路设计与应用[M].北京:科学出版社,2006:51-80.

[3] 黄智伟.锁相环与频率合成器电路设计[M]. 西安:西安电子科技大学出版社, 2008:6-31.

[4] 王家礼,孙璐. 频率合成技术[M]. 西安:西安电子科技大学出版社, 2009:5-10.

[5] Roland E.Best.锁相环设 计、仿 真与应用[M].北京:清华大学出版社,2003:115-145.

[6] William F. Egan.Phase-Lock Basics[M]. John Wiley & Sons,Inc,2008:1-3.

[7] Amit Mehrotra, Noise Analysis of Phase-Locked Loops[J]. IEEE Trans. Cir. and Sys. I, 2002, 49:1309-1316.

[8] Floyd M. Gardner. Phaselock Techniques[J]. Wiley-Interscience,2005,103-117.