基于多模组3G视频传输终端的硬件设计与仿真

2011-03-15刘晓春胡东平简毅彬

刘晓春,胡东平,简毅彬

(1.长安大学 信息工程学院,陕西 西安 710061;2.中兴通迅股份有限公司西安研究所,陕西 西安 710065;3.陕西电信西安分公司,陕西 西安 710082)

0 引言

随着中国3G技术的大规模商业化应用,在视频监控行业中,3G技术已经成为目前无线视频监控的最佳方案。依托3G无线通信网络,通过集成视音频压缩、流媒体管理、数据传输等技术,以无线传输方式攻克了目前固定式监控方式中线路设施投资大、不易更改设备位置以及现有移动监控设备需通过大存储器定期转存数据的3大难题[1-2]。但是,由于中国通信3G网络建设的原因,存在一些客观问题,主要表现在城乡之间网络信号覆盖不均衡,信道传输带宽分配不均衡,数据信号传输带宽不够理想[3]。特别是在偏远地区,存在3G视频监控信号在传输中由于信道带宽不够,导致视频图像不流畅,质量差等现象。笔者针对3G无线视频传输在监控行业中出现的一些缺陷,设计了一种基于S3C2440为核心的,通过USB硬件扩展方式实现的多模组3G无线视频传输终端硬件平台,在该硬件平台上结合相应的算法和系统软件,可以很好地解决3G无线视频监控信号传输质量问题。

1 系统硬件方案设计

1.1 系统方案及工作原理

笔者设计的多模组3G无线视频传输终端系统,主要由CPU小系统、前端视频采集单元和USB扩展小系统、以太接口和3G无线通信模块等构成,如图1所示。

系统基本工作原理是:前端视频采集模块将采集到的视频信息经过压缩、编解码后送给CPU小系统进行处理,根据设计需求CPU小系统主要对前端采集的信号按照一定的算法协议对信息包分割成片,分别送给多个3G无线发射模块进行多信道的无线传输,如在视频接收端(视频服务器端)。根据相应的算法协议,对分片的信号进行恢复,形成源端的视频信号数据包,从而提高信号的传输带宽,增加实时图像的传输质量。系统中,以太网口是联系本系统和上位机的关键接口,通过以太接口上位可以对3G无线传输终端进行管理与控制。

1.2 前端视频采集传输总线的设计

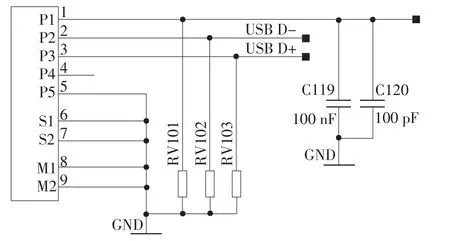

系统中的前端采集单元主要实现视频数据采集,并进行编解码。前端视频采集和处理单元与CPU模块之间用USB接口通信(接口类型主要由前端模块来确定)。硬件设计必须考虑接口设计稳健性,能保证数据可靠传送,以及接口在经常插拔过程中保持连接的可靠性,系统电路如图2所示。

图2 USB信号传输接口电路设计

电路中RV102,RV103最好选取小电容类型的压敏电阻器,可以有效实现电路的EMC防护。可以参考AMOTECH公司的ALVC18S02003,或者EPCOS公司的B72590T7900V60。设计USB接口电路,最大提供电流不超过500 mA。

1.3 CPU小系统设计

1.3.1 CPU芯片的选型

CPU小系统模块是本系统的核心模块。CPU芯片的选型是关键,总体原则是:尽量考虑低功耗,高速率的内部数据处理能力,足够的总线带宽处理实时视频信号以及系统有较强的抗干扰能力。

三星公司的S3C2440芯片能比较好地满足系统的设计需要,S3C2440是基于ARM9内核ARM920T的一款低功耗的SoC芯片,典型主频为400 MHz,0.13 μm的CMOS工艺标准单元和存储单元复合体。并且采用了新的总线构架(AMBA),其内核为32 bit的先进处理器。提供的主要接口有:2路USB Host接口和1路设备USB接口;外部存储器控制接口单元;4路定时器;1路内部计数器和看门狗;RTC时间日志功能等功能接口。

1.3.2 CPU外围存储电路设计

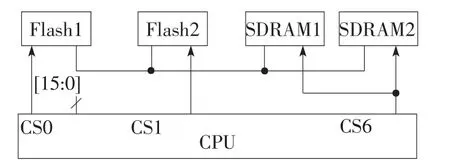

在CPU小系统设计中,CPU外部存储系统是关键点。本设计中所有的Memory芯片都通过Local Bus总线挂接到CPU上,Flash芯片在设计中使用2片,Flash1芯片用来存储ARM启动代码和系统文件,采用可靠性高、存储容量小的SST39VF1601芯片实现。Flash2采用存储容量大、成本低、可靠性相对比较低的S29GL128P11FFI010来实现。内存SDRAM芯片选用2片数据位宽16 bit的EM63A165TS-6G实现,存储容量256 Mbit的SDRAM存储器并联使用,构成32 bit位宽的外部存储总线。系统设计中将总线时钟位置为166 MHz。那么内存的总线带宽为(166×32/8)Mbyte/s=664 Mbyte/s,可以满足系统的要求。如图3所示,CPU对不同芯片的片选信号的选择进行分时访问操作,设计的主要点为:

图3 CPU外部存储总线设计示意图

1)正确配置CPU芯片。硬件配置CPU的OM[1:0]的状态,在系统复位器件采用配置信息来决定系统从NOR Flash启动,还是从NAND Flash启动,本系统配置从NOR Flash启动。

2)正确选用总线控制片选CS。存储启动代码的Flash1选用CS0信号,SDRAM选用CS6或者CS7作为片选信号,Flash2可以选用CS2~CS5之间任何一个。

3)正确设计地址信号。由于Local Bus总线上各个芯片数据总线位宽不一致,CPU和芯片的地址互联不是直接一一对应关系,需要仔细考虑。

4)正确配置SDRAM控制控制信号。2片SDRAM芯片配置成总存储容量512 Mbyte的系统内存,单片SDRAM的Bank容量是64 Mbyte,故使用CPU的A[25:24]作为SDRAM的BANK选择信号,为保障时钟信号的完整性,有CPU独立提供时钟信号CLK1,CLK2。

1.3.3 CPU调试接口电路设计

由于CPU不直接提供MII/GMII等网络通信接口,笔者选用DM9000芯片作为以太网口的PHY芯片,即通过配置DM9000芯片使其通过LOCAL_BUS总线实现与CPU的通信。考虑到系统调试的方便同时设计RS-232串口,JTAG接口方便调试与数据的加载。同时必须注意,产品化以后,调试接口需要经常插拔,特别是网口需要增加防护电路,防护标准参考电信产品CLASS C标准进行设计。

1.4 CPU对3G无线通信模块控制与管理策略

系统设计中采用多个3G无线通信模块,最大支持4个模块,采用各个模块相互独立,通过CPU集中进行管理的设计思想。在视频监控行业中,采用多模组3G视频传输终端系统。在实际使用过程中不总是所有模组都同时工作,客户在使用该系统过程中将根据监控场景、资费情况的不同进行选择。同时还需要考虑到系统异常情况下的可恢复性问题,系统功耗与节能等问题。有必要利用CPU芯片丰富的I/O实现用户对3G模块进行控制和管理,使系统变得灵活可控。CPU与3G反射模块接口设计如图4所示。主要控制与管理策略有:

1)通过CPU的GPIO实现对3G模块的独立复位控制与管理;

2)通过CPU的GPIO实现对3G模块的无线射频功能进行使能控制与管理;

3)通过CPU的GPIO实现对3G模块的电源使能控制与管理;

4)通过CPU的GPIO实现对USB通信链路进行连接与关断控制与管理。

1.5 3G模块的接口外围电路设计

联通的WCDMA是国内3G移动通信的一种,具有技术成熟、带宽大等优点,笔者以华为WCDMA无线通信模块EM770W为例来说明3G无线通信模块外围接口电路的设计。

目前国内主要3G发射模块供应商都采用了USB物理接口,早期也采用UART接口,传输模块的基带信号。笔者采用USB HUB来桥接3G无线通信模块和CPU小系统,进行信号基带传输。USB HUB芯片采用TI2707芯片,扩展出7个USB口,笔者使用其中的4个USB口。

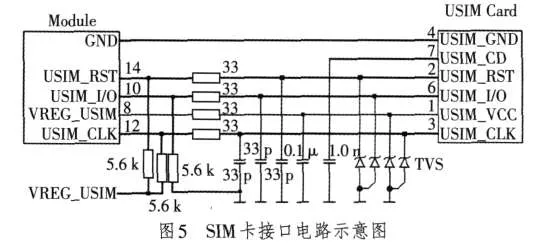

对于3G模块的外围电路设计中,SIM卡电路设计是关键。如图5所示,SIM卡接口速率典型值在3.25 MHz左右,因此USIM卡座应该距离模块接口较近的位置,避免因走线过长,使波形严重变形,从而影响信号的通信。USIM-CLK和USIM-I/O信号的走线需包地处理。

在USIM-VCC上加一个0.1 μF或0.22 μF的电容,其余的USIM-CLK,USIM-I/O,USIM-RESET上面对GND网络加33 pF电容,滤出天线信号的干扰。此外,4个信号都通过TVS管用来ESD防护。

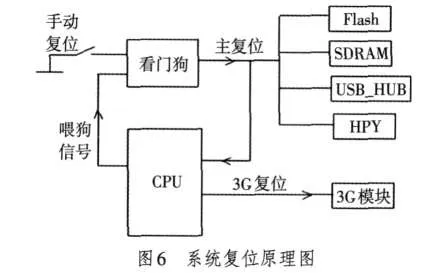

1.6 看门狗与系统复位电路的设计

硬件看门狗电路的应用能使使用稳健,设计硬件看门狗电路实现对CPU程序进行实时监控,如果出现程序异常后看门狗实时对系统进行复位,喂狗时间大于1 s小于2.25 s,典型1.6 s;复位脉宽满足负责芯片最低要求。其中多个3G无线通信模块的复位由CPU进行集中控制,也可以通过手动进行系统全局复位,复位脉冲宽度一般要求大于50 ms小于200 ms。系统复位方案如图6所示。

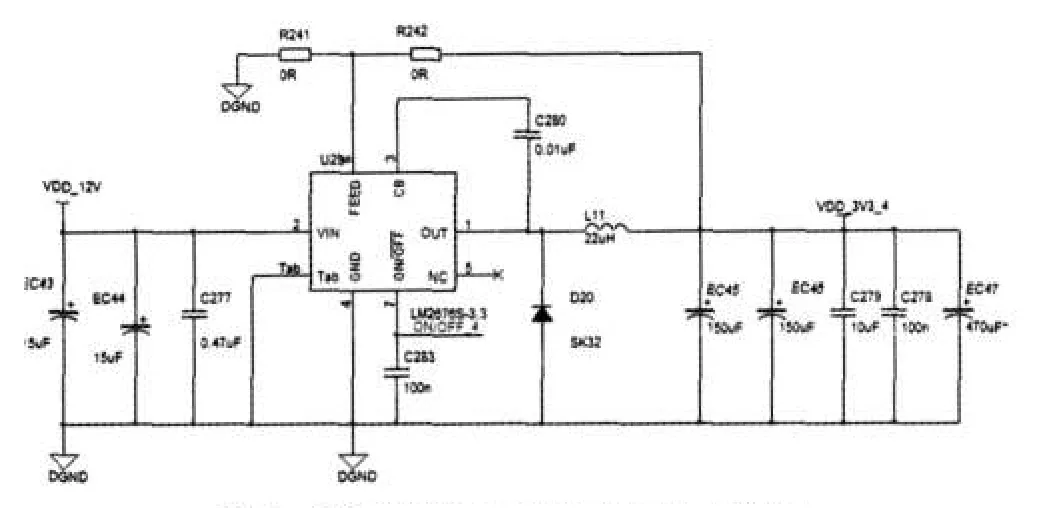

1.7 3G无线通信模块的电源电路设计

国内主流3G无线通信模块外部输入电压规格为3.0~3.6 V,典型值为3.3 V。实验表明在网络信号很弱时,3G天线通信模块会加大功率发射,模块的瞬态电流会有1.6~2.7 A不等。所以推荐使用1.6 A以上的LDO或开关电源。此外必须考虑到大功率发射时到能导致的电压跌落,在模块的电源端口处加上一个较大的超级电容,尽量添加220 μF以上的大电解电容。多模组同时工作需要仔细考虑系统整体功耗问题,有必须进行降额处理,增加系统的可靠性。详细设计电路如图7所示,其中,CPU通过ON/OFF信号实现对电源模块的控制与管理,在模块不工作时,通过CPU关断其工作电源节省空耗。

2 关键信号的信号完整性问题

2.1 高速数字系统与信号完整性

信号完整性问题已经成为硬件设计中不可回避的一个问题,处理好SI问题是硬件工程师必须面对的挑战[4]。在本系统中,主要的考虑SI敏感关键型号分别有CPU与SDRAM之间的高速总线、USB传输信号线、全局复位信号RST信号、高速芯片电源去耦等关键因素。影响这些信号的SI问题的主要因素有阻抗不连续、多负载总线的拓扑结构选择不合理、布局布线等因素。在硬件具体设计中,借助于业界优秀的仿真软件Candence对关键型号进行前/后仿真。考虑到仿真时间成本、人力成本与仿真信号的重要程度之间的平衡。下面对本系统非常关键的几组信号选取代表性的信号进行仿真设计。

图7 3G模块电源供电原理图(截图)

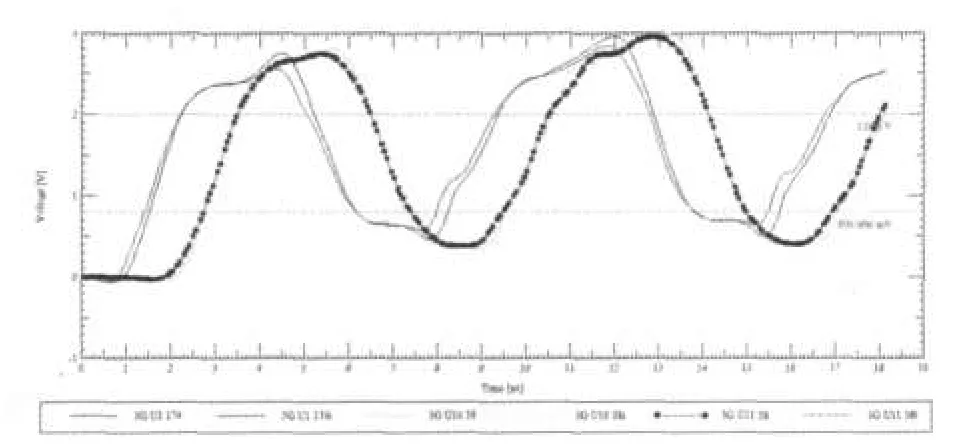

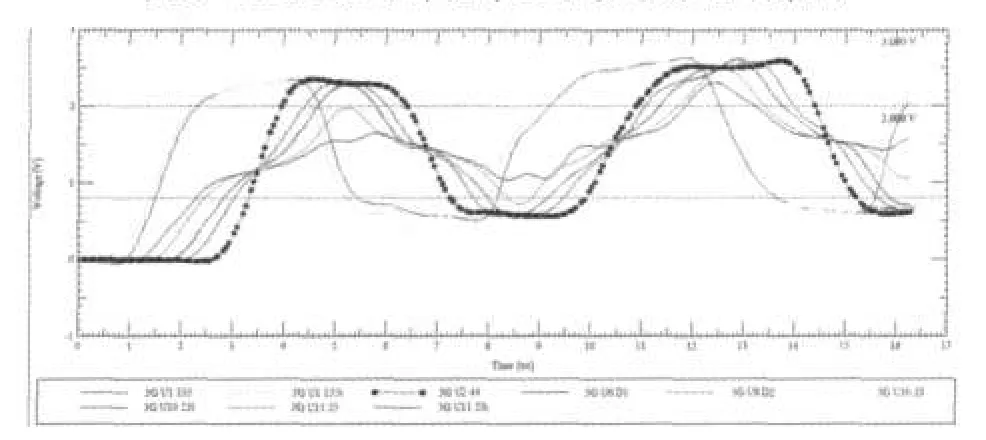

2.2 关键信号的SI问题及其仿真

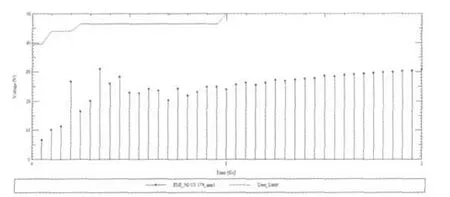

在硬件设计中,信号完整性问题主要表现为有信号反射、SSN和信号串扰。在本设计对SDRAM和CPU之间的总线进行设计后仿真,图8~图10分别是时钟信号CLK、地址信号A2和数据信号D0的仿真波形。从仿真波形和数据中不难发现,信号上下沿单调,信号无上冲和下冲等反射。硬件系统中Clock信号的周期性特点往往成为EMI问题的罪魁祸首,图11中对SDRAM总线的1 332 MHz的时钟信号的EMI仿真结果,按照FCC CLASS A标准定义,结果表明没有明显EMI超标问题。

图8 SDRAM时钟信号SI仿真波形图(截图)

图9 SDRAM地址总线信号SI仿真波形图(截图)

图10 SDRAM数据总线信号SI仿真波形图(截图)

图11 SCLK信号EMI仿真波形图(截图)

3 小结

笔者针对3G视频监控应用中存在的问题,设计了一个多模组的3G无线视频传输终端硬件平台。配合软件成功解决了当前3G无线视频监控存在的网络传输带宽问题。在硬件平台设计过程中,引入SI,EMC等前仿真和后仿真技术,使得硬件设计问题尽量早的在设计阶段就突出出来,并实施有效的控制手段。在实际项目的实施中极大提高了单板的一版成功率,极大地降低了产品设计成本及其研发成本。该硬件平台已经产品化并稳定运行在电力设备监测、无线应急指挥等系统中。

[1]黄帅,许雪梅,徐蔚钦,等.嵌入式3G无线视频监控系统硬件设计与信号完整性仿真[J].计算机应用,2010,30(9):2535-2540.

[2]夏振华,张正炳.基于3G移动通信的无线视频监控的设计[J].电视技术,2010,34(3):94-95.

[3]吴彦文.移动通信技术与应用[M].北京:清华大学出版社,2009.

[4]邵鹏.高速数字系统设计与仿真[M].北京:清华大学出版社,2008.