基于FPGA的AD9910控制设计

2011-03-14杨小勇毛瑞娟许林华

杨小勇,毛瑞娟,许林华

(国家无线电频谱管理研究所 陕西 西安 710061)

随着数字信号处理和集成电路的发展,要求数据处理速度越来越高,基于单片机+DDS(直接数字频率合成)的频率合成技术已不能满足目前数据处理速度需求。针对这一现状,本文提出了基于FPGA+DDS的控制设计,能够快速实现复杂数字系统的功能。

1 AD9910的硬件电路设计

AD9910是ADI公司推出的一款单片DDS器件,内部时钟频率高达1 GHz,模拟输出频率高达400 MHz,14-bit的DAC,最小频率分辨率为0.23 Hz,相位噪声小于-125 dBc/Hz@1 kHz(400 MHz),窄带无杂散动态范围大于80 dB,串行I/O控制,具有自动线性和随机的频率、相位和幅度扫描功能,1 024 32位RAM,具有调幅、调相的功能,1.8 V和3.3 V供电,可实现多片同步。应用在高灵敏度的频率合成器、可编程信号发生器、雷达和扫描系统的FM调制源、测试与测量装置以及高速跳频系统[1]。

AD9910芯片的主要外围电路为:参考信号源、控制、环路滤波器和输出低通滤波器等电路。参考信号源为AD9910提供基准频率,参考信号输入芯片后,内部的倍频器和锁相环起作用产生1GSPS的系统时钟;控制电路通过芯片的I/O给内部寄存器写入内容,寄存器内容不同,芯片工作状态不同,控制芯片可以是单片、FPGA或DSP,本设计采用FPGA;AD9910提供专门的管脚外接环路滤波器,以优化内部PLL的性能,环路滤波器为简单的低通滤波器;AD9910输出高达400 MHz的模拟信号,为了减少噪声,在它的输出端口设计了400 MHz的低通滤波器[2]。

图1为实际设计的AD9910外围连接图[3]。

在AD9910的电路设计中,应注意以下几个问题[4-5]:

1)AD9910电源和地设计。AD9910需要4组电源,AVDD(1.8 V)、DVDD(1.8 V)、AVDD(3.3 V)和 DVDD(3.3 V),模拟电源和数字电源需要隔离,电源管脚的滤波最好采用钽电容和陶瓷电容。在PCB设计中,数字地和模拟地分开,用磁珠单点连接,减少干扰。

2)AD9910环路滤波器设计。当外部的时钟较低时,例如100 MHz,系统时钟1 GHz,芯片内部的锁相电路起作用,这时需要在外部设计环路滤波器,如图1中R17、C47和C48构成的RC滤波器,电容电阻值用如下公式计算。

图1 AD9910外围电路图Fig.1 Peripheral circuit of AD9910

其中:N为分频比,KD为鉴相器的增益,KV是VCO的增益,fOL是环路带宽。

3)晶振电路的设计。AD9910需要外部提供参考信号源,它的质量直接决定了模拟输出信号的质量(频率精度和相位噪声),本设计采用高精度的温补晶振,频率100 MHz。在PCB设计时尽量靠近时钟管脚。

2FPGA控制AD9910的软件实现

采用Altera公司的EP1C6Q240C8控制AD9910,该器件的外部时钟频率为 50 MHz,20个 128?36 bit的 RAM块,5 980个逻辑单元(LE),240个管脚,属表贴器件。

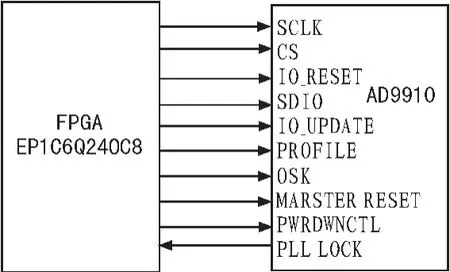

FPGA与AD9910的外围电路简单,无需外加任何驱动电路,从而节省了硬件电路设计和调试的时间,FPGA与AD9910的连接框图如图2所示。

图2 FPGA与AD9910的连接图Fig.2 Connecting diagram of FPGA and AD9910

其中,SCLK用于输出数据交换的控制时钟,CS为片选信号,IO_RESET控制DDS的系统复位,SDIO是数据传输线,IO_UPDATE使能DDS内部各寄存器数据更新,PROFILE用来选择八个相位/频率寄存器中的一个,OSK用来选择DDS的输出键控模式,MASTER_RESET用来清除所有存储单元,并且把寄存器设为默认值,PWRDWNCTL用来选择是否使用外部使能控制,不使用时置为0,这里设置为0,PLL_LOCK用来指示锁相环的锁定状态。另外,由于未采用多芯片数据通信,所以需将AD9910与同步信号相关的引脚悬空,例如7、8、9、10 和 53 引脚。

根据需要AD9910有4种工作模式可供选择,分别是单音模式、RAM调制模式、Digital ramp modulation模式和并行数据端口调制模式。这里选用最基础的signal-tone单音工作模式。

对AD9910的17个寄存器进行设置。这里使用了AD9910的评估软件对寄存器参数进行设置,只需要在评估软件中输入目标参数,软件将自动给出寄存器中的值,这样减小了工作量。根据需要,这里仅对其中的3个寄存器进行设置,分别是地址为0X01、0X02的控制寄存器和地址为0X0E的单音模式profile,而其他的寄存器均使用默认值,因此无需设置。

FPGA对AD9910的软件控制流程图如图3所示。

首先,对系统进行初始化,对FPGA的各控制信号进行复位操作,使能CS信号。

图3 FPGA的软件控制流程图Fig.3 Software controlling flow chart of FPGA

其次,对3个主要的寄存器进行设置。设置地址为0X01的寄存器CFR2,共32位,这里只需要使能第24位单音模式profile的幅度值,默认值为0,这里设为 1,其余均使用默认值,因此地址为0X01寄存器的内容为0X01_40_08_20。

地址为0X02的寄存器CFR3主要用来设置PLL和VCO的参数。其中,第26位到第24位用来选择PLL VCO参考时钟的频带,这里选择 820~1 150 MHz的 VCO5,因此为 101;第8位是PLL使能的选择,默认值为0,这里选择使能1;第7位到第1位这7 bit数据是PLL倍频器的倍频系数,默认值为0000000b,这里对外部时钟进行40倍频,因此,设置为0101000b。其余各位均使用默认值。所以,地址为0X02寄存器的内容为0X1D_3F_41_50。

对地址为0X0E的单音模式profile进行设置,它是用来控制DDS的幅度、相位和频率。其中第61位到第48位这14位用来设置幅度值,根据需要在评估软件中输入所需幅度值可以直接查看寄存器中相应位的值,这里使用默认值00_1000_1011_0101b;第47位到第32位这16位用来设置相位偏移量,这里仍旧使用默认值0X0000;低32位是用来设置频率控制字的值,频率控制字 M=fout×2N/fc,其中,fout为输出频率,N为频率控制字的位数,位数越大输出频率的分辨率越高,fc为系统时钟1 GHz,这里输出频率为50 MHz,对应的频率控制字为214748365,因此对应位的值设置为0X0CCC_CCCD。 地址为 0X0E寄存器的内容为0X08B5_0000_0CCC_CCCD。

最后,结束IO_UPDATE的操作动作,完成一次完整的设置过程。

对寄存器的读写操作是通过向输入端口SDIO发送8位指令来实现的,这8位中,最高位为读写指令,1为读操作,0为写操作,低5位用来选择在通信周期时选通哪个寄存器进行数据的传输,控制寄存器的内容,如表1所示。

表1 控制寄存器的内容Tab.1 Contents of control register

对AD9910读写操作时,需要注意AD9910的时序要求,对于串行I/O端口的各种控制信号之间的有4种基本的时序关系,分别是串口写时序,时钟在低电平停止;三线串口读时序,时钟在低电平停止;串口写时序,时钟在高电平停止;两线串口读时序,时钟在高电平停止。这里采用第一种时序关系,时序图如图4所示。

图4 串口写时序,时钟在低电平停止Fig.4 Serial port write timing,clock stall low

在SCLK上升沿,写入数据有效,FPGA控制SCLK信号的产生。具体写入数据的程序代码(使用Verilog HDL编写)如下所示:

//send cfr2

if (m==j) begin sdio=cfr2[i-1];sclk=1'b0;j=j+10’d4;end

if (m==p) begin i=i-1’b1;sclk=1’b1;p=p+10’d4;end

m=m+1’b1;

if (i==7’d0) begin state=next_state;m=10’d0;j=10’d0;p=10’d2;end

该指令用于对地址为0X01的控制寄存器CFR2进行写操作。鉴于FPGA的高速处理能力,在程序设计时需要注意一些特殊的时序要求,如以下几个方面。

1)AD9910开始工作时必须先将其复位,复位时间保持1 000个系统工作周期。

2)如果系统工作需要多次使用I/O_UPDATE,要注意I/O_UPDATE引脚置1的时间控制,这关系到系统能否顺利设置各个寄存器。

为了更好的说明FPGA对AD9910的控制,以下给出相关例程[6]:

always@ (posedge sclk_temp)begin

case (state)

s0: begin //DDS复位及初始化

io_update=1’b0;master_reset=1’b1;io_reset=1’b1;cs=1’b1;sdio=1’b0;sclk=1’b0;i=7’d0;j=10’d0;m=10’d0;p=10’d2;

osk=1’b0;profile=3’b000;state=s1;

end

s1:begin //保证复位时间

m=m+1’b1;

if(m==10’d100)begin

master_reset=1’b0;io_reset=1’b0;

state=s2; m=10'd0;

end

end

s2: begin //cs使能有效

cs=1’b0;

if(m==10’d2)

begin

state=s3;m=10’d0;i=7'd8;

end

else

m=m+1'b1;

end

s3: begin …… end //发送写CFR2指令

s4: begin …… end //发送CFR2的内容

s5: begin …… end //发送写CFR3指令

s6: begin …… end //发送CFR3寄存器的内容

s7: begin …… end //发送写single tone profile0指令

s8: begin …… end //发送single tone profile0内容

s9: begin //完成 io_update动作

m=m+1’b1;

if(m==10’d3) io_update=1’b1;

if(m==10’d8) begin state=s10;m=10'd0;end

end

s10: begin io_update=1'b0;p=10'd0;end //结束DDS设置

endcase

end

例程中,将update信号设置为手动,通过频率控制single tone profile0写入频率控制字0X0CCC_CCCD,此数字转换成十进制为214748365,代入频率控制字的公式,计算出频率为50 MHz。使用示波器测量观察,如图5所示。

图中,横坐标为时间t,单位为纳秒(ns),纵坐标为电压幅度(A),单位为毫伏(mv)。可以看出,输出波形的频率为50 MHz,与初始设定值一致。由此可见,程序符合设计要求。

3 结束语

图5 示波器的输出Fig.5 Output of oscillograph

FPGA对AD9910的控制是通过对其各个控制寄存器进行相关设置来实现的。随着FPGA的广泛应用,以及更快的数据处理速度,基于FPGA+DDS的方案对于频率源的设计与实现具有工程实践意义[7],而且还将在更多的领域得到应用。

[1] Analog Devices Inc,AD9910 Datasheet[EB/OL].2008.Http://www.analog.com /static/imported-files/data-sheets/AD9910.pdf.

[2] 张瑾,张伟,张立宝等.Protel 99SE入门与提高[M].北京:人民邮电出版社,2007.

[3] Analog Devices Inc,AD9910_PCBZ Datasheet[EB/OL].2008.Http://www.analog.com/static/imported- files/eval_board /AD9910_PCBZ.pdf.

[4] 王文理,王丽.DDS在数字频率特性测试仪中的应用[J].电子设计工程,2007(1):20-23.WANG Wen-li,WANG Li.Application of DDS in digital frequency characteristic testing instrument[J].Electronic Design Engineering, 2007,1:20-23.

[5] 郝迎吉,王长乾,王荣刚.基于DDS三相数字信号源的设计[J].电子设计工程,2007(9): 57-60.HAO Ying-ji, WANG Chang-qian, WANG Rong-gang.Research of three-phase digital signal source based on DDS[J].Electronic Design Engineering, 2007(9):57-60.

[6] 刘福奇,刘波.Verilog HDL应用程序设计实例精讲 [M].北京:电子工业出版社,2009.

[7] 王家礼,孙璐.频率合成技术[M].西安:西安电子科技大学出版社,2009:124-136.