一种基于电压控制的扫描测试功耗优化方法*

2011-03-06张红南文跃荣

张红南,文跃荣,邓 榕

(1.湖南大学物理与微电子科学学院,湖南长沙 410082;2.长沙大学电子与通信工程系,湖南长沙 410003)

一种基于电压控制的扫描测试功耗优化方法*

张红南1†,文跃荣1,邓 榕2

(1.湖南大学物理与微电子科学学院,湖南长沙 410082;2.长沙大学电子与通信工程系,湖南长沙 410003)

提出了一种通过电压控制来实现扫描测试低功耗优化的方法(压控法).该方法主要采用插入门控晶体管来控制组合逻辑单元供电,从而有效地解决了在扫描测试移入过程中测试信号向组合逻辑的无用传播,由于组合逻辑的供电受到控制,因此压控法不仅有效降低了无用的动态功耗,同时也大大降低了由于供电所产生的漏电静态功耗.而且门控晶体管的插入对于当前设计的面积和时序影响都很小.实验结果表明,压控法对面积和延迟的影响远远小于以往插入逻辑门单元的方法,同时对功耗的优化最高可达近32%的改善.

动态功耗;扫描测试;组合逻辑电路;测试信号;静态功耗

随着集成电路制造技术的发展及纳米时代的到来,高集成度使得芯片的测试功耗成为集成电路设计必须考虑的重要因素.采用扫描结构的可测试性设计(DFT)方法,能够提高测试覆盖率,缩短测试时间[1].然而,测试模式下产生功耗比在功能模式下产生的功耗要大很多.目前,已有研究指出在测试信号移入阶段,触发器跳变会影响组合逻辑,引起不必要的信号传播,导致了大量无用功耗产生[2].

本文提出了一种采用物理设计方案来降低测试功耗的方法.利用控制测试向量移入过程中组合逻辑做不必要的翻转来降低功耗[3],通过增加门控晶体管控制组合逻辑供电来实现低功耗优化.这与当前许多研究最大不同之处是不用改变现有测试流程以及相应测试工具[4],便可以在保持其原有性能的基础上大大降低芯片测试功耗[5].

1 插入逻辑门单元

插入逻辑门单元可以简单而有效地降低测试功耗[6].如图1所示,除了插入与门和或门单元,还可以插入MUX选择器或者扫描保持电路,插入扫描保持电路的方法相当于提供一个时序元件,这一方法非常有助于延迟故障的测试[7].在一个扫描保持设计中,每一个时序元件包含一个附加的存储单元(即保持锁存器),锁存器的输出直接连到组合逻辑路径,在扫描测试的移入过程中这一单元是不使用的.因此,它也可以有效地阻止测试信号向组合逻辑的扩散.

图1 逻辑单元的扫描测试电路Fig.1 Scanning test circuit of logical unit

然而上述方法因为加入了逻辑单元,所以增加了信号从触发器到组合逻辑传播的延迟.而且,增加的逻辑单元还会导致面积增加及正常功能模式下的开关功耗增大.本文提出了一种通过电压控制,将触发器连接的第1级组合逻辑单元供电电压关闭,信号会因为无法通过已经断开供电的逻辑单元而停止向组合逻辑传播.

2 压控法原理分析

压控法通过在第1级组合逻辑上引入一个门控晶体管,来门控住VDD或GND.这一方法同前面介绍的模块插入的方法相比,降低了峰值功耗和总功耗,缩小了芯片面积.并且,延迟的影响也明显得到改善.

图2 单独门控晶体管的插入Fig.2 Independentgating transistor insertion

如图2所示,图2(a)给出了独立门控晶体管插入的示意图.如果采用的是NMOS管(即门控GND)门控则是从“1”到“0”的跳变;如果采用的是PMOS管(即门控VDD)门控则是从“0”到“1”的跳变.从图中可以看出,输入端口IN从“1”到“0”的第一次跳变将会把输出OUT1变为VDD.这一跳变将会沿着反相器链传播下去.然而,此后输入端进来的任何跳变将不会再传播下去,因为此时的OUT1不能够被放电.这样就可以有效地减少扫描移入过程中多余的单元翻转.由于门控晶体管的引入,相当于在NMOS管的栅极挂上负载,输入端口IN对于高电平时的电压值会增大.

尽管采用独立的门控晶体管(即每一个逻辑单元都采用一个晶体管控制供电)可以有效地控制组合逻辑单元的开关激活,但是这样会造成很大的面积和延迟影响.为了克服这种影响,如图2(b)所示,仅在与触发器相连的第1级组合逻辑上增加门控晶体管,可以有效地屏蔽后面剩下的组合逻辑单元的跳变(transition).

3 输出端浮空的控制

采用压控法降低动态功耗的一个关键问题是:如果输出端电压由晶体管门控后被锁定在逻辑“0”,那么,此时的电路状态相当于第1级逻辑单元输出是浮空的.浮动输出电压取决于门控网络的PMOS管和NMOS管之间漏电流的平衡.另外,由于电路总的串扰噪声和瞬态效应的存在很容易改变一个浮动的输出电压.如果第1级门控的输出电压不能准确地稳定在VDD或者GND,将有可能引起后面被驱动的逻辑单元产生静态短路电流.以及紊乱的动态不定向翻转.这违背了原有的设计初衷,因此必须采用一定的方法来控制输出端电压的浮动变化.

如图3所示,在增加门控晶体管电路基础上加入一个上拉(或下拉)晶体管,这样就可以将输出端的电压值稳定在与门控晶体管锁定电压相反的状态.如图3 (a)所示,当采用门控GND方法时,当触发器输出由“0”到“1”时,门控GND使电路输出被锁定为ground.但是为了控制输出端浮空问题,此时采用上拉晶体管(Pull-up),电路输出可以有效地被控制在VDD;同样,当采用门控VDD的方法时,当触发器输出由“1”到“0”时,门控VDD使电路的输出被锁定为power.但是为了控制输出端浮空问题,此时采用下拉晶体管(Pulldown),电路输出可以有效被控制在GND.

4 优化方案设计

图4给出了采用压控法进行无用动态功耗优化设计的电路方案.通过对第1级逻辑单元的供电电压控制有效地消除了扫描测试移入过程中组合逻辑单元的开关激活.在一个扫描结构电路中,有2种方法可以实现动态功耗的压控法优化设计:1)对第1级的逻辑单元进行独立的电压控制,也就是给每一个第1级逻辑单元都加入相应的门控晶体管,如图4所示;2)对第1级所有的逻辑单元采用一个门控晶体管控制,如图5所示.

图3 输出端浮空问题的控制Fig.3 Control of the outputend floating

图4 第1级独立门控的电路设计方案Fig.4 Design of the first-levelindependentgating circuit

压控法除了降低测试过程中组合逻辑所带来的动态功耗,同时还可以通过输入测试向量控制算法有效地降低漏电静态功耗.随着工艺特征尺寸的不断缩小,漏电功耗已经成为芯片总功耗的关键来源.压控法不需要增加任何额外的硬件和控制信号,仅仅通过控制第1级组合逻辑的供电来降低扫描测试移入过程中的静态功耗.与逻辑门插入法相比优化力度和整体性能都得到很好的改善.

5 实验结果分析

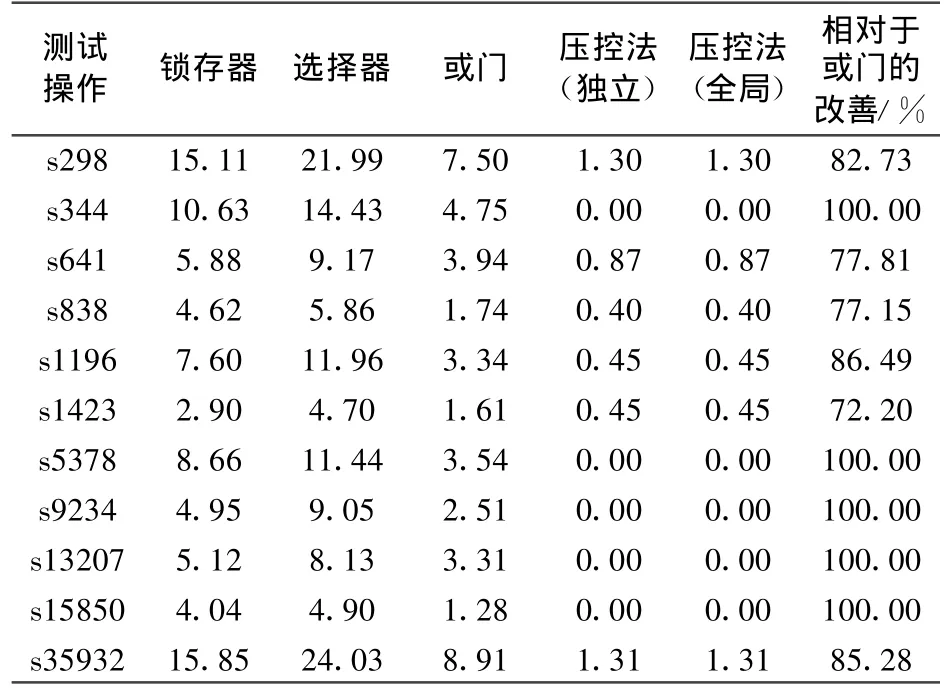

为了说明压控法对动态功耗的优化效果,本文对ISCAS89基台的测试电路进行了设计仿真.该仿真在70 nm BPTM模式下进行,以观测在低于100 nm情况下的门控效应.如表1所示,压控法对于电路延迟的影响最小.MUX常值法有最大的电路延迟,Latch常值法次之.常值法中插入或非门所带来的延迟最小(因为引入的单元最简单).表1最后一列给出了压控法相对于或非门常值法在延迟性能上的改善.压控法平均性能要比或非门高94%.

图5 第1级全局门控的电路设计方案Fig.5 Design of the first-level g lobal gating circuit

表1 延迟百分比增加的比较Tab.1 Comparison of percentage increase in delay

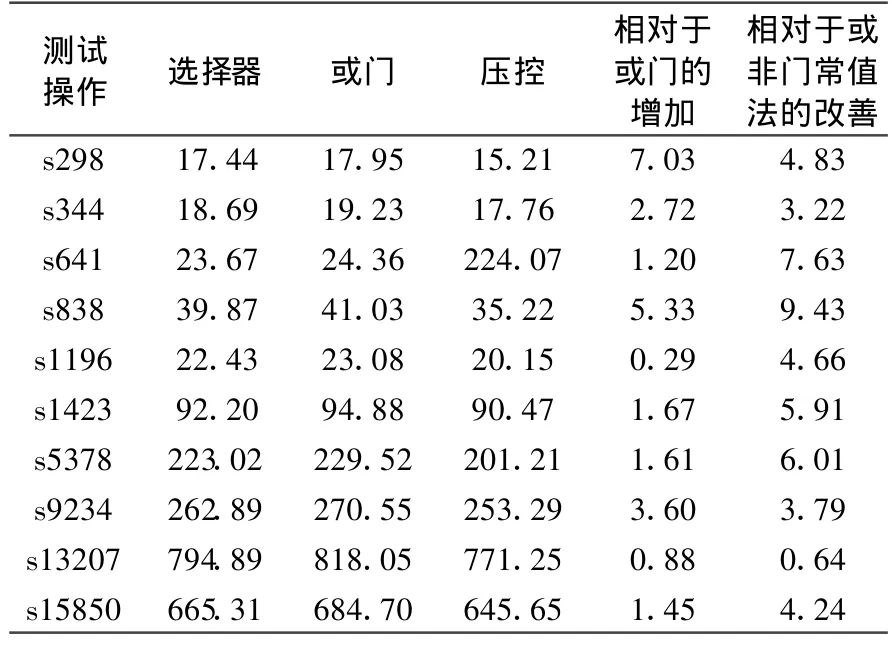

表2为测试模式下电路的功耗分析和比较.因为压控法能够控制组合逻辑的供电,所以扫描模式电路的静态功耗也得到了很好的改善.在表2的最后一列给出了功耗相对于或非门常值法的改善程度.

表2 测试模式下功耗分析和比较Tab.2 Power analysis and comparetion in testmode

6 结 论

本文主要介绍了一种优化动态功耗的方法——压控法,通过插入门控晶体管来控制第1级组合逻辑单元的供电,由此来阻止扫描测试信号向后面组合逻辑的传播.实验证明,在面积、延迟和功耗3个方面,压控法对电路的优化效果要比其他一般方法好很多.

[1] TANG H,REDDY SM,POMERANZ I.On reducing test data volume and test application time for multiple scan chain designs[C]//International Test Conference.Charlotte:IEEE, 2003:1079-1088.

[2] ABDO LLAH I A,FALLAH F,PEDRAM M.Leakage cu rrent reduction in CMOS VLSI circuits by input vector con trol [J].IEEE T rans on Very Large Scale Integ ration Systems, 2004,12(2):140-154.

[3] GIRARD P.Su rvey of low-pow er testing of VLSIcircuits[J]. IEEE Design and Test Com puters,2002,19(2):82-92.

[4] XU J,LI X K.Efficient physical design methodology for reducing test pow er dissipation of scan-based designs[C]//Netw ork,A rchetectu re and Storage.Zhang jiajie,H unan:IEEE, 2009:365-370.

[5] YOUSSEF A,ANISM,ELMASRY M.A comparative study betw een static and dynam ic sleep signal generation techniques for leakage tolerant designs[J].Very Large Scale Integration System s,2008,16(9):1114-1126.

[6] KHANDELW AL V,SRIVASTAVA A.Leakage con trol th rough fine-grained placement and sizing of sleep transistors [J].Compu ter-Aided Design of Integ rated Circuits and System s,2007,26(7):1246-1255.

[7] WANG Y,HE K,LUO R,et al.Tw o-phase fine-grain sleep transistor insertion technique in leakage critical circuits[J]. Very Large Scale Integ ration Sy stems,2008,16(9):1101-1113.

A Method for Scan Test Power Optimization Based on Voltage Control

ZHANG Hong-nan1†,WEN Yue-rong1,DENG Rong2

(1.College of Physics and M icroelectronics Science,Hunan Univ,Changsha,H unan 410082,China;

2.Co llege of Elec tronics and Communication Engineering,Changsha Univ,Changsha,H unan 410003,China)

This paper proposed amethod to accomplish scan test low-power optimization through voltage control. Thismethod is named voltage-controlmethod for short.It controls the power supply of combination logical units mainly through gating transistor insertion.Iteffectively solves the prob lem of the useless propagation to combination logic from test signals in the processof theshift-in of scan test.Thepowersupply of combination logic is controlled, thus the voltage-controlmethod not only effectively reducesuseless dynamic power,butalso substantially reduces the leakage current static power caused by power supply.Also the insertion of gating transistor has little influence on the designed areaand timing sequence.The experiment result has shown that the voltage-controlmethod hasmuch less influence on the area and delay than the logic gate insertionmethod,and also,the power optimization isimproved by nearly 32%.

dynamic power;scan test;com bination logic circuit;test signals;static power

TN407

A

1674-2974(2011)01-0040-04 *

2010-01-15

湖南省自然科学基金资助项目(851204013)

张红南(1952-),男,湖南益阳人,湖南大学教授

†通讯联系人,E-mail:zhanghongnan5@163.com