一种基于OSERDES复用的信号源设计

2011-03-06权友波王甲峰

权友波,张 伟,王甲峰,严 俊,岳 旸

(中国工程物理研究院电子工程研究所,四川 绵阳 621900)

0 引言

直接频率合成技术 DDS具有频率分辨率高、频率切换速度快、相位噪声低和频率稳定度高等优点,缺点是输出频率范围窄、输出杂散大。有FPGA和DDS芯片两种产生方式。若产生高采样率的模拟信号,通常做法是 FPGA产生DDS信号,输出到外部MUX芯片。MUX芯片对输入信号复用,将低码速率信号转换为高码速率信号,再输入到 DA芯片,最后输出需要的模拟信号。当PCB板上传输高速信号时,由于中间有一级MUX,串扰现象严重。

该设计利用FPGA内部OSERDES替代外部MUX芯片完成复用。若选用OSERDES的DDR工作模式,将输出数字信号码速率再次翻倍,FPGA的输出信号码速率可达1Gb/s以上,完全满足高采样率DAC输入的需要。由于FPGA输出直接进入DAC,去掉MUX复用,简化了印制板设计。从而减少串扰,提高板上信号传输质量。

1 基于OSERDES复用的高速DA设计原理

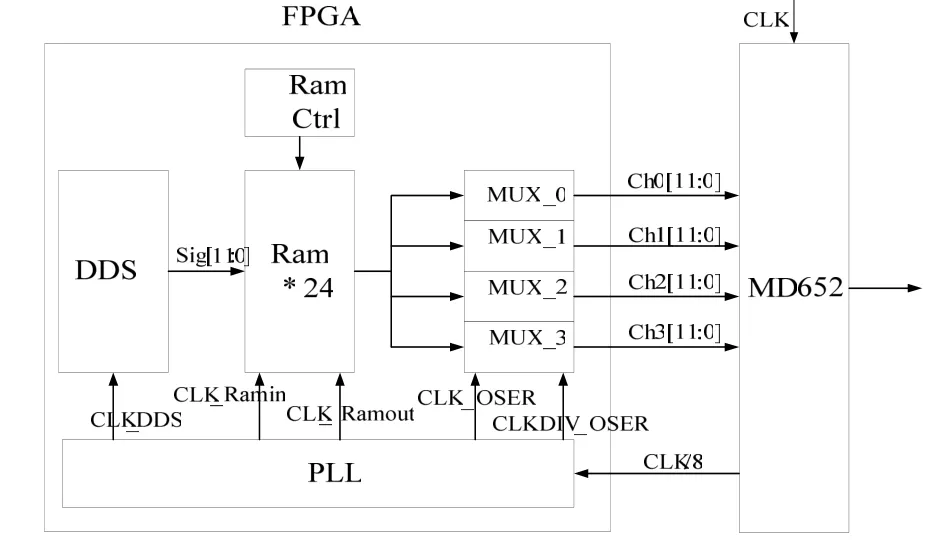

基于OSERDES复用的高速DA设计框图如图1所示,整个框图由Xilinx 的FPGA芯片Virtex-5 LX110和DA芯片MD652组成。FPGA利用DDS原理产生任意波形,通过DAC输出模拟信号。FPGA内部PLL模块输出需要的时钟,DDS产生任意波形数据存储在24个Ram中,Ram由Ram Ctrl模块控制。Ram Ctrl模块包含Ram读控制子模块和Ram写控制子模块。Ram中数据传送给四路MUX进行并串转换后输出,每路MUX由12个OSERDES构成。四路MUX输出数据在DA芯片内部再进行一次并串转换最终输出需要的模拟信号。

图1 基于FPGA的高速DA设计框

1.1 MD652芯片

MD652是EUVIS出品的一款高速12 bit数模转换器[3],芯片内部整合了一个48∶12的输入复用器,框图见图2所示。采样速率可达4.0~4.5 GSPS。在48对低速差分输入信号复用为12 bit的高速信号后,被锁存并驱动DAC输出模拟信号。4分频的时钟输出在采样相位选择管脚 SEL1和 SEL2控制下使得采样相位与输入数据对齐。同时提供8分频和4分频的差分时钟。

图2 MD652框

1.2 OSERDES复用

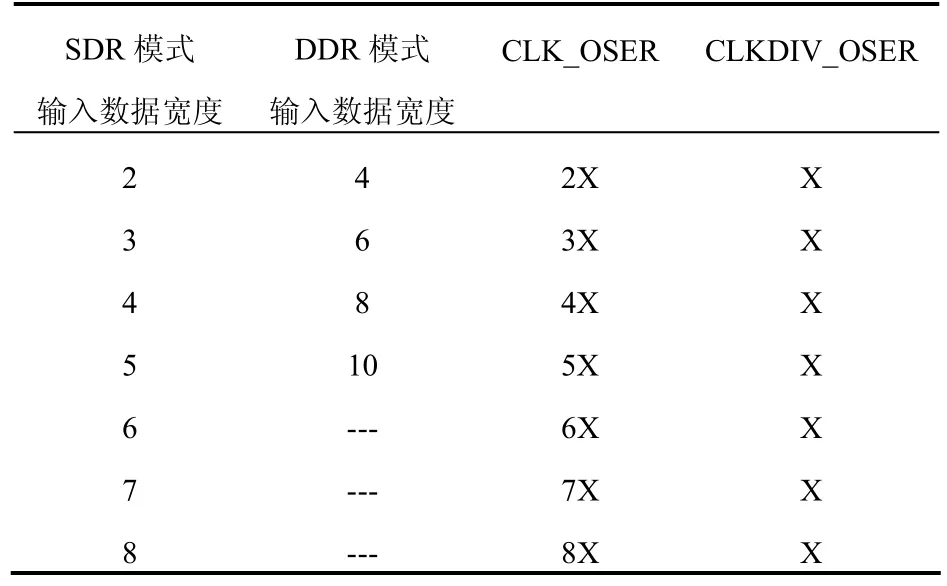

方案选用Xilinx Virtex-5 LX110产生DDS。LX110利用DDS技术产生0~450MHz的信号。借助OSERDES复用输出高采样率信号。OSERDES是专用的并串转换器[2],每个OSERDES模块包括一个用于数据和三态控制的专用串行器。单个OSERDES数据串行化可达 6∶1,可在两种模式下工作:单倍数据速率(SDR)和DDR。OSERDES使用CLK_OSER和CLKDIV_OSER两个时钟进行数据速率转换。CLK_OSER是高速串行时钟,CLKDIV_OSER是分频并行时钟。假设CLK_OSER和CLKDIV_OSER相位对齐,表1为数据转换器两种模式下CLK_OSER与CLKDIV_OSER之间的对应关系。

表1 数据并串转换器的CLK_OSER/CLKDIV_OSER关系

该方案选用DDR模式下单个OSERDES进行数据并串转换,采用 6∶1串行化。由表1可知 CLK_OSER是CLKDIV_OSER的三倍。由图 1所示 DDS输出信号位宽12 bit,每个MUX由12个OSERDES组成,4个MUX需12×4=48个OSERDES。OSERDES采用6∶1的比例复用,4路MUX需4×6=24个Ram。MUX复用顺序见表2所示。

表2 MUX复用顺序

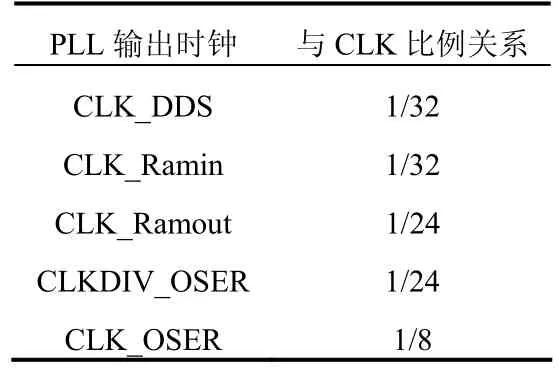

1.3 时钟分配关系

由图1所示,MD652时钟CLK由外部时钟源提供,将其8分频后输出给FPGA的PLL模块。PLL锁相输出FPGA工作需要的5个时钟:DDS的输入时钟CLK_DDS、Ram的输入时钟 CLK_Ramin、Ram 的输出时钟 CLK_Ramout,OSERDES分频并行时钟CLKDIV_OSER和OSERDES高速串行时钟CLK_OSER。各种时钟关系见表3所示。

MD652输出采样率为CLK的模拟信号,故FPGA输出CLK/4的四路数字差分信号。OSERDES选用 DDR模式,CLK_OSER为CLK/4/2=CLK/8。采用6∶1的串行比,则CLK_Ramout=CLKDIV_OSER=CLK_OSER/3=CLK/24。DDS输入频率范围是0~450 MHz,综合考虑输出信号稳定性、信号质量等因素,选择CLK的32分频作为DDS的时钟输入,接收DDS数据的Ram时钟CLK_Ramin=CLK_DDS= CLK/32。

表3 PLL输出时钟与外部输入CLK比例关系

2 硬件实现

当MD654工作频率为4GHz时,FPGA输出信号频率在1GHz。此时PCB板高速信号传输时存在严重的串扰等问题,需要丰富的高速PCB布线经验。该方案测试在CLK=2 GHz条件下进行。此时FPGA输出信号码速率500 MHz。DA芯片分别输出125 MHz和375 MHz单音频谱,如图3和图4所示。由图可知在CLK=2 GHz条件下SFDR可达50 dBc以上,完全可以满足设计要求。

3 结语

图4 CLK=2 GHz,fout=375 MHz时单音信号频谱

这里方案基于DDS基本原理,采用FPGA加DA芯片MD652的结构产生高采样率的任意波形信号。FPGA中的并串转换器OSERDES取代片外MUX将24路低速信号复用为4路高速信号,高速信号输入 DA芯片再进行一次复用后数模变换,输出高采样率模拟信号。通过实验验证了此方法的可行性。

[1] 薛小刚,葛毅敏.Xilinx ISE 9.X FPGA/CPLD设计指南[M].北京:人民邮电出版社, 2007:10.

[2] Xilinx Inc.Virtex-5 User Guide (ug190) [EB/OL] (2007-09-11)[2010-02-01].www.xilinx.com/cn/support/documentation/user_guides/c_ug190.pdf.

[3] Euvis Inc.MD652 Data Sheet[M].USA:[s.n.], 2007.