两片ADS7863与TMS320F28335的接口设计

2011-03-06谢战洪王大鹏

高 瑛,谢战洪,王大鹏

(郑州机电工程研究所,河南 郑州 450015)

0 引言

工程技术人员采用DSP芯片进行系统设计时,需要对很多信号进行采集,若仅使用DSP芯片上的A/D转换器进行信号采集,显然不够。因此,人们转向使用片外A/D转换器。现将阐述TI公司的TMS320F28335(以下简称F28335)的多通道缓冲串口(McBSP, Multi-channel Buffered Serial Port)与两片串行A/D转换器ADS7863的接口设计。

1 McBSP

[1-7]。TMS320F28335是一款高性能、多功能、高性价比32位浮点DSP。该器件最高可在150MHz主频下工作,片上集成丰富的外设,其中包括两个McBSP。McBSP是一种同步串行接口,除具有一般DSP串口功能之外,还可以支持T1/E1,ST-BUS,SPI等不同标准。McBSP包括6个引脚,分别是串行数据发送信号(DX, Data Transmit),串行数据接收信号(DR, Data Receive),发送时钟信号(CLKX, Transmit Clock),接收时钟信号(CLKR, Receive Clock),发送帧同步信号(FSX, Transmit Frame Synchronization)和接收帧同步信号(FSR, Receive Frame Synchronization)。McBSP通过这6个管脚为外部设备提供了数据通道和控制通道。

McBSP通过DX和DR实现DSP与外部设备的通信和数据交换。其中,DX完成数据发送,DR完成数据接收。控制信息通过CLKX、CLKR、FSX和FSR以时钟和帧同步的形式进行通信。由于 McBSP内有一个可编程的采样和帧同步时钟发生器,所以这些时钟和帧同步信号既可以由内部产生,也可以由外部输入。

McBSP发送数据的过程如下:首先将要发送的数据写入数据发送寄存器(DXR[1,2], data transmit register),如果发送移位寄存器(XSR[1,2], transmit shift register)中没有数据,则DXR[1,2]中的值先复制到XSR[1,2],再由XSR[1,2]将数据移到 DX上发送;如果 XSR[1,2]不为空,则等待将 XSR[1,2]中的数据全部移出到DX脚发送后才将DXR[1,2]中的值复制到XSR[1,2],再由DX脚将数据发送出去。

McBSP接收数据的过程如下:DR脚上接收的数据首先移入接收移位寄存器(RSR[1,2], receive shift register),一旦收到一个字(可以是8、12、16、24或32位),检查接收缓冲寄存器(RBR[1,2], receive buffer register)是否为空,如果为空,则将 RSR[1,2]中的数据复制到RBR[1,2],接着,数据被复制到数据接收寄存器(DRR[1,2], data receive register),CPU通过读取DRR[1,2]中的数据完成数据接收。需要注意的是,DRR2、RBR2、RSR2、DXR2和XSR2寄存器只有当接收或发送的字长超过16位(20位、24位和32位)时,才会用上。

2 ADS7863

2.1 ADS7863芯片的特点

ADS7863是一个双路、2MSPS、12位、3+3或2+2通道、基于连续逼近寄存器原理的同步采样模数转换器。ADS7863具有如下特点:①四路全差分或六路伪差分输入;②信噪比:71 dB,总谐波畸变率:-81 dB;③可编程的和缓冲的内部2.5 V参考电压;④灵活的省电功能;⑤可变的电源范围:2.7~5.5 V;⑥低功率操作:5 V时45 mW;⑦工作温度范围:-40~+125℃;⑧引脚与ADS7861、ADS8361等芯片兼容。

2.2 ADS7863芯片的工作原理

(1)ADS7863的主要引脚定义

ADS7863的主要引脚定义如下:①CHxy+:同相模拟输入通道 xy+(x代表A或B,y 代表0 或 1,eg:A1+);②CHxy-:反相模拟输入通道xy-;③M1:模式引脚1,选择SDOx数字输出,x代表A或B;④M0:模拟引脚0,选择模拟输入通道;⑤SDI:串行数据输入;⑥CONVST:转换开始;⑦RD:读数据;⑧CS:芯片选择;⑨CLOCK:外部时钟输入;⑩BUSY:ADC忙碌指示符;SDOB:转换器B的串行数据输出;SDOA:转换器A的串行数据输出。

(2)ADS7863的工作原理

ADS7863的工作模式根据M0、M1的不同配置分为四种,如表1所示。以下主要介绍ADS7863的M0=0、M1=1模式时的工作原理。当M0=0、M1=1 时,ADS7863工作在人为通道控制模式,数据只在SDOA脚输出,SDOB脚置为3态。SDI选择不同的模拟输入通道。当CONVST置高时,一个转换被触发。ADS7863需要32个CLOCK周期从两个模数转换器ADCs输出转换结果,需要1.0 us完成一个完整的CONVERSION/READ周期。如果CONVST信号每0.5 us被触发一次(RD信号的需要),那么每第二个脉冲被忽略。在CONVST的上升沿,不管CLOCK的状态,ADC从采样模式进入保持模式。经过一些延迟,BUSY信号变成高电平,并且在转换周期内保持高电平。在第二个时钟的下降沿,根据SDI寄存器的C[1∶0]两位的状态,ADS7863选择使用下一个转换周期的模拟输入通道。CS必须置为低电平以使能SDOA输出。在每个转换的每32个CLOCK周期的下降沿,数据是有效的。输出数据由一个‘0’,紧接一个 ADC指示符(CHAx为‘0’,CHBx为‘1’),12位转换结果,和一个‘00’组成。

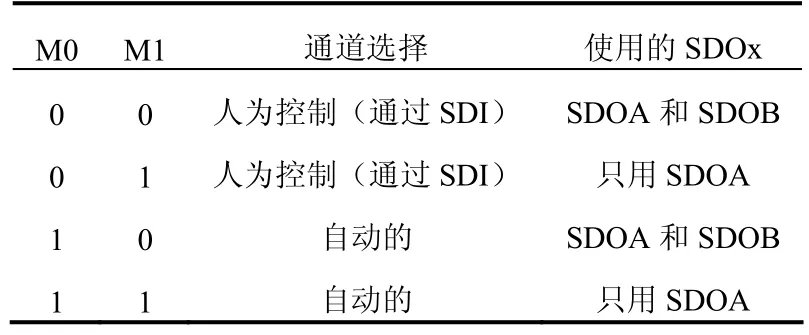

表1 M0/M1真值表

3 McBSP与ADS7863接口设计

3.1 硬件接口设计

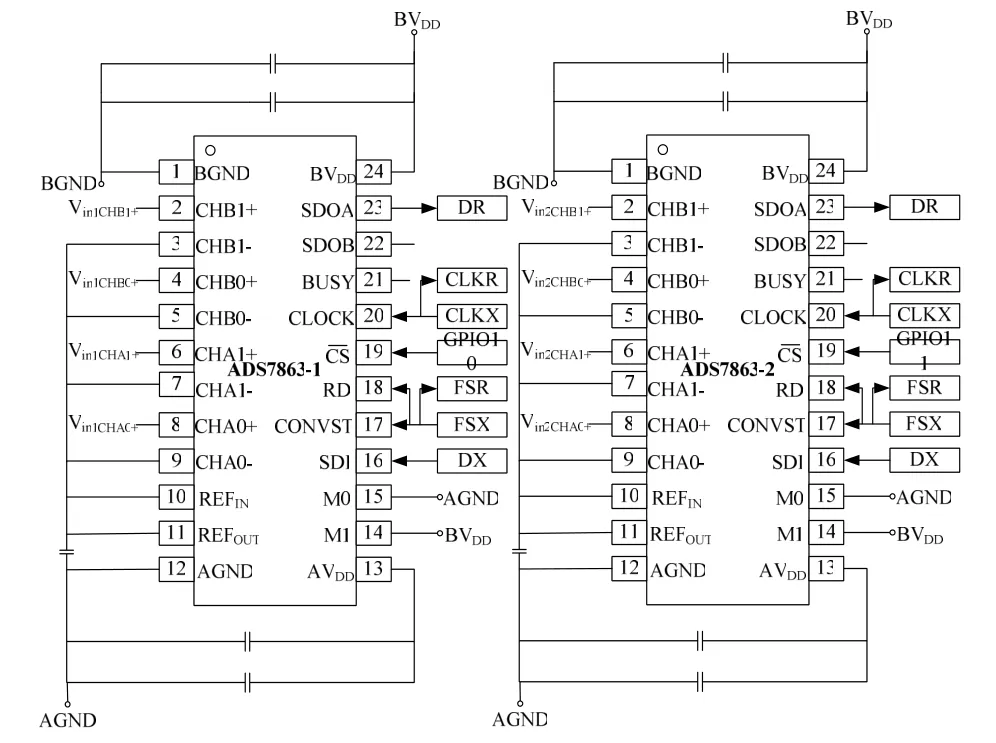

参考文献[8]。图1是F28335 McBSP与两片ADS7863无缝连接的示意图。该硬件接口设计中两片 ADS7863与同样的McBSP引脚连接。可以看出,McBSP与两片ADS7863之间的连接非常简单,实现了数据的高效转移,充分体现了同步串口连接的优点。

图1 McBSP与两片ADS7863无缝连接的示意图

由F28335 DSP的GPIO10向ADS7863-1提供片选信号、GPIO11向 ADS7863-2提供片选信号。McBSP的数据发送DX脚接两片ADS7863的SDI脚,向两片ADS7863发出控制信号。两片ADS7863的SDOA脚接McBSP的数据接收DR脚,向F28335传送数据信号。由McBSP内含的可编程采样率发生器生成时钟信号 CLKG和帧同步信号 FSG。由CLKG驱动发送时钟信号CLKX,CLKX驱动接收时钟信号CLKR和两片ADS7863的时钟信号CLOCK。由FSG驱动发送帧同步信号FSX,FSX驱动接收帧同步信号FSR和两片ADS7863的开始转换信号CONVST。CONVST初始化一个转换进程,并启动发送前一周期转换的数据。为了简化,只连接了两片ADS7863的CHA0+、CHB0+、CHA1+、CHB1+通道,可用输出数据的第二位(ADC指示符)分辨所采样的信号来自哪个通道,并用GPIO10、GPIO11判断所采样的信号来自哪个芯片。

3.2 软件接口设计

(1)MCBSP口初始化

参考文献[9-10]。整个初始化过程包括三部分:接收部分初始化、发送部分初始化和采样率发生器初始化。

①DSP初始化后,采样率发生器的初始化位GRST置0;在其它情况下,也可通过向串口控制寄存器2(SPCR2, Serial Port Control 2 Register)寄存器中的GRST位置0,使采样率发生器处于初始化状态。在此状态下,时钟 CLKG时钟为CPU时钟的1/2,帧同步信号FSG为逻辑0;设置接收初始化位RRST、发送初始化位XRST和帧同步发生器初始化位FRST为0;

②对采样率发生器SRGR[1,2]进行设置,并对其它控制寄存器进行设置;

③等待两个CPU时钟以确保内部正确同步;

④将采样率发生器初始化位置 1,使采样率发生器进行工作;

⑤等待两个SRG时钟;

⑥将接收和发送初始化位置1;

⑦在下一个CPU时钟的上升沿,CLKG时钟发送一个1,并以(CPU时钟/(1+CLKGDV))的频率运行;

⑧在数据发送寄存器DXR[1,2]被载入数据后,将帧同步初始化位置1以发出正确的帧同步脉冲信号。现是McBSP初始化程序片段:

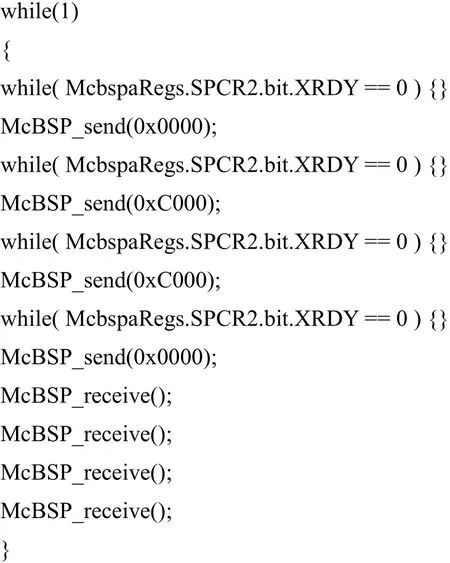

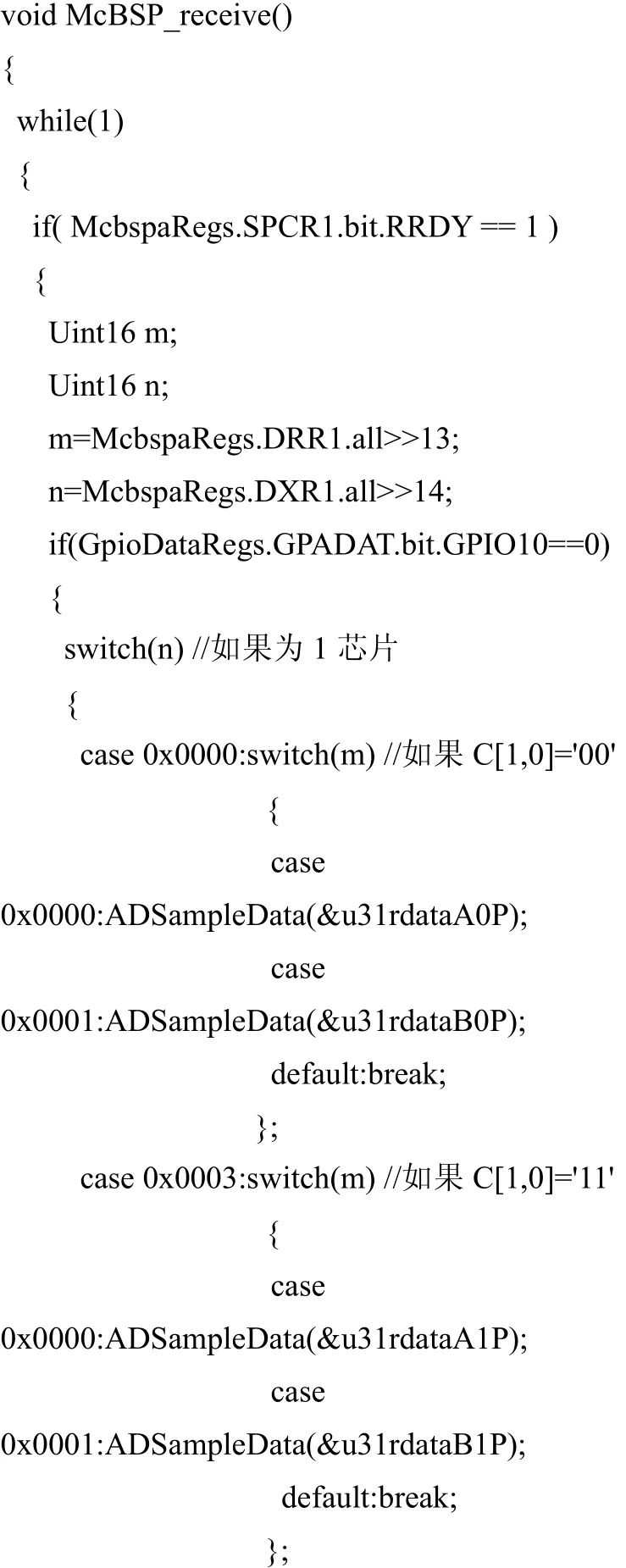

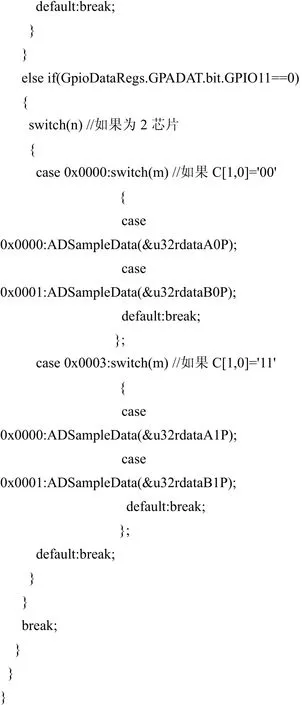

(2)McBSP串口通信主要程序

4 试验结果

当ADS7863的输入模拟量为以下时:

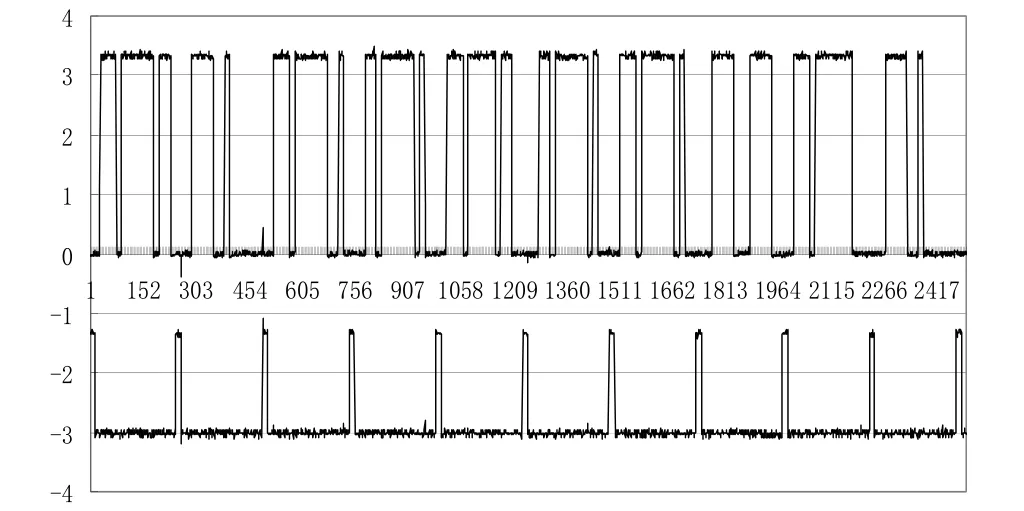

A/D转换器SDOA引脚输出如图2所示。图中第二条曲线为ADS7863的转换开始信号CONVST,第一条曲线为两片ADS7863的转换输出结果,输出顺序依次为:

试验中,通过设置McBSP的采样率发生器时钟分频系数CLKGDV,使得McBSP的采样率发生器时钟CLKG频率为 323.2 kHz,从而使得两片 ADS7863的外部输入时钟CLOCK频率为323.2 kHz、转换开始信号CONVST频率为20.2 kHz。

图2 SDOA输出

5 结语

与其它论文只用一个McBSP串口连接一片A/D芯片不同,通过一个McBSP串口与两片ADS7863之间的软硬件接口设计及试验结果,验证了一个 McBSP串口可以扩展更多的A/D芯片,从而可以采集更多的信号。对其它A/D系统设计具有很大的借鉴意义。

参考文献

[1] 薛志宏,刘建业.TMS320C54XX系列 DSP与 PC机间串行通信的实现[J].集成电路应用,2003(05):78-80.

[2] 唐丽萍,牛大胜.McBSP在音频处理中的应用[J].开发与应用,2005(06):44-46.

[3] 李季,戚俊,陈结祥,张毅,等.TMS320VC5402与高速 A/D的无缝连接[J].量子电子学报,2002,19(06):545-549.

[4] 张秀丽,李萍,陆光华.TMS320VC5402与串行AD/DA转换器的接口设计[J].电子工程师,2003,29(08):21-23.

[5] 赵军朝,谭争光,邵婷,等.TMS320VC54XX与串行A/D接口设计[J].火炮发射与控制学报,2008,32(03):58-60.

[6] 俞兴明.基于DSP的DMA和McBSP的双声道音频采集系统设计[J].电子测量技术,2009,32(02):118-120.

[7] 韩康榕,陆宏,季晓勇.数字处理器与通用异步串口通信的实现[J].通信技术,2002(01):55-57.

[8] 梁天明,耿相铭,陈健.多通道串行 A/D转换器与 TI DSPs的接口实现[J].通信技术,2002(05):4-7.

[9] 任治刚,孙洪波,张泽.TMS320C54x系列 McBSP 串口特性及其应用[J].内蒙古大学学报,2001,32(03):336-339.

[10] 王新艳,李欣.多通道缓冲串行接口简介[J].仪表技术,2007,(06):44-45.