基于时频分析的引信模拟器系统设计*

2011-01-15袁汉钦吉礼超

袁汉钦 吉礼超

(海军驻景德镇地区航空代表室1) 景德镇 333001)

(海军驻航空科技集团公司代表室2) 成都 610100)

基于时频分析的引信模拟器系统设计*

袁汉钦1)吉礼超2)

(海军驻景德镇地区航空代表室1)景德镇 333001)

(海军驻航空科技集团公司代表室2)成都 610100)

提出了基于时频分析的新型调频引信模拟器的硬件设计方案,以DSP系统为核心构建了时频分析算法实现的硬件平台,重点就调制电路,滤波电路进行了设计仿真。

时频分析;引信;DSP

Class NumberTN911.7

1 引言

在传统引信信号处理中,人们分析和处理信号的方法是傅立叶变换。但是,傅立叶变换是一个整体变换,在整体上将信号分解为不同频率分量,对信号的表征要么完全在时域,要么完全在频域,作为频域表征的功率谱,不能告诉我们某种频率分量出现在什么时间及其变化情况。然而在实际应用场合中,引信的差频信号都是非平稳信号。其统计量是一个时变函数,对信号进行单一时域或频域分析不能满足实际处理的需要,这时最希望得到的是信号频谱随时间的变化情况。鉴于此本文将时频分析的方法应用于新型引信的信号处理设计。

2 引信模拟器系统设计方案

用硬件实现的基于时频分析的引信模拟器系统的结构如图1所示。

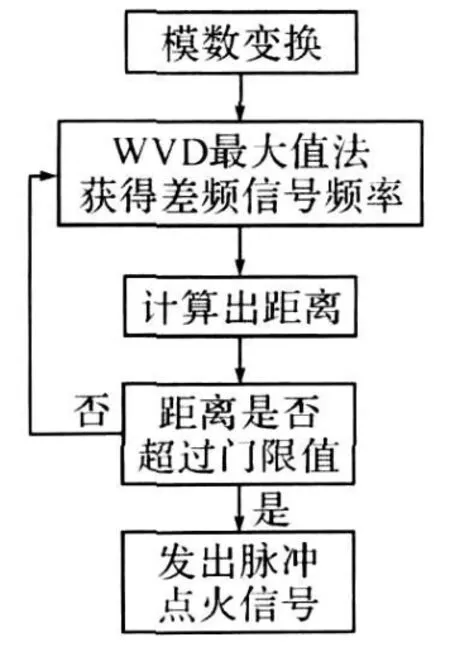

图2 基于时频分析的定距算法流程图

图1中各组成部分的功能说明:调制电路产生三角波作为压控振荡器的输入得到三角波调制的发射信号,一部分通过发射天线发射出去,另一部分作为本振与接收天线接收的信号混频,经过放大滤波,滤除直流分量和高频分量后得到差频信号,通过AD转化后交由DSP芯片处理,当判断目标在起爆范围之内后,给出脉冲信号,启动点火装置。

DSP模块完成对目标距离的判断,其信号流程图如图2所示。

3 调制电路的设计

本系统采用三角波线性调制,在调制器设计中主要用到两个芯片ICL8038和LM317。其功能图如下所示:

图3 三角波信号产生电路

ICL8038是一款单片集成电路,其功能为产生正弦波,方波,三角波,锯齿波以及脉冲的高精度信号发生器。它具有高保真,高线性较大的频率范围以及能够同时输出正弦波,方波,三角波等特点。

LM317是一款单片集成电路,如图 3所示。其功能为三端口可调正电压校准器,支持高于1.5A负载电流,输出电压可调,范围在1.2V~37V之间。它提供内部限流,过热保护以及安全范围内的补偿[1]。

通过对上述两款芯片的功能利用,设计本系统的三角波产生电路如图3所示。

在图3中,ICL8038的10和11脚间连接一个外加电容,通过对电容C的充放电,电容C两端的电压线性增加或线性减小,由于充放电时间相同,从而产生对称的线性三角波。控制开关的触发器产生方波。通过调整R1的阻值来控制LM317的可调电流,从而使得其输出电压可调,作为ICL8038的输入电压从引脚6输入。产生的三角波由ICL8038的引脚3输出作为压控振荡器的输入电压。

4 带通滤波器的设计

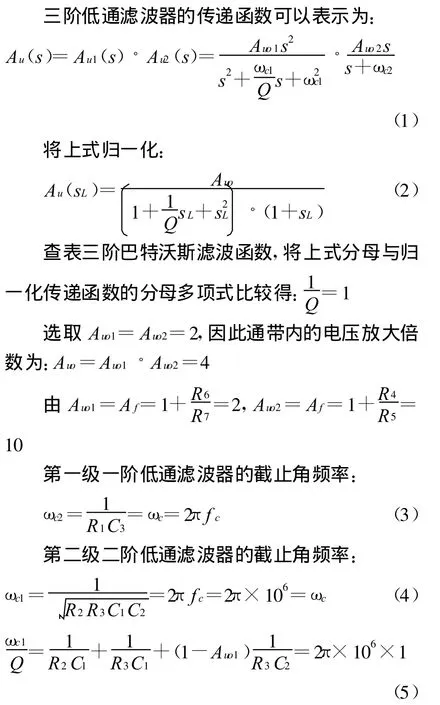

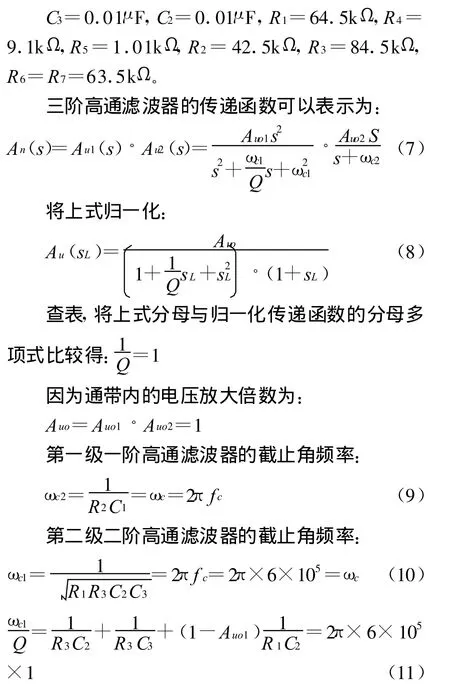

混频器混频后的信号即包括有用的差频信号,还包括直流分量和高频干扰,因此在信号处理之前要进行滤波得到有用的差频信号。我们设计的引信模拟器作用范围为 10m~20m,调制频率为2kHz,最大频偏为5MHz,因此带通滤波器的指标要求是通带为600kHz~1000kHz,通带衰减容限为小于1dB,阻带抑制为大于16dB/倍频程,增益大于20dB。

由于上截止频率和下截止频率之比远大于一个倍频程,因此该设计可以用低通滤波器和高通滤波器级联实现。频率响应指标被分解为单独的低通和高通设计。本文中采用一个600kHz高通滤波器和一个1000kHz低通滤波器组成带通滤波器来提取差频信号。

该滤波电路设计中采用的运算放大器是MCP602,MCP602是Microchip公司的2.7V~5.5V单电源CMOS双运算放大器[3]。该器件采用先进的CMOS技术,有偏置电流低、静态电流消耗少、运行速度快、开环增益高以及满幅输出等特点。

为了减少输入偏置电流及其漂移对电路的影响 ,应使:

根据上面的式子联立求解可以计算得

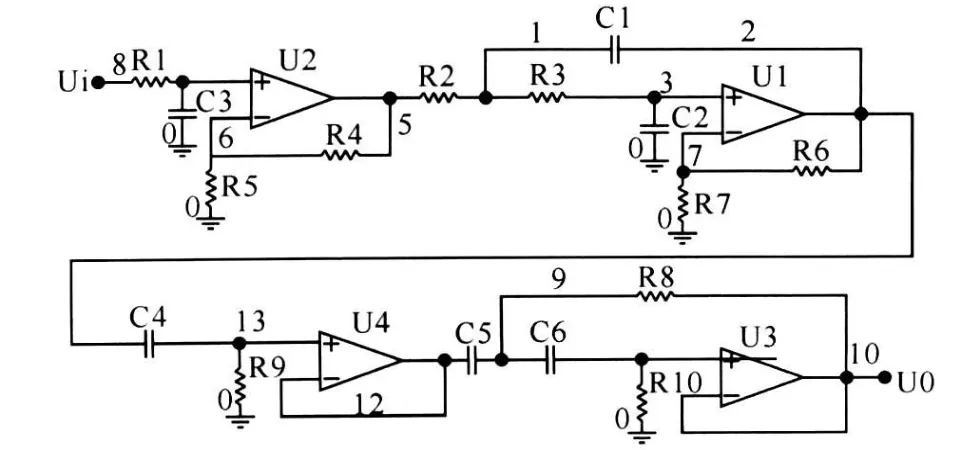

设计的低通滤波电路和高通滤波电路级联即可实现要求的带通滤波电路,带通滤波电路如图4所示[3]。

图4 带通滤波器电路

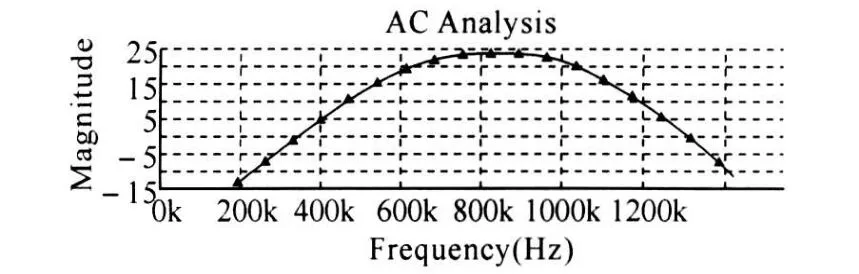

最后组成的带通滤波器的幅频响应如图5所示。从图中看出滤波器的通带满足设计需求。

5 A/D转换电路设计

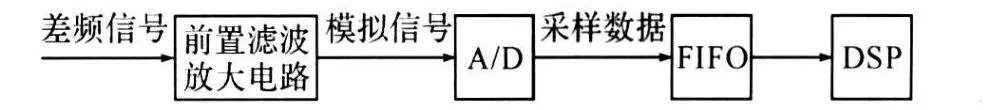

A/D电路用来完成对差频信号的采样,并将其转换为数字信号处理交给DSP进行处理。图6为从混频器输出的信号到DSP经过的几个阶段。

图5 带通滤波器幅频特性

在模拟引信系统中选用的ADC为MAX1426。这是一种单片集成的10位 ∑-ΔADC,内部集成了采样/保持放大电路,极大地减少了外围器件的数目。内部提供+2.5V电压基准,也可采用外部提供电压基准的方式。它的输入带宽高达150MHz,转换率可从0.1MHz~10MHz,在转换率为2MHz时,信噪比高达61dB,即模拟电压采样误差可以达到0.1%以下(绝对误差为±LSB)。MAX1426的输入采样电压范围为-2V~+2V,数字部分既可采用5V电源,也可用3.3V电源,输出数据为2的补码形式,可以很方便地与各种电平逻辑的处理器连接而无需电平转换。

图6 A/D电路流程图

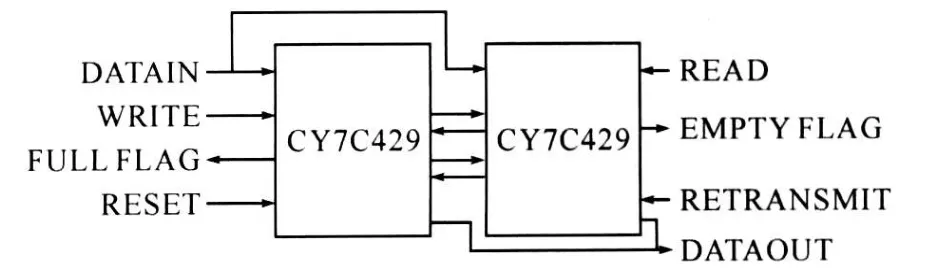

因为采样的速率高达 2MHz,若频繁的中断DSP则会造成处理器处理时间的大量浪费,所以,对采样的数据进行有效的缓冲就显得十分必要。将采样的数据先送往FIFO暂存,然后再集中交给DSP处理。这样就可以有效地节省DSP的处理时间。而且,利用FIFO的读使能和写使能可以控制对ADC采样数据的保存和读取。

本系统采用的FIFO器件是CY7C429,该器件是一种2K×9的先进先出存储器。因为ADC的输出数据是10位的,所以CY7C429的位宽不够,要用两个CY7C429并联。两个FIFO并联的电路图如图7所示[4]。

图7 FIFO并联电路

CY7C429使用的是5V电源,于是前面说的ADC芯片MAX1426的数字部分也采用5V供电。

利用FIFO的R(读使能)和W(写使能)当引脚,可以用两个就绪信号来控制采样数据的存入和读取。这样,可以保证只有当DSP处理完目前的工作并准备就绪后,FIFO才能向DSP送入下一组数据;当DSP读取完FIFO中所有的数据后,再发一个信号,启动ADC向FIFO写数。这两个就绪信号是由CPLD译码产生的,当DSP芯片对I/O中的FIFO地址进行读操作时,CPLD对地址译码,与DSP芯片的读写(R/W#)信号、I/O空间选择信号(IS)相或,并检测FIFO的数据满信号,若FIFO的数据已满,则产生 FIFO的读信号,如FIFO中的数据还未满,则给 DSP芯片发等待信号。

6 信号处理模块设计

我们选择 TI(Texas Instruments)公司推出TMS320F2812DSP芯片来完成我们对信号的实时处理,它提供了强大的计算能力,集控制器和高性能DSP的特点于一身,是工业界首批32位内含闪存以及高达150MIPS的DSP。图8为CPU的结构设计。

在较高信噪比情况下,可以通过 WVD最大值法完成差频信号瞬时频率的精确估计,因此我们在此讨论WVD算法的 DSP实现[5]。

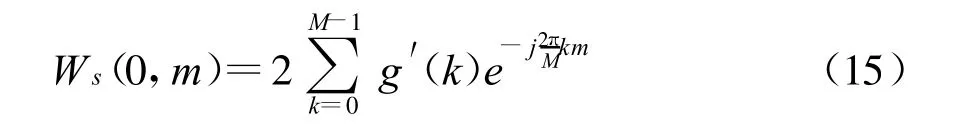

对于输入无限长信号,不能直接进行计算,对信号进行离散化加窗后才能用于实时的处理。若我们想求t=ta时的WVD,则可利用h(t)对x(t)截短。所以在这里采用的是伪WVD算法。连续的WVD的算法如式(14)。令采样频率为 fs,t=n/fs,τ=2k/fs,对频率离散化 ωm=mπ/M,即一个周期内取M点,窗函数为h(t),时域和频域离散化的PWVD算法为:

图8 DSP运算单元结构

当我们用窗函数h(t)在时间轴上对 x(t)作一段一段的截短时,可以把截的每一段都移到时间轴的起点,即 t=0,令g(k)=x(k)x*(k)h(k)h(-k)

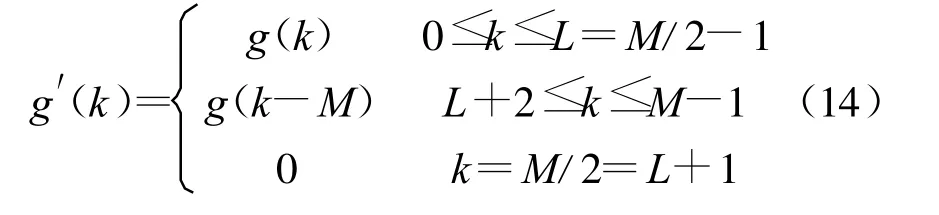

式(13)时域和频域都是离散的,可以用DFT来实现。做DF T时,还应将时域下标由k=-L,…,L,移为 k=0,1,…,2L+1,具体办法是:令移位后的序列为 g′(k)

式中M=2L+2,为了利用FFT,M可取大于2L+2时的2的整数次幂,这时要在式(14)中间补零。将式(14)代入式(13),得

图9 WVD算法的实现步骤

7 结语

本文提出了基于时频分析的模拟引信系统的设计方案,并设计了调制电路以及提取差频信号的带通滤波器,给出了信号Wigner-Ville分布的程序实现算法及流程图,讨论了基于信号PWVD的信号瞬时频率估计的DSP软件实现,完成了系统的整体设计。

[1]张雄伟,陈亮.DSP芯片的原理与开发应用[M].北京:电子工业出版社,2003

[2]牛燕炜.有源低通滤波器的设计与仿真[J].现代电子技术,2007(12):181~183

[3]李良荣.EWB9电子设计技术[M].北京:机械工业出版社,2007

[4]苏小妹.软件无线电调制解调系统的研究[D].长沙:湖南大学,2005

[5]艾俊轶.毫米波高精度测距雷达信号处理及实现[D].成都:电子科技大学,2006

Design of FMFuseSimulator System Based on Time-frequency Analysis

Yuan Hanqin1)Ji Lichao2)

(Aviation Military Representative Office of Navy in Jingdezhen1),Jingdezhen 333001)

(Aviation Military Representative Office of Navy in Aviation Technology Group2),Chengdu 610100)

The article proposed the new FM fuse simulator hardware design which make DSP system as the core to build a time-frequency analysis algorithm hardware platform,designed the modulation circuit,as well as filter circuit.

time-frequency analysis,fuse,DSP

TN911.7

2010年8月15日,

2010年9月22日

袁汉钦,男,硕士研究生,助理工程师,研究方向:信号处理。