基于可编程逻辑器件单稳态电路的设计与实现

2011-01-05王坤宁周宁侠

韩 彬 王坤宁 周宁侠 余 坤

(中国石油集团测井有限公司装备与销售分公司 陕西西安)

基于可编程逻辑器件单稳态电路的设计与实现

韩 彬 王坤宁 周宁侠 余 坤

(中国石油集团测井有限公司装备与销售分公司 陕西西安)

针对常规硬件电路实现单稳态功能,存在电路复杂、灵活性差的问题,所提出新的解决方案。文章就中子寿命地面仪中解码电路的设计,提出采用可编程逻辑器件来实现的设计思想,从硬件及软件两个方面描述此电路的设计方法,并给出了VHDL软件设计的实例。经时序仿真及实际使用验证,基于可编程器件的单稳态电路设计,大幅提高单稳态电路关于脉冲宽度、精度及稳定性的要求,具有控制灵活、使用方便的优点。

可编程器件;单稳态;VHDL;时序仿真;Altera

0 引 言

在电路设计中,常使用单稳态电路完成整形、延时、窄脉冲展宽等功能,通常使用元件 74LS123、74LS221等集成单稳态芯片来实现[1、2]。目前使用的中子寿命地面仪中解码电路,就使用了74LS123和74LS221元件实现窄脉冲展宽功能。

无论采用哪种元件,都由外围的R、C阻容元件决定定时时间。由于每一个阻容元件具有不同的参数误差,以及受外围温度影响较大,导致单稳态电路定时精度低且稳定性较差,工作的可靠性不高;同时,定时时间由外围阻容元件决定,一旦外围电路固定,较难改变定时时间,缺少灵活性;此外,这种单稳态电路结构复杂,占用电路板面积大,无法做到集成化、小型化[3]。针对单稳态电路目前现状,有必要选择一种新的方法取代当前电路。

随着电子技术特别是数字集成电路技术的迅猛发展,可编程逻辑器件的逻辑容量和工作速度不断提高,产品价格越来越低,得到了广泛应用。利用可编程逻辑器件替代目前的单稳态集成电路,可以有效提高单稳态电路关于脉冲宽度、精度和温度稳定性方面的要求,还大幅减小电路面积,提高集成度。可编程逻辑器件采用VHDL(Very High Speed Hardware Description Language超高速硬件描述语言)描述,硬件设计软件化,具有极强的灵活性。

1 电路设计

Altera公司为可编程逻辑器件的领导者,其产品一直在业界占有重要地位。本设计使用Altera公司的EPM7128元件,实现中子寿命地面仪解码电路中,单稳态电路脉冲展宽功能。EPM7128作为Altera公司推出的一款经典可编程逻辑器件,具有高容量、高性能、功耗低、成本低的优点,得到了广泛的应用,而且其电源部分及I/O端口使用+5 V标准,便于和外围的TTL元件接口对接,这样对现有箱体不做大的改动情况下,迅速实现设计要求,加快设计进度[4]。

和通常的硬件电路设计不同,可编程逻辑器件设计的重点是软件部分,即所谓硬件设计软件化,使用软件编程来实现硬件电路功能。本设计采用Altera公司的Quartμs II设计软件,使用VHDL语言编程。但是,常见的单片机C语言编程是单步串行工作的,是串行语句,而VHDL语言描述的对象是硬件电路,上电后,所有硬件电路同时工作,故VHDL是并行语句。使用VHDL编程,不能按照纯软件的设计思想,而要按照描述电路的思想,也就是说,使用VHDL编程对应得是一个个硬件电路。因此,每编写完成一段程序以后,生成的是什么电路,具有什么样的功能,都要做到心中有数[5、6]。

故此,基于可编程逻辑器件的单稳态电路,其软件设计思想就是把一个电路合理的分解为几个电路,从而实现单稳态电路功能,而对外围电路来说,只需把对应的管脚连接起来即可。

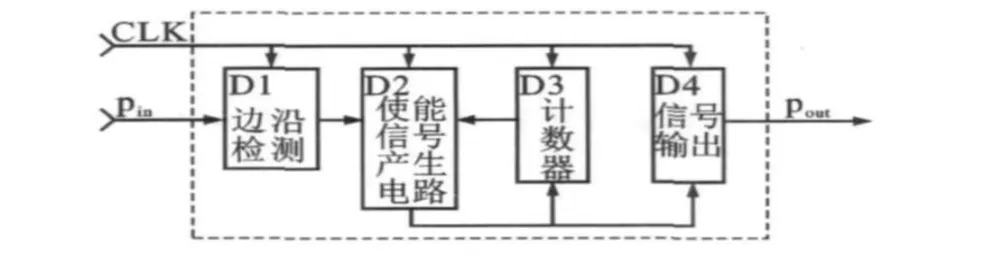

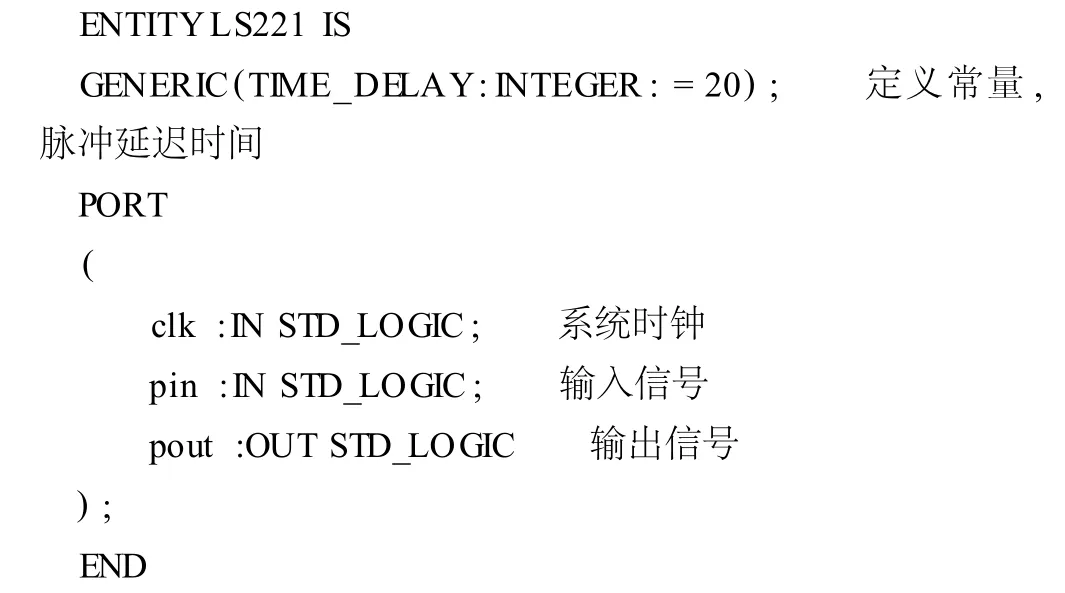

基于CPLD器件,使用VHDL语言,采用模块化设计理念实现的单稳态电路如图1所示。整个电路有三个管脚,分别为系统时钟输入端CLK、脉冲信号输入端Pin、脉冲信号输出端Pout。其内部电路分解为边沿检测电路、使能信号产生电路、计数器及信号输出电路等四个电路。

图1 CPLD内部电路分解图

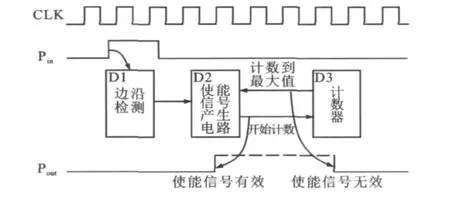

图2 CPLD内部电路工作过程

CPLD内部电路工作过程如图2所示,脉冲信号输入端Pin管脚输入的脉冲信号首先进入D1边沿检测电路,当它检测到一个上升沿时,对D2使能信号产生电路起作用,使能信号有效;当使能信号有效时,D3计数器开始计数,同时D4信号输出电路输出高电平,当计数器计数到最大值时,使能信号无效,这时D3计数器停止计数并清零,同时D4信号输出电路输出低电平,这时,本次单稳态电路工作完毕,等待下一次输入脉冲。所有的电路都在系统时钟CLK的控制下工作,保证电路为同步电路,避免出现毛刺,同时,系统时钟又决定了定时时间的精度,在芯片所能认定的最高频率范围内,提高系统时钟就能提高定时时间的精度。在本次设计中使用的系统时钟确定为1 MHz时,单稳态电路的精度就是1μs。其程序的部分代码如下:

2 验 证

Quartμs II是Altera公司新推出的设计软件,具有输入、综合、布局布线、下载等功能,还具有时序仿真功能。通过时序仿真功能,可以观察输出信号是否满足设计要求,验证电路设计是否正确;通过时序仿真功能,可以及时发现设计中的错误,从而大大缩短设计时间,提高设计的可靠性,这也是可编程逻辑器件最大的优点之一。

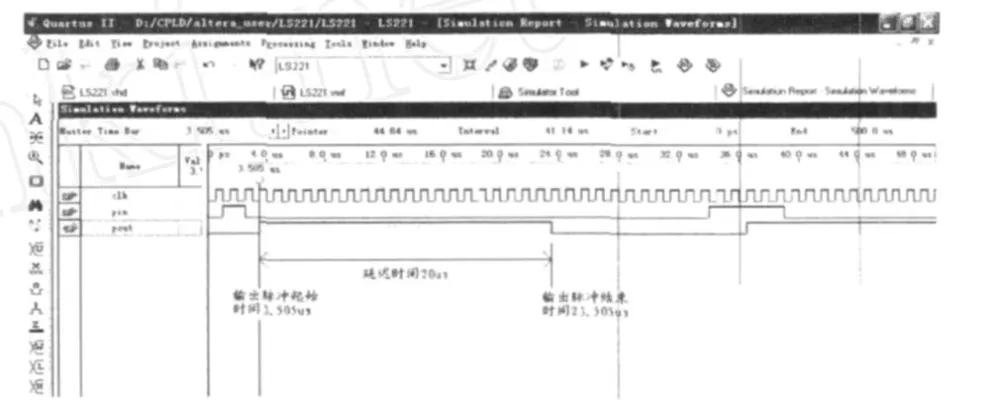

使用Quartμs II设计软件,其生成的时序仿真波形如图3所示。

图3 单稳态脉冲展宽电路时序仿真图

由图3可以看到,当输入端Pin出现一个脉冲信号后,输出端Pout就会产生一个维持一段时间高电平的脉冲信号。这个时间是在类属表中定义,如程序部分所示,这里定义为20,GENERIC(TIME_DELAY:INTEGER:=20)。系统时钟设置为1 MHz即1μs时,延迟时间就定义为20μs,测量Pout的宽度,可以看到它的宽度为20μs,表明当输入端出现一个窄脉冲信号时,输出端就会产生一个时间宽度为20μs的脉冲信号。时序仿真结果证明本电路符合设计要求。

另外,使用示波器验证设计正确与否。在输入管脚输入一个窄脉冲,在输出管脚用示波器测量,看输出脉冲的长度是否等于程序中定义的延迟时间。经实际测量,完全符合程序要求的延迟时间,证明本电路符合设计要求。

3 结束语

随着可编程逻辑器件性能的不断提高、体积的不断减小和成本的不断降低,已经广泛使用在各种电路设计中。基于可编程逻辑器件的单稳态电路,无需外接R、C定时元件,从而大幅提高单稳态电路关于脉冲宽度、精度及稳定性的要求,输出脉冲宽度准确、稳定、精度高,仅与系统时钟有关。同时,一片CPLD元件即可替代几十片常规元件,大大减少了电路面积,提高了设计的集成度,使用单稳态电路越多时,这个优点越明显。基于可编程逻辑器件的单稳态电路设计,使得硬件电路设计软件化,整个过程如同软件编程一样方便,简单的几句话就能改变它的延迟时间,在模块化设计中,上层模块调用单稳态脉冲展宽模块时,只需在元件调用语句中修改类属表GENERIC中的定义即可。在描述语句中只需要一点小小的改变,产生的电路形式也多种多样,在计数器清零判断语句中只判断使能信号,这样描述的电路就是元件74LS221,不可重触发脉冲展宽电路;在计数器清零判断语句中判断使能信号或输入端的上升沿,这样描述的电路就是元件74LS123,可重触发脉冲展宽电路。

不仅如此,基于可编程逻辑器件的单稳态电路设计,使用时序仿真功能,提前就能验证电路设计是否正确,及时发现错误,不像以前只有等电路板全部焊接好以后,才能验证,有效保证电路的准确性,减少设计时间和成本。

不管是时序仿真,还是对信号的实际测量,其结果都表明,基于可编程逻辑器件的单稳态电路,达到了预期的设计效果,完全可以取代旧式的设计电路。本设计已经使用在最新设计的中子寿命地面仪解码电路中,产品计划出口到伊朗。基于可编程逻辑器件的单稳态电路,以其强大的功能,众多的优点,必将得到越来越广泛的应用。

[1] 袁绍明.基于CPLD器件的单稳态脉冲展宽电路[J].电子技术应用,2001,12(5)

[2] 王金花,姚宏宝.可编程逻辑器件实现单稳态触发器[J].红外与激光工程,2002,31(2)

[3] 赵世平,张玉华.基于VHDL的全数字单稳态电路研究[J].电力学报,2005,19(4)

[4] Altera公司.EPM7128数据手册.2004(资料)

[5] 侯伯亨.数字系统设计基础[M].西安:西安电子科技大学出版社,2000

[6] 蔡良伟.数字电路与逻辑设计[M].西安电子科技大学出版社,2009

TP331.1

B

1004-9134(2011)06-0075-02

韩 彬,男,1972年生,工程师,1996年毕业于江汉石油学院仪器专业,现在中国石油集团测井有限公司装备与销售分公司从事工作。邮编:710068

2011-06-05

梁保江)

·开发设计·