ADF4157在数字预失真时钟方案中的应用

2010-12-21张福洪罗晚会杨小海

张福洪,罗晚会,杨小海

(杭州电子科技大学通信工程学院,杭州 310018)

在现代电子技术的设计与开发过程中.特别是在通信、雷达、航空、航天以及仪器仪表等领域,都需要进一步提高一系列高精度、高稳定度的频率源的频率精度,频率合成器是无线通信设备中的一个重要组成部分,其设计的优劣直接影响到通信设备的性能。

由于数字预失真(DPD)技术是对信号进行非线性处理,通常预失真后的信号带宽为原始信号带宽的5 ~7倍,这样DPD算法才能在最大程度上发挥性能。由此应选择恰当的上变频和下变频方案及相应的时钟方案,以确保信号的质量。本文结合新型PLL频率合成器ADF4157 设计一款适用于数字预失真系统本振时钟的频率合成器, 方便地实现DPD系统上下变频所需要的时钟。

1 PLL频率合成器ADF4157简介

ADF4157[1]芯片是美国ADI公司推出一款全新的具有高分辨率,小数分频的PLL频率合成器(FNPLL),内部结构如图1。

图1 ADF4157内部结构

其内部集成1个小数N分频的频率合成器,具有25 bit固定模数,在6 GHz实现亚赫兹频率分辨率。1个参考时钟输入端且输入范围为10 MHz到300 MHz, 2个RF预分频输入端RFINA/RFINB,一个参考输入频率倍增位D和一个参考输入2分频位T,低噪声数字鉴相器,精密电荷泵(CP),可编程参考除法器, ADF4157小数分频有多种实现方式,本文采用Σ-Δ小数频率合成器实现方式,且ADF4157内置周跳减少电路,在不需要对环路滤波器进行更改的情况下实现了更快速锁定。这种小数N分频的PLL频率合成器适合用于需要低相位噪声和超精细控制分辨率的应用,最大的特点是在参考频率不变的情况下,比任何单环NPLL可以有更小的步进变化,通过提供鉴相频率既可增加环路带宽、加强反馈、加快频率转换时间,又可降低与大分频比N有关的参考相位噪声的倍乘,从而可获得比NPLL环路更好的噪声性能,提高了频谱纯度。按照FNPLL频率合成器的方法,得到的输出信号频率不必是参考信号频率的整数倍,也可以是小数倍。小数频率合成器输出频率精度由参考信号频率和小数频率合成器的分辨位数决定,所以ADF4157支持高频率的参考信号的同时可以获得很高输出频率精度。

2 DPD系统本振时钟设计与实现

2.1 DPD时钟的总体方案介绍

基于Xilinx IP核的数字电视发射机中数字预失真技术方案的硬件平台主要有两部分组成:预失真基带单元和预失真时钟单元。本时钟单元为小数频率合成方案,所合成的频率精度高,频率高,频率合成器所涉及有PLL(锁相环)以及PLL+DDS(锁相环+直接数字频率合成)等合成原理。主要产生的频率为DVB-T时钟频率30.24 MHz, ADC采样时钟90.72 MHz, DAC采样时钟362.88 MHz, FPGA工作频率90.72 MHz,射频路上下变频频率的发射端第一级本振1 973.16 MHz、接收端第二级本振1 927.80 MHz、发射端第二级本振与接收端第一级本振2 482.44 MHz。

整个时钟板功能主要是由 10 MHz晶振、AD9516、LPF构成的一个类似PLL的环路来实现的。其详细的实现框图见图2。

整个时钟方案主要由两大部分组成,时钟分配器和PLL频率合成器,时钟分配器采用ADI公司的AD9549[2]和AD9516[3], PLL频率合成器采用ADI公司的整数N分频ADF4106[4]和ADF4360[5]及小数N分频ADF4157。

图2 预失真时钟板频率合成框图

本方案中的PLL频率合成器ADF4157 需要以AD9516送过来的fREF=181.44 MHz作为参考频率,合成发射端二级本振上变频频率和接收端一级本振下变频频率2 482.44 MHz,由于它要产生上下变频的本振信号,要求输出功率比较大,故在它所构成的PLL环路中加了一个集成运放,以提高外部VCO的输出功率,以致于满足预失真板上混频器的本振功率要求,且要增加一个功分网络将一路输出分成两路。

ADF4157内部小数N分频,通过Σ-Δ调制方式再结合频率合成器的环路低通滤波器输出低的相位噪声和更高的频率精度,本文ADF4157模块的鉴相频率为 2.835 MHz, 输入参考频率是 181.44 MHz,则步进频率为fPHD/225=0.084 489 6 Hz,输出频率分辨率(频率精度)为fREF/225=5.0473 Hz。用在DPD系统的接收机和发射机的上变频和下变频部分中,用来实现本振。

2.2 ADF4157内部主要寄存器配置

ADF4157所有寄存器的控制是通过简单的三线接口进行的,如图3。

图3 ADF4157 PLL频率合成器的串行控制接口

控制接口由时钟CLOCK,数据DATA,加载使能LE构成。加载使能LE的下降沿提供起始串行数据的同步。串行数据先移位到PLL频率合成器的移位寄存器中,然后在LE的上升沿更新内部相应寄存器,注意到时序图中有两种LE的控制方法。另外,需要注意的是对PLL芯片的寄存器进行写操作时,需要按照一定的次序来写,具体请参照芯片资料中的描述。

ADF4157通过INT与FRAC寄存器配置N分频器, N=INT+(FRAC/225),图2中的环路滤波器(LPF)的作用是滤除鉴相器输出信号的高频成分和噪声,并将鉴相器的输出电流转化为电压送到VCO的输入端,以控制VCO的输出频率。同时将VCO输出频率经过N分频后反馈给鉴相器。鉴相器的作用是对反馈频率和参考鉴相频率进行比较,当鉴相器两个输入信号的相位同步时, VCO的输出频率就是要锁定的频率。 PLL的R, INT, FRAC寄存器通过合理配置使外部VCO工作在2 482.44 MHz输出,将其快速锁定锁相模块。其关系式为

由(1), (2)得

Design of Shore Power Supply Supervisory and Control System……………GUO Shengjun, ZHENG Xiaoming, CHEN Yunyu(3·29)

由于N分频的Σ-Δ调制器速度的限制fPHD最大为32 MHz。 FRAC取0到225-1, D、T取0或1,R取1到32, INT可取23到4095,通过ADI公司设计的 ADF4157 Evaluation Software ADF_FRAC_REC3[6]软件进行 R, INT和各个分频器合理的设置。由于fREF为181.44 MHz由AD9516时钟分配器输出, R选32, fPHD=2.835 MHz, D取0, T取1。

将上述数据都转化为十六进制数可得到其配置数据。最终将外部VCO输出的时钟信号,通过环路滤波器输入到数字预失真系统的上下变频模块作为本振时钟。

2.3 测试结果

2.3.1 ADF4157相位噪声仿真

相位噪声是影响频率合成器性能的重要指标[7],主要来自锁相环各组成部分的相位噪声,分别为VCO相位噪声,参考输入频率相位噪声, PLL芯片相位噪声,环路滤波器相位噪声。根据数字预失真系统上下变频本振频率要求, VCO输出频率2 482.44 MHz,参考输入频率为181.44 MHZ, 鉴相频率2.835 MHz,由于VCO控制电压(14 V)超出了Vp电压(5 V),所以锁相环环路滤波器采用有源滤波器,放大器为 OP184, 环路带宽选择为84 kHz,VCO选择 SCD-160(UMX-160-D16)通过 ADIsim-PLL[8]软件仿真如图4。

图4 相位噪声

可以看出,在低的偏离频率处,参考源的噪声是频率合成器输出噪声的主要来源,在高的偏离频率处, VCO相位噪声成为影响频率合成器总的相位噪声主要因素,在10 kHz时总的相位噪声为-89.256 0 dBc/Hz,性能较好。

影响锁相环频率合成器锁定时间最主要的因素是环路带宽和相位裕量。环路带宽越宽锁定时间越快,但其滤波效果差。 ADF4157在参考输入频率为181.44 MHz,锁相环VCO输出2 482.44 MHz,鉴相频率为2.835 MHz,环路带宽选择为84 kHz,相位裕量47°,在45.54 μs的时候,锁相环基本上达到锁定,通过ADIsimPLL软件仿真如图5。

图5 84 kHz时锁定时间

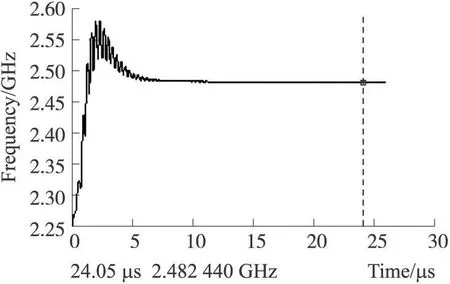

在图6中环路带宽为200 kHz其他条件不变,24.05 μs的时候,锁相环基本达到锁定。进一步证明环路带宽越宽锁定时间越快,但其滤波效果更差。

图6 200 kHz时锁定时间

2.3.3 ADF4157输出频谱图

采用此本振频率时钟方案,系统整体性能也较为理想, PLL频率合成器ADF4157产生的本振频率经过频谱分析仪测试频率合成器输出信号,输出信号频率为2 482.44 MHz,信号功率为-2.5 dBm左右,在40 MHz的窄带范围内没有明显的杂散存在,满足预失真系统上下变频本振信号频率要求,经过调试匹配等优化措施输出频谱图如图7。

图7 ADF4157输出频谱图

2.3.4 时钟板实物图

我们采用Cadence Allegro PCB Editor15.5绘制出整个时钟方案的PCB图[9],时钟板为4层板,顶层和底层是信号层,中间两层是地层和电源层,鉴于时钟线的布线要求,时钟线应尽量短而粗,采用差分走线,保证信号完整性[10]。经过合理布局,绘制的PCB电路图如图8。

图8 时钟方案实际PCB图

3 结束语

锁相式频率合成器是现代在应用最广泛的一种频率合成器,而分数数字锁相频率合成技术作为一种很有前途的锁相频率合成技术,备受大家的关注,本文介绍了基于FNPLL的ADF4157数字预失真系统本振频率以及相应的时钟方案设计,确保预失真系统信号质量。 ADF4157具有低的相位噪声,更高的频率分辨率,快速锁定,在参考输入频率不变情况下,比一般单环NPLL具有更小的步进变化等特点,对今后的设计类似功能的频率合成器具有很高的参考价值。

[ 1] ADF4157 DataSheet[ R] .Analog Devices Inc, 2007.

[ 2] AD 9549 DataSheet[R] .Analog Devices Inc, 2007.

[ 3] ADI公司的AD 9516用户手册[S].2007.

[ 4] ADF4106 DataSheet[ R] .Analog Devices Inc, 2005.

[ 5] ADF4360 DataSheet[ R] .Analog Devices Inc, 2006.

[ 6]ADF4157 Evaluation Software[ EB/OL] .http://www.analog.com/en/rfif-components/pll-synthesizersvcos/products/eb_PLL_download_software/fca.htm l.

[ 7] 张福洪,陶士杰,栾慎吉.锁相式频率合成器相位噪声分析与设计[ J] .电子器件, 2009, 32(3):6.

[ 8] ADIsimPLL Version 3.1Software[ EB/OL] .http://www.analog.com/en/rfif-components/products/ADIsimPLL_thankyou/fca.htm l.

[ 9] 周润景,袁伟亭,刘晓斌.Cadence PCB设计与制作[ M] .北京:电子工业出版社, 2005, 4.

[ 10] 布鲁克斯(美)著.刘雷波,赵岩,译.信号完整性问题和印制电路板设计[ M] .北京:机械工业出版社, 2005, 8.