基于FPGA的等精度频率计设计

2010-11-07罗磊赖万昌刘良成都理工大学核技术与自动化工程学院610059

罗磊 赖万昌 刘良 成都理工大学核技术与自动化工程学院 610059

基于FPGA的等精度频率计设计

罗磊 赖万昌 刘良 成都理工大学核技术与自动化工程学院 610059

1 引言

等精度测频方法是一种在直接测频方法基础上发展起来的测频方法,该方法测量精度高、频段宽,在频率测量中具有广泛的应用前景。FPGA由于其并行的执行结构及可编程型等优势使得其应用得到了飞速的发展。SPCE061A为凌阳科技新推出的unSP内核的高集成度,高性能十六位单片机。内置2路电流输出型的10bitDAC转换通道。

2 系统主要测量原理

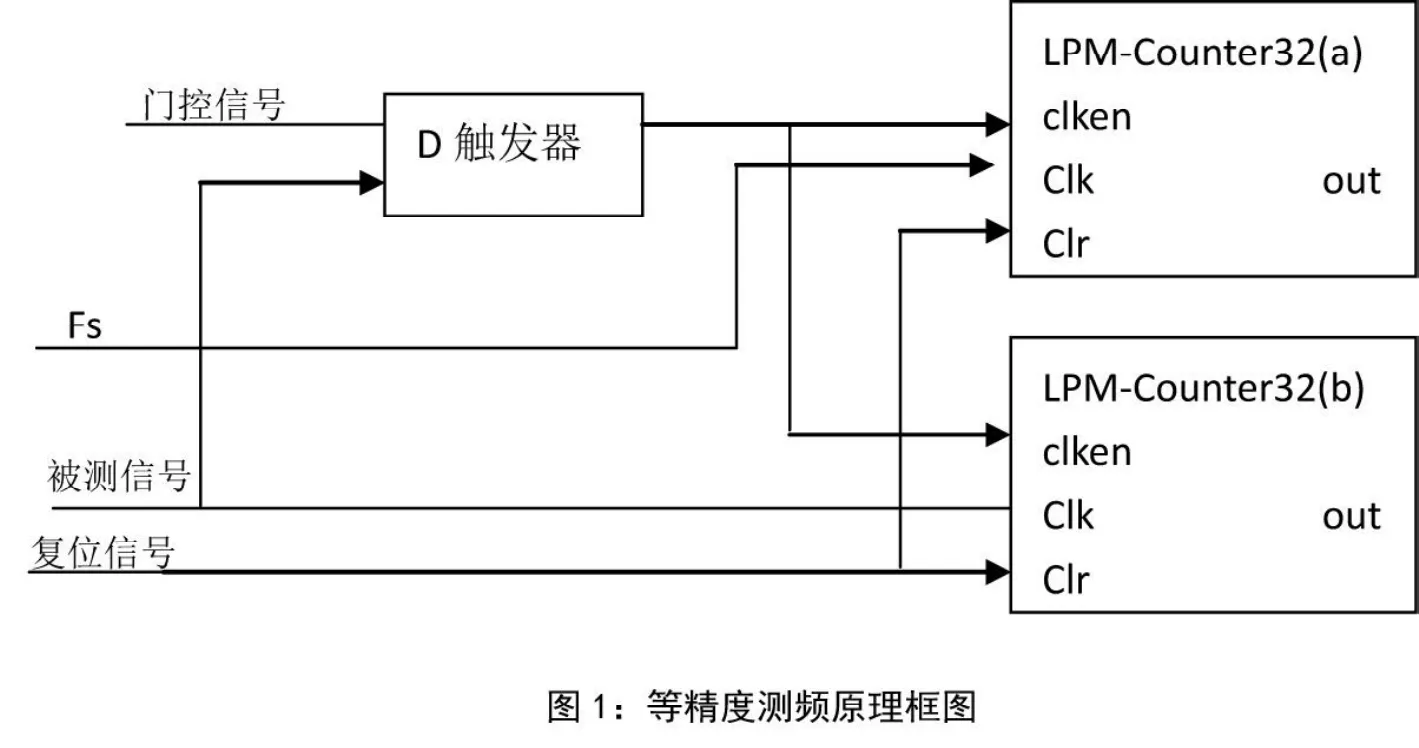

等精度测量原理:

等精度测频原理框图见图1。图中预置门控信号是一个宽度为Tpr的脉冲。它的初始值由初始化后的输入测量时间确定。L P M-C o u n t e r 32(a)和L P MCounter32(b)是两个可控计数器。标准频率信号fs从LPM-Counter32(a)的时钟输入端CLK输入;经整形后的被测信号从CNT2的时钟输入端CLK输入,设其实际频率为fxe,测量频率为fx。预置门控信号为高电平时,经整形后的被测信号的上升沿通过D触发器的Q端同时启动计数器LPM-Counter32(a)和LPM-Counter32 (b),分别对标准频率信号和整形后的被测信号同时计数。预置门控信号为低电平时,经整形后的被测信号上升沿使这两个计数器同时关闭。设在一次预置门时间Tpr中对被测信号的计数值为Nx,对标准频率信号的计数值为Ns,则下式成立:, 计数结束后读取LPM-Counter32(a)和LPMCounter32(b)的计数值,根据上式即可计算出被测信号的频率。在一次测量中,由于计数的起停时间都是由被测信号的上升沿触发的,因此,在Tpr时间内对fx的计数Nx没有误差,对fs的计数Ns最多相差一个脉冲Δ s。根据误差传递公式对上式微分,得相对测量误差:

从误差分析式中可以看出,其测量精度与被测频率无关。增大Tpr或fs可以减小测量误差,提高测量精度。

测周,正负脉宽原理:

测周与测正负脉宽都采用多次测量取平均值的放法。测量的测次数由始化后输入的测量次数n决定。被测信号的上升延使系统的计数开始。在测量次数达到后,读计数器二的值为Nx,被测量的时间t=,Fs为系统时钟频率。

测幅度原理:

由DAC1控制的比较器2不断的加大电压,当测量模块的计数为0时可得到输入脉冲的幅度。由与AD603属于压控放大器,在DAC2的输出确定后,其放大倍数便已确定。由此我们可计算出输入信号的准确幅度。

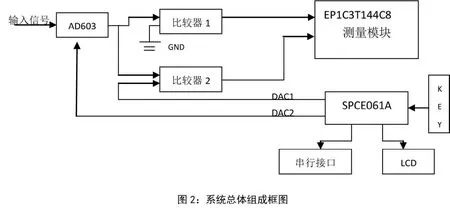

3.系统硬件

系统硬件总体组成框图,见图2。

输入信号通过AD603压控放大后,分两路进入快速比较器(tl3016),比较器1主要是进行信号的频率,周期,正负脉宽的测量。比较器2主要是进行幅度测量。LCD主要对测量的结果进行显示。按键key可以进行显示的控制。串行接口可以实现整个系统与PC机的通信。

4.系统软件

本系统的软件设计中主要是FPGA与单片机SPCE061A的软件设计。FPGA主要完成频率,周期,占空比等的测量。使用QuartusⅡ7.0集成环境进行程序编写。SPCE061A主要是负责进行按键的扫描与测量数据的显示。以下是FPGA内的主要模块。

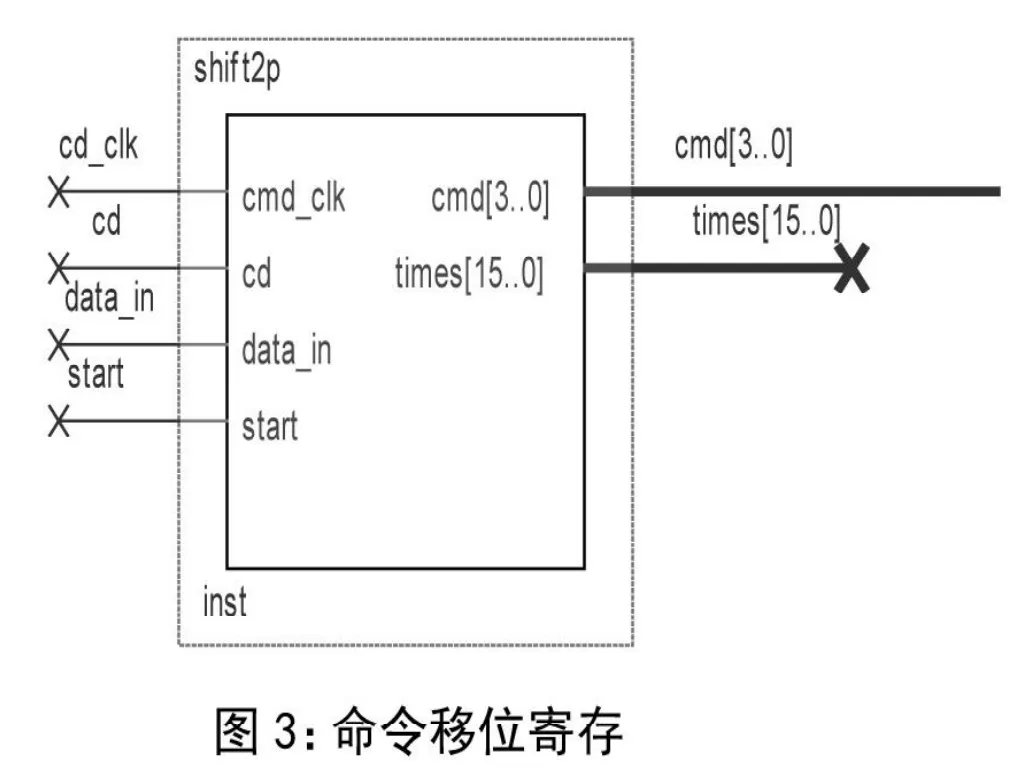

串行输入输出模块:

串行输入输出主要有移位寄存器构成,如图3,串行输入的命令主要通过时钟cd_clk进行输入。在20为命令输入完毕后只要启动start信号,命令便自动被加载到控制部分。数据的串行输出主要靠shift32实现(图4所示),cd_clk 为读取时钟,在上升延data_out输出数据。

控制模块与命令解析模块:

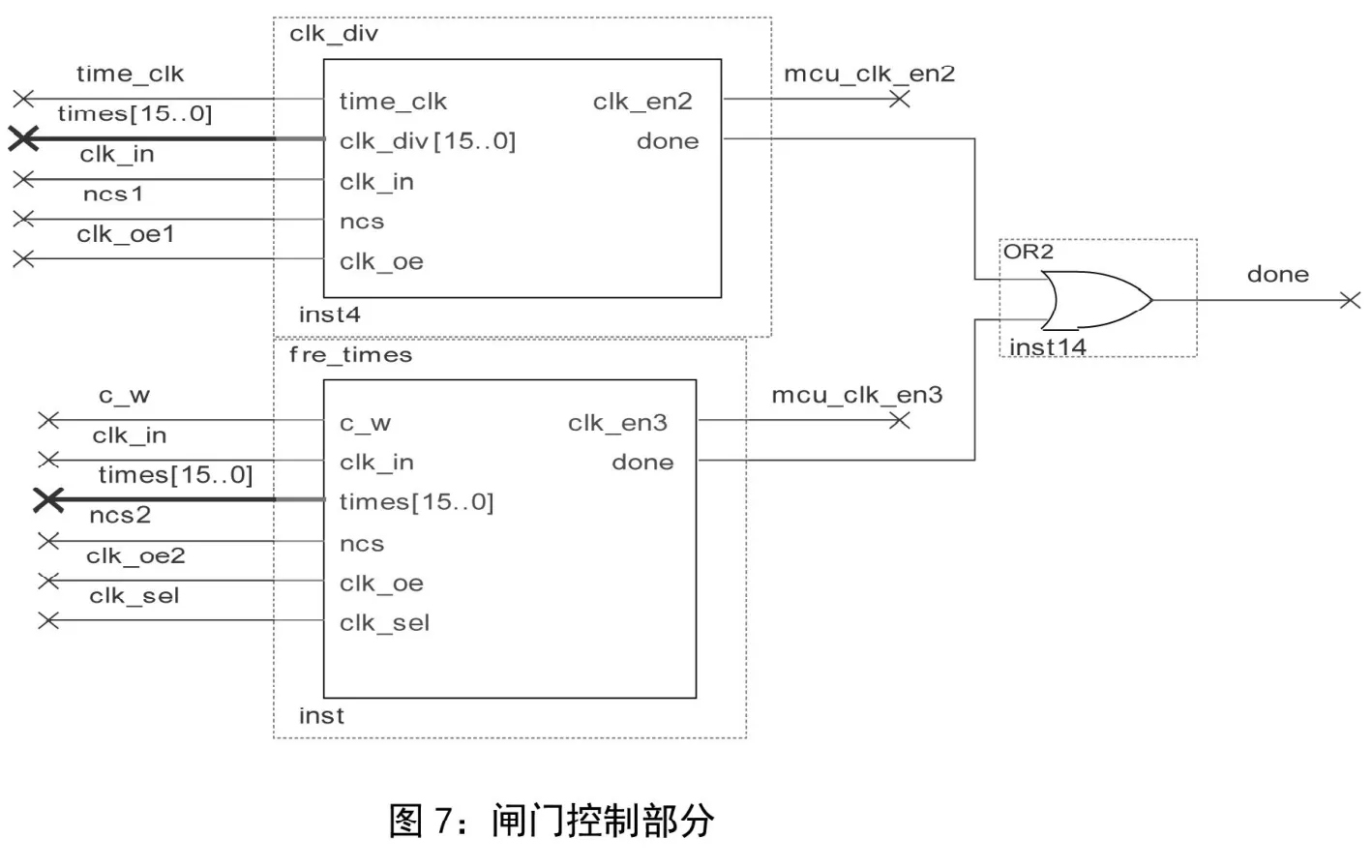

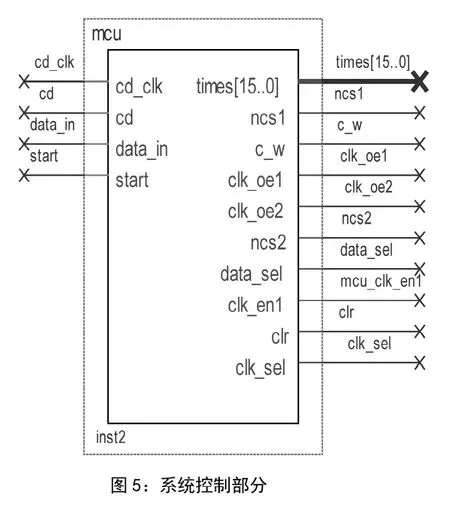

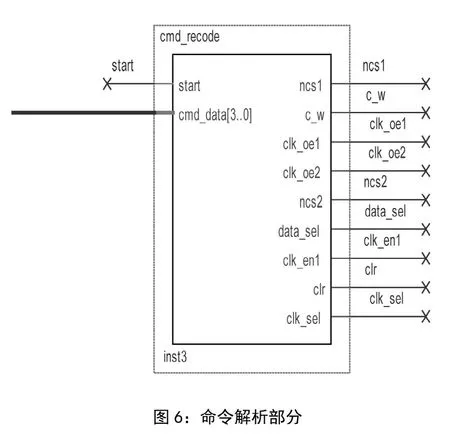

系统的控制部分由实体MCU实现,如图5,输入命令通过上面的移位寄存器后,有cmd_decode如图6进行解析。之后由MCU输出实际的控制信号。闸门控制部分如图7接到控制信号后分别控制两个计数器的使能端进行控制。

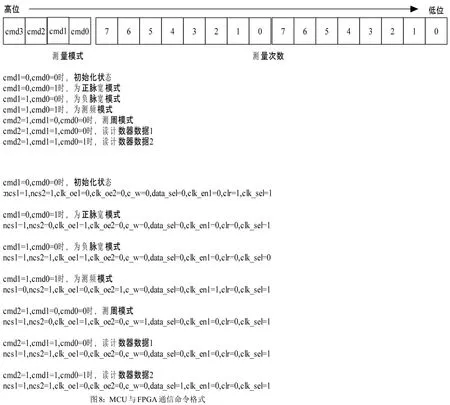

SPCE061A与FPGA主要的通信格式(图8)。

5.实验结果分析

测量仪器:1Gs/s

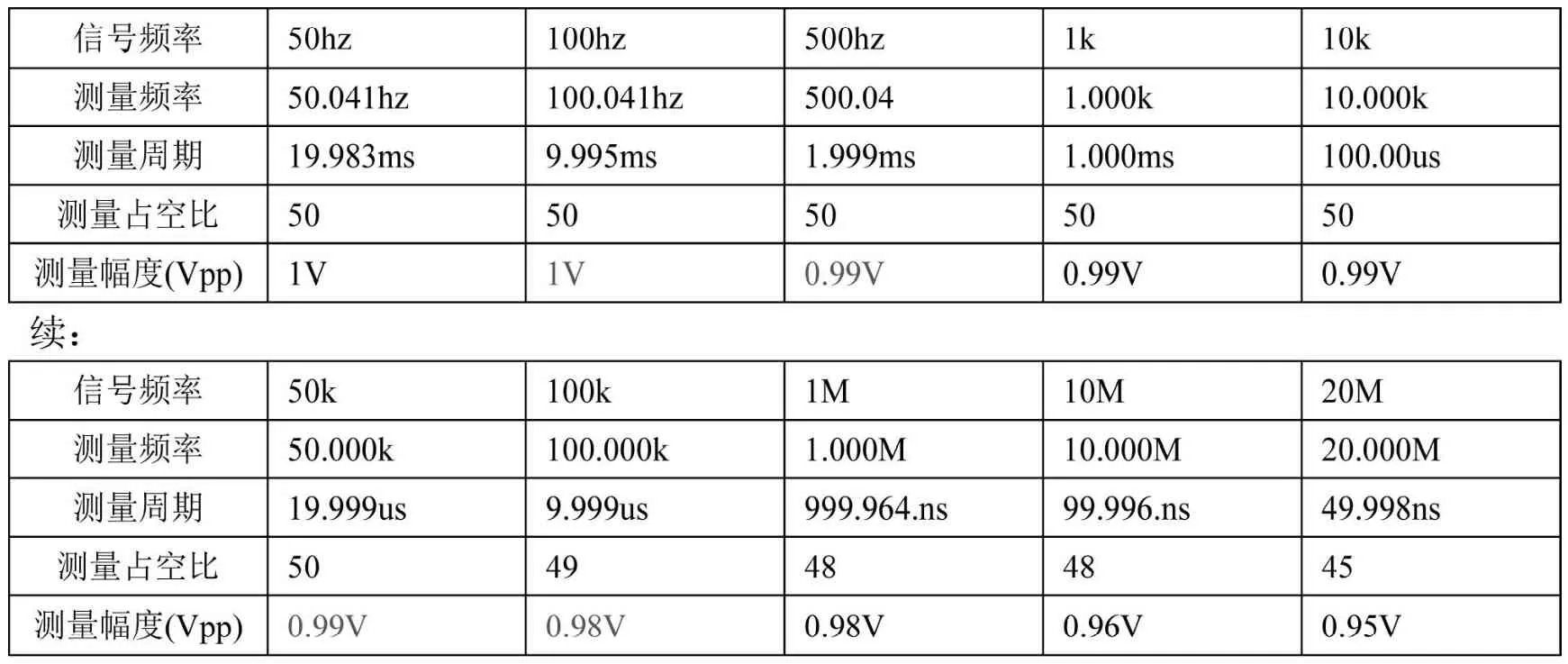

测试数据,见表5-1。

本系统中FPGA部分采用100M的晶振,理论测量频率可以达到100M。但由于ad603增益带宽最大为90M,限制了测量的带宽。由测量数据可以得出1~20M的测量误差最大在0.082%即0.041Hz。在频率接近100k时由于前级处理使信号失真,被测信号的占空比已经偏移。由于ad603增益带宽限制与噪声的干扰,幅度测量在500Hz时出现了10mv的偏移。想进一步提高占空比,幅度的测量范围,精度。可以进行屏蔽降低干扰,选用更高速的比较器。

6 结束语

本文采用FPGA 芯片EP1C3T144C8与SPCE061A对等精度频率计进行了系统的设计。设计中使用了V HDL 语言,经过实验验证设计中等精度测频是成功的,达到预期的结果。和传统的频率计相比,利用FPDA 设计的频率计简化了电路板设计,提高了系统设计的实用性和可靠性,实现数字系统的软件化,这是数字逻辑设计的趋势。

表5-1主要测试数据输入正弦波(1Vpp,占空比50%)

[1] 杨恒.FPGACPLD最新实用技术指南.清华大学出版社

[2] 潘松,王国冻编著.VHDL实用教程.电子科技大学出版社.

[3] 马彧,王丹利,王丽英.CPLDFPGA可编程逻辑器件实用教程.机械工业出版

[4] 褚振勇,齐亮,田红心.FPGA设计及应用(第二版),西安电子科技大学出版社

[5] 周润景,图雅,张丽敏.基于QuartusⅡ的FPGA/CPLD数字系统设计实例.电子工业出版社

[6] 李晓白,秦红磊.凌阳16位单片机C语言开发.北京航空航天大学出版社

[7] (美国)布朗等著.字逻辑与VHDL设计/VHDL与集成电路设计丛书.清华大学出版社

[8] www.21ic.com

Design of equal precision frequency meter with FPGA

Luo lei lai wanchang liu liang

College of Applied Nuclear Technology and Automation engineering, Chengdu University of Technology, chengdu 610059

频率的测量方法有:直接测量法,间接测量法,例如周期测频法、V-F转换法等。基于传统测频原理的频率计的测量精度将随被测信号频率的变化而降低。本设计中采用等精度测频方法与FPGA模块相结合,使得测量频率的范围与精度大大提高。同时FPGA中采用多次测量取平均值的方法完成周期,占空比的测量,系统采用双比较器与双DAC完成了被测信号的幅度的测量。SPCE061A单片机实现按键与测量结果在LCD上进行显示。

FPGA(EP1C3T144C8);SPCE061A;等精度测频;DAC

The frequency measurement is usually implemented in direct and indirect ways.Such as measuring period, converting voltage to frequency and so on.The frequency meter based on the traditional method is always inaccurate when measuring steep signal.The design enhanced the scale and Accuracy of frequency by integrating equal accuracy measurement and FPGA..In the same time, the design measures duty cycle and period of signal by choosing average data.This system achieves measurement of Amplitude of signal by using two comparators and two DAC.SPCE061A realizes the function of checking keys and displaying data on LCD.

FPGA(EP1C3T144C8);SPCE061A;equal precision frequency;DAC

10.3969/j.issn.1001-8972.2010.09.066

罗磊(1983-),男,四川广元,成都理工大学核技术应用研究生。