模数混合采集系统设计中的噪声抑制

2010-09-29何山

何山

(中国测试技术研究院 电子研究所,四川 成都 610021)

随着数字电路的飞速发展,智能化检测、测量、自动控制等模数混合系统的应用越来越广泛,速度也越来越快,对信号检测的精度要求也越来越高,但是随着数字信号频率的升高、数字边缘速率的增加,噪声问题却日趋严重,最新的8位模数转换器的采样率已超过3 GHz,11~14位模数转换器的采样速度已超过100 MHz,在采样率和信号频率如此之高的情况下,噪声成为一个必须关注的问题。如何尽可能降低混合信号电路的噪声,是大多数电路设计和布线工程师长期以来面临的一个难题[1]。

1 典型系统和影响系统噪声的主要因素

典型的模数混合采集系统如图1所示。可以设想,整个系统的噪声可以看作是信号通路上每个电路元素所贡献的噪声项的总和,因此总噪声的均方根值可由式(1)得 出[2]:

其中,Nm代表某个特定电路元素的噪声项,这些噪声项主要包括供电电源的噪声、模数转换器(ADC)本身的噪声、ADC输入电路的噪声、ADC输出电路的噪声、基准电压源的噪声、时钟电路的噪声和板级噪声。模数混合采集系统的噪声抑制就要从这几方面入手,对引起噪声干扰的几项逐个分析,将总的噪声抑制到最小。

图1 典型的模数混合采集系统

2 设计实例及具体降噪措施

在具体设计实例中,采用14位、10 MS/s采样率的模数转换器AD9240进行4路的模拟信号采集,电路主要由模/数转换器、模拟信号输入电路、量化数字信号输出电路、数据显示和存储电路、外部接口电路等部分组成,如图2所示。

下面逐项来讨论如何通过抑制各个部分的噪声来减小系统噪声。

图2 4路数据采集系统框图

2.1 ADC本身的噪声

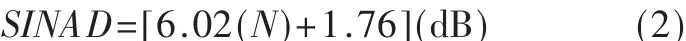

采用14位分辨率的模拟-数字转换器(ADC)未必意味着系统将具有14位的精度,很多时候,数据采集系统所表现出的性能往往远低于期望值,因此首先要根据芯片规格书选择合适的ADC。ADC的主要指标包括采集位数、积分非线性误差(INL)、微分非线性误差(DNL)、信噪比(SNR)、信噪失真比(SINAD)。INL和DNL是直流指标,跟噪声有关的关键指标是SNR和SINAD,SINAD定义为ADC满量程单频理想正弦波输入信号的有效值与ADC输出信号的奈奎斯特带宽内的全部其他频率分量(包括谐波分量,但不包括直流分量)的总有效值之比[3]。SNR类似于SINAD,只是它不包含谐波成分,因此,SNR总是好于SINAD。对于一个理想的ADC,

其中N是转换器的位数,对于理想的14位转换器,SINAD为86 dB。这个方程可重写为N的表达式,新的表达式揭示了能够获得的信息的位数与噪声的函数关系:

这个方程就是等效位数的定义,即ENOB。如果一个14位ADC在感兴趣的频率SINAD的最小值为74 dB,那么可获得的ENOB值为12,也就是说,由于转换器的噪声和失真,丢失了2位信息。

2.2 电源系统噪声抑制

稳定的电源是整个系统的基础,电源的纹波会直接带来采集的误差,现在一般都使用开关电源和DC/DC来供电,其纹波主要由开关纹波和高频噪声组成,如图3所示。

电源噪声的频谱大致为 10 kHz~30 MHz,最高可达150 MHz。特别是瞬态噪声干扰,其上升速度快、持续时间短、电压振幅度高、随机性强,对电路易产生严重干扰。具体可采取的措施有:

(1)加大电感和输出电容滤波,电感内电流波动大小和电感值成反比,输出纹波和输出电容值成反比,所以加大电感值和输出电容值可以减小纹波。但这种做法对减小纹波的作用是有限的,因为受体积限制,电感不会做得很大,输出电容增加到一定程度,对减小纹波就没有明显的效果了。

(2)接低压差线性稳压器(LDO)滤波,这是减少纹波和噪声最有效的方法,输出电压恒定,不需要改变原有的反馈系统,但也是成本最高、功耗最高的办法。对比图4的曲线和波形,可以看出对几百kHz的纹波,LDO的抑制效果非常好,但在高频范围内就不是十分理想了。

对于高频噪声,可以采取的措施有:

(1)在二极管上并电容C或RC。

(2)二极管后接电感,这也是常用的抑制高频噪声的方法,针对产生噪声的频率,选择合适的电感元件,同样能够有效地抑制噪声。

2.3 ADC输入电路

AD9240的模拟信号输入有单端输入和差分输入两种,本设计中采用将单路信号耦合为差分输入,因为差分输入可以对共模噪声有很好的抑制作用。ADC输入电路多采用运放直流耦合或变压器交流耦合方式,为输入信号提供增益、偏置和缓冲。一般来说,变压器耦合在噪声性能上要优于采用运放直流耦合,尤其是在信号频率比较高时更为明显。如果采用运放直流耦合,为了获得低的失真(THD),记得驱动ADC的运放增益带宽积要求大于100倍采样速率,另外,在ADC输入前加 1个RC滤波器可以滤除噪声,抗混叠,并为ADC的转换产生的瞬态能量提供缓冲。加RC滤波并不会像很多人想的那样影响ADC的性能,相反,如果时间常数选择得当,还会提高它的性能和稳定性。ADC一般有采样电路,外部的电容可以在每次采样的时候提供快速的充放电,提高它的精度。一般ADC外部都会有运放来驱动,所以电容不会影响保持时间,如图5所示。

图5 ADC输入端的RC滤波

2.4 ADC输出电路

ADC的输出驱动器根据输出的电容改变动态电源电流大小。因此,如果不对输出驱动器电源进行去耦,输出驱动器电源上引起的噪声可能会干扰其他模拟电路,这就需要对ADC的输出驱动器电源进行充分的去耦处理。另外,ADC数据输出线上的噪声会通过这些寄生电容耦合到模拟输入端,导致ADC的SNR和有效位数ENOB下降。若要降低噪声,当务之急就是把输出总线电容最小化,以便以较小的电流对该电容进行充电,即降低ADC输出端的负载电容和输出电流。具体的做法是在ADC数据输出端接一个锁存器,可避免将其直接连在数据总线上,有效限制了其输出端的负载电容。另外,在ADC每一个数据输出端都串联一个电阻,可限制其输出电流。本设计采用74LVTH162374作为AD9240的输出数据锁存器,同时,每一个数据输出端都串联一个220 Ω的电阻。

2.5 电压基准

引起数据转换系统噪声的另一个因素是电压基准的问题。采用内部或外部基准的ADC的一个最大潜在噪声源是参考电压,很多情况下,内置于芯片内部的基准通常都没有足够严格的规格,尽管转换器可以有较高的分辨率,但是,大多数模数转换器都只具有适用于小于13位分辨率应用的内部基准。精密外部电压基准与片上带隙电压基准相比,具有较低的温度系数、热迟滞和长期漂移。所以在需要高精度(14位或16位ADC)的应用中,通常需要一个外部精密电压基准[4-5]。在本电路设计中,采用了AD780来作为外部电压基准。

2.6 时钟电路

时钟的质量直接影响到ADC的孔径抖动,孔径抖动(或称孔径误差)是指相邻两次采样的孔径时间的偏差,而孔径时间又称孔径延迟时间,是指在保持命令发出之后到ADC采样保持放大器完全打开采样开关所需的时间,即ADC采样发出命令到采样实际开始的时间。孔径抖动造成了信号的非均匀采样,引起了误差。设ADC满量程电压为±1 V,输入信号为:

孔径抖动的方差值为tjitter,由此引入的信噪比为:

孔径抖动与SNR的关系如图6所示。

由图6可以看到,输入信号频率每增加10倍,由于孔径抖动引起的信噪比就恶化20dB,因此,为降低ADC的孔径抖动对SNR的影响,必须降低采样时钟的抖动,应使用低相位噪声的石英晶体振荡器作为采样时钟发生器。如果采样时钟不需可调,则可直接用晶体振荡器,并采用低抖动的时钟驱动。具体时钟电路如图7所示。

图7 时钟电路

2.7 电路板的布局布线

混合信号电路PCB的设计很复杂,元器件的布局、布线以及电源和地线的处理将直接影响到电路的噪声性能和电磁兼容性能。在实际应用中主要采取了如下几个措施[6]。

(1)将模拟电路和数字电路分开布局,ADC跨分区放置;

(2)避免在ADC芯片下走数字线,以免将噪声耦合到芯片上;

(3)所有旁路电容应尽可能靠近器件安装,并与器件位于电路板的同侧;

(4)采用电源平面、地平面;

(5)模拟电源和数字电源相互隔离;

(6)模拟地和数字地相互独立,并在数字回地电流小的地方进行单点共地连接;

(7)如果数字电路的噪声和电流比较大,应该将ADC的数字地也就近接到模拟地上;

(8)为减小信号线上的分布电阻、电容和电感,应尽量缩短导线长度并增大导线之间的距离;

(9)模拟输入应是均衡的。也就是说,从驱动源(放大器和滤波器等)到差分输入端的走线应该等长,元件布局应相互对称,这样,所有的寄生参数才会均衡。走线长度应尽可能短,以降低电感、减小干扰;

(10)时钟输入与模拟输入和基准一样敏感。应像对待模拟信号那样对时待时钟信号。避免将时钟线靠近任何数字输出信号线。如果板上有多个ADC,则需隔离时钟线对,以尽量降低噪声并减小来自其他ADC的干扰。时钟信号线不应与数字输出信号线布在同一层。如果布在同一层,应尽量使这两类信号线之间保持较大间距,并在这两类信号线之间布隔离的GND(地线),以降低可能产生的任何耦合。

随着数字信号频率的升高、数字边缘速率的增加,噪声问题也日趋严重,如何尽可能降低模数混合采集电路的噪声,是大多数电路设计和布线工程师长期以来面临的一个难题。本文从典型的模数混合采集系统和影响系统噪声的各种因素入手,详细分析了引起模数混合采集系统噪声干扰的主要因素,针对每个环节提出了切实可行的抑制噪声的具体方法和措施,有效地抑制了模数混合系统的噪声,提升了系统的性能。

[1]GRAY N.优化混合信号电路的抗噪性能[J].半导体技术,2006(10):82-85.

[2]Maxim.ADC中的ABC:理解ADC误差对系统性能的影响.Maxim Application Note 1600,2002,2.

[3]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[4]Maxim.多ADC系统的基准电压设计.Maxim Application Note 1735,2002,6.

[5]Maxim.Selecting the optimum voltage reference.Maxim Application Note 2879,2003,11.

[6]Maxim.Schematic and layout guidelines for high-speed data converters.Maxim Application Note 3491,2005,3.