相控阵天线集成技术

2010-09-26

(中国西南电子技术研究所,成都 610036)

1 引 言

早期的相控阵雷达用于战略探测、跟踪与预警,工作频率较低,整个系统体积巨大,成本高昂。随着微电子与计算机技术的发展,相控阵系统逐渐应用于战术层面,如战斗机、直升机、无人机、精确制导等领域,工作频段通常是X、Ku与Ka频段。这些武器平台空间狭小,自身价值有限或者雷达实际使用寿命很短,但是相控阵系统的战术、技术指标要求却依然很高:波束扫描范围宽,指向精度高,具备多目标精确跟踪能力;重量轻,尺寸紧凑,功耗少;生产目标成本低。大型天基通信与雷达探测也日益强调采用相控阵技术,成本虽非首要因素,但是体积、重量与功耗要求却非常苛刻。民用智能通信天线尤其关注成本控制。

相控阵天线是相控阵系统的核心部分,特别是二维有源相控阵天线,其集成水平决定了整个系统的性能与成本,工作频率愈高,每个阵元的面积(约λ2/4)愈小,集成度要求愈高。

传统的有源相控阵天线,当应用平台或者功能项目变化,需要扩大或者缩小阵列天线的口径时,除了要增加或减少T/R组件的数量,还需要重新设计相控阵其它分系统,以适应射频、中频、数字信号与电源接口数量以及负荷能力的变化。

开放式可扩展阵列天线,以子阵模块为基本单元,不仅封装了多个相控阵天线通道,还集成了相控阵其它分系统(如波束形成与幅相校正网络、电源、波束控制、频率源、波形产生以及冷却系统)的部分功能,大幅度减少接口类型与数量,实现模块化、通用化,提高可扩展性能。这时候,每个子阵都是一个高度集成的小型相控阵天线。

过去10年间,单片微波集成电路迅速发展,在相控阵天线上得到广泛应用,提高了系统可靠性,减小了体积,降低了重量与成本。但是二维有源相控阵仍然是代价不菲的,迄今为止,仅仅美国的战斗机部分换装了有源相控阵雷达。

相控阵天线集成阵列结构有砖块式与瓦片式两种,电路集成技术由多芯片模块(MCM)向多功能集成芯片与晶圆级单片相控阵发展。

2 阵列结构与封装

将多个通道在电路与结构上封装为一个整体,作为阵列装配的基础积木块或在线可更换单元(LRU),是相控阵天线最基本的集成手段。基础阵列模块通常集成了多个T/R组件、射频馈电网络、控制与直流偏置等电路,如果还集成了天线辐射阵元,可称为子阵。

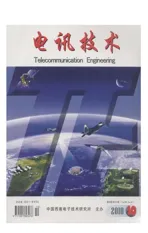

相控阵天线集成的阵列结构有两种:基于砖块式线子阵的纵向集成横向组装;基于瓦片式面子阵的横向集成纵向组装[1],如图1所示[2]。

图1 砖块式与瓦片式集成子阵Fig.1 Brick and tile type sub-array

通常,砖块式用于较高频段,瓦片式用于较低频段,但是还要兼顾相控阵天线的用途与技术参数。脉冲工作的雷达系统波束窄,阵元数多且间距小,功耗大,系统散热要求苛刻,砖块式设计相对容易;通信系统的发射功率要求不高,波束比较宽,阵元数少且间距宽,瓦片式集成难度比较小;而共形相控阵天线必须采用瓦片式集成技术。

通过子阵模块集成,能够大幅度减少相控阵天线与波束形成网络、控制电路、电源组件等分系统之间的信号互联,降低损耗,提高效率,提高电磁兼容水平;减少机械装配结构件,降低重量;简化封装与装配程序,提高相控阵天线的测试性、维修性与可扩展性。在较高的频段,还有利于降低机械公差要求,实现更小的阵元间距,扩大波束无栅瓣扫描范围。

2.1 砖块式

砖块式子阵是最流行的阵列结构,元器件放置方向垂直于相控阵天线孔径平面,辐射阵元通常采用偶极子或锥形槽天线;其电路与结构设计遵循传统的分系统概念,信号互联、测试与封装技术继承性好,缺点是纵向尺寸大;较高的频段,阵元间距小,有利于晶圆级单片集成。

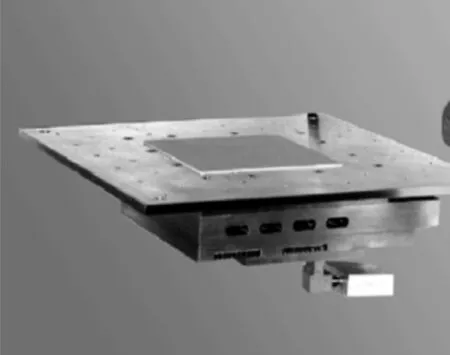

砖块式子阵集成的典型例子是AN/APG-77有源相控阵机载雷达、雷声公司开发的35 GHz低成本相控阵导引头[3]以及俄罗斯的全球空间监视雷达[4],如图2所示。

(a)X频段砖块式子阵

(b)X频段瓦片式子阵

(c)诺格公司Ka频段相控阵天线

(d)雷声公司Ka频段相控阵天线

图2 X频段子阵与Ka频段相控阵天线

Fig.2 X-band sub-array and Ka-band phased array

2.2 瓦片式

瓦片式集成的子阵模块采用分层结构,将多个通道相同功能的芯片或电路集成在数个平行放置的瓦片上,然后垂直互联,辐射阵元多采用微带贴片天线。有源相控阵天线的基本瓦片层包括[5]GaAs层、冷却层、DC与控制电路层、RF馈电层和辐射阵元层。在较低的频段,瓦片式也能支持多通道晶圆级芯片集成,如将整个平面子阵的部分微波电路集成在一个GaAs晶圆上。

瓦片式子阵利用高密度组装技术,大幅度减小了纵向高度、重量与成本,但是需要新颖的互联技术,完成各层之间、子阵模块与信号分配背板之间的信号交换。此外,还需要处理好毗邻器件可能发生的耦合效应、中间层热设计、测试性与维修性设计。

瓦片式子阵集成始于军用卫星通信终端设计。20世纪80年代后期开发测试了多个晶圆级集成的20 GHz接收与44 GHz发射有源子阵,并设计了多层集成的机载智能蒙皮有源相控阵天线结构[6]。由于技术不成熟,波音公司开发的91元44 GHz发射阵最终改用多芯片微组装工艺与多通道密布结构,三角形栅格,阵元发射功率0.2 W[7]。

在DARPA与NASA的支持下,美国多家公司先后研究了多个频段的瓦片式集成子阵。西屋公司采用晶圆级集成技术,开发了4×4瓦片式子阵,每个通道5位幅度、6位相位控制,发射带宽6~12 GHz,发射功率0.5 W;接收带宽4~12 GHz,噪声系数小于7 dB,增益大于20 dB[5]。德州仪器开发的Ka频段4×4发射子阵,阵元间距0.8 λ,4位PIN二极管移相器插损4.5 dB,阵元发射功率100 mW,馈电网络的插损5 dB[2]。休斯公司开发的X频段瓦片式4元有源模块,采用多层氮化铝基板,共面波导传输线和毛纽扣连接器,倒装单片微波集成电路(MMICs)。和砖块式4元模块相比,体积、重量与生产成本分别降低了86%、67%、76%[8]。

法国Thales公司开发的8×8数字接收瓦片模块,包括电源、控制以及光学接口等组件,整个厚度100 mm,重量不到8 kg[9]。

针对大型天基相控阵应用,加拿大学者设计的瓦片式集成结构,每个8×8子阵由3层瓦片组成:辐射阵元、MEMS移相器与功分器、T/R组件[10]。

2.3 封装技术

封装给模块中的元器件提供物理支撑,完成RF、DC偏置与控制信号的互联以及电磁屏蔽功能,提供外部接口、热传导路径。

目前,子阵模块成熟的封装技术是多芯片微组装。基板材料与工艺有多种,常用的包括印制电路板(PCB)表面贴装,低温、高温共烧陶瓷(LTCC,HTCC),薄膜与厚膜多层陶瓷等,其发展趋势是工艺性好,封装面积大,价格低廉。

LTCC能够在复杂的三维结构中高密度集成电阻、电容和电感等无源器件,减少表贴元件以及互联,降低多芯片微组装的复杂性,提高可靠性;LTCC高频特性优良,基片介电常数范围宽,线宽与间距小,是微波毫米波电路设计与制造的主流方向。

印制电路工艺成本低,易于集成表面贴装元件;封装面积大,易于大量生产。

德国IMST为智能天线终端开发的Ka频段8×8瓦片式LTCC模块,共16层,不仅集成了混频器、滤波器与功放,还集成了液体冷却系统。

雷声公司采用商业PCB技术,开发的X频段16×8模块化可扩展接收子阵,集成了SiGe控制芯片、GaAs LNA与开关、贴片天线、极化馈电网络、波束形成、DC偏置与数字控制电路,整个厚度仅仅5.3 mm[11]。

RF MEMS器件具有插损低、功耗少、工作频带宽等一系列优点,在相控阵天线中应用前景光明。适于MEMS相控阵集成的微加工技术、与PCB工艺相容的MEMS技术也在不断发展中[12]。

Arkansas大学在高阻硅基片上集成了Ku频段4元线阵[13],采用微带贴片天线,BaSrTiO3薄膜铁电移相器,15 GHz频点处最大插损2.6 dB。

3 多功能芯片

多芯片微组装采用微型焊接与封装工艺,通过多层布线基板,将多块裸芯片与各种片式电路元件组装起来,实现高密度互连,是当前相控阵天线集成的主流技术。但是,在低成本与高频段有源相控阵天线应用中,存在3个问题:一是芯片数量多,T/R组件通常有5~9个MMICs,芯片成本约占整个相控阵天线的25%[14],芯片互联要耗用大量的辅助材料,微组装工序繁多,不利于降低成本;二是单个芯片的指标要求高,考虑到多芯片组装连线的损耗、电磁耦合效应,单个芯片的指标必须有适当的余量;三是高频段相控阵天线没有足够的空间来安置过多的芯片。

如果在一个芯片里集成低噪放、功放、射频开关与移相器,甚至控制电路,不仅能够大大减少相控阵天线的芯片数目,减少芯片互联工序与连线,还能够从整体上优化设计各个功能单元的指标要求,提高整个功能模块的综合性能。

令Rmax、N、Pe、Ae、λ、σT、Smin、L分别表示最大作用距离、阵元数、每个阵元的发射功率、每个阵元的等效口径面积、波长、目标截面积、最小可检测信号与系统损耗,对于大型相控阵天线,考察雷达方程:

(1)

对于给定的功率孔径积,适当增加阵元数,可以大幅度降低每个阵元的发射功率,从而减小全部T/R组件的直流功耗,降低天线成本[15]。此时不需要高功率放大器,有可能将T/R组件的全部功能集成在一个MMIC上,即单片T/R组件。

3.1 X频段多功能芯片

传统的多芯片T/R组件,发射与接收放大器选用不同的芯片工艺,独立优化各自的性能,实现最大发射功率(或效率)与最小接收噪声系数。单片T/R的放大器采用同样的工艺技术,需要综合分配指标。

2001年,DARPA发起大型经济阵列项目,要用一个MMIC完成X频段T/R组件功能,以消除多芯片互联的成本[16]。3个合同商都考虑接收发射共用一个放大器,以减小芯片面积。朗讯公司选择了IBM 5HP SiGe工艺;诺格公司选择了InP HEMT工艺,功耗低,噪声系数小;雷声公司选择了GaAs pHEMT工艺,发射效率较高。

此前,荷兰TNO物理与电子实验室为天基SAR应用开发了一款X频段T/R芯片[17],该芯片集成了7位衰减器、7位移相器、射频开关、LNA、中功率放大器、数据串并转换以及电平变换功能,采用OMMIC ED02AH 0.2 μm pHEMT工艺,芯片尺寸4.2 mm×4.4 mm,噪声系数为8~10 dB,发射功率为14 dBm。2004年,该实验室报道了新的6位幅度相位控制T/R芯片[18],提高了发射功率,大幅度降低了噪声系数;芯片功耗1.2 W,采用UMS公司0.25 μm pHEMT工艺,芯片尺寸略大。

针对MEMS无源瓦片子阵应用,加拿大学者将3位MEMS移相器与功分器垂直无孔集成在一个双面晶圆上。开关线移相器采用4个级联的SP3T开关,插损2.5±0.2 dB。芯片尺寸22 mm×11 mm,152.4 mm的晶圆可以布置64个[10]。

3.2 Ka频段多功能芯片

2002年,DARPA发起的MEMS相控阵导引头项目遭遇到技术瓶颈,在成功开发出X频段单片T/R以后,该项目转而支持基于单片T/R组件的有源相控阵方案,要求开发152.4 mm直径的35 GHz有源相控阵天线,发射峰值功率30 W,相控阵天线的目标成本是19 000美元。

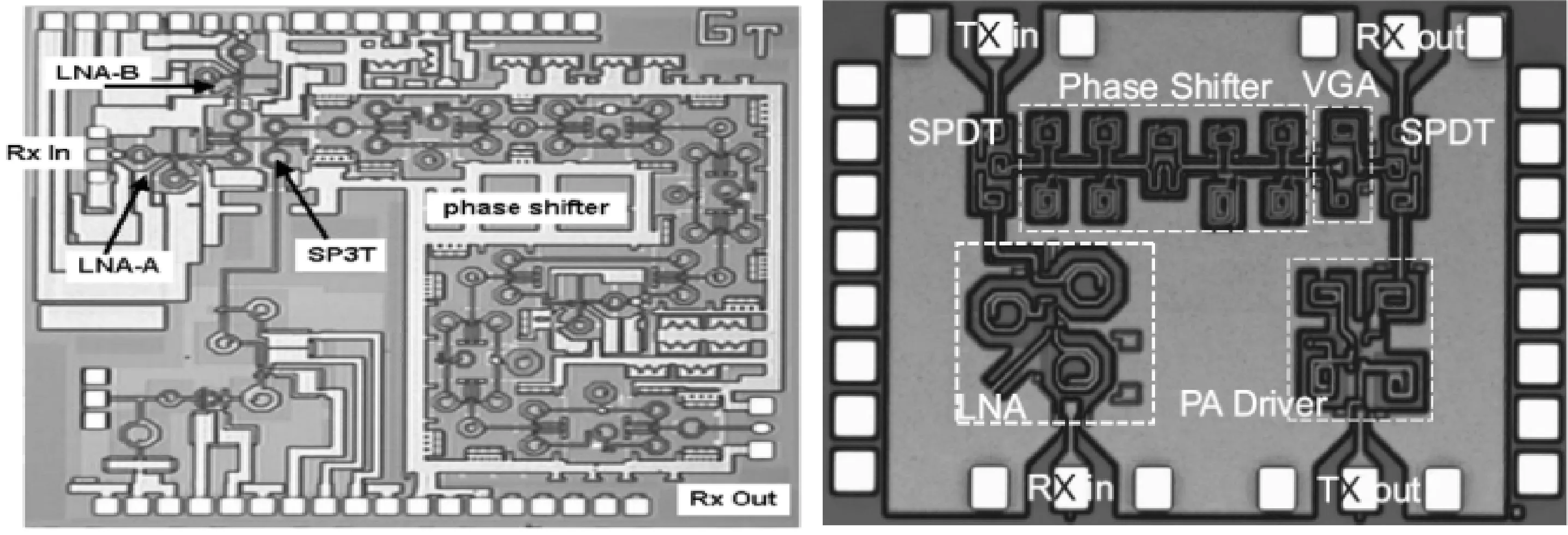

诺格与雷声公司先后开发出Ka频段二维有源相控阵天线[19,3],前者采用了瓦片式结构,后者采用砖块式结构,如图2所示。

雷声公司开发的单片T/R组件,发射功率40 mW,成本30美元。诺格公司开发的Ka频段共源双向功放芯片,接收与发射各两级放大,另外两个管子用做收发开关,接收增益17 dB,噪声系数4 dB;发射功率17 dBm,增益13 dB。如果采用共栅设计,双向功放仅仅需要两个管子,但是增益较低,发射功率较小[20],如图3所示。

(a)35 GHz单片T/R组件 (b)Ka频段双向功放

(c)SiCe X频段T/R芯片 (b)SiGe Ka频段T/R芯片图3 X与Ka频段多功能芯片Fig.3 X- and Ka-band multi-function chips

3.3 基于SiGe的多功能芯片

虽然发射功率与噪声系数指标上不能比肩GaAs,但因为用Si做衬底,SiGe可以使用更大尺寸的晶圆,并支持商用工艺,芯片能够以很低成本高密度集成更多的功能,如微波功放、低噪放、A/D以及逻辑控制电路,器件成本要比GaAs低一个数量级。

在X频段,SiGe BiCMOS可以比较经济地输出0.5~2 W功率,单片集成T/R组件可以在大型阵列中直接应用,再配合一个功放构成双芯片T/R组件,能输出更高的功率。

针对地基、机载、临近空间与天基雷达应用,Georgia Tech Research Institute设计了一款X频段T/R芯片[21]:2 GHz带宽,集成5位移相器,两路LNA,一路发射功放以及SP3T开关。预期噪声系数3.6 dB,接收增益12 dB,功耗34 mW;发射功率50 mW,功耗400 mW。实际完成的接收部分实测噪声系数4.1 dB,芯片尺寸3.8 mm×3.5 mm[15]。

Michigan大学和California大学的研究人员开发的Ka频段单片T/R组件[22],用于卫星通信与防务,芯片尺寸0.93 mm×1.33 mm,3位幅度与4位相位控制。所有放大器采用0.12 μm SiGe晶体管,开关与移相器采用0.12 μm CMOS晶体管(移相器插损12.5 dB)。该芯片接收增益19 dB,噪声系数4~5 dB;发射增益10 dB,发射功率5.5 dBm。增益与相位RMS误差小于0.6 dB与7°,发射功耗58 mW,接收功耗29 mW,如图3所示。

4 晶圆级集成

晶圆级集成概念提出迄今已逾20多年,随着商用微电子技术的迅猛发展,晶圆级的相控阵天线集成技术逐步走向实用。

Thales公司研制的W频段有源相控阵导引头天线[23],使用两个101.6 mm的晶圆,一个集成偶极子天线和PIN二极管移相器,另一个集成驱动电路,有3 000多个单元,波束宽度2°,扫描范围±45°。

4.1 射频多通道集成

多通道集成是将多个相控阵天线通道的同一频段电路(主要是射频)集成在一个晶圆上,如高功率放大器集成为一层,LNA和增益放大器集成为另一层。

瓦片式结构的相控阵天线,如果阵元间距比较大,或者为了提高天线的工作带宽,常常将辐射阵元单列出来,与射频电路不集成在一个晶圆上。

Rome航空研发中心开发的44 GHz有源发射子阵,集成了2×2通道的园极化微带贴片天线、变容二极管移相器、功分器、两级FET功率放大器。20 GHz接收子阵规模是4×4[6]。西屋公司在一个晶圆上集成了两个4×4通道的T/R组件,每个组件还设计了冗余电路[5]。

Michigan大学在76.2 mm晶圆上集成了一个8元MEMS无源电扫阵[24]。电路包括分布式MEMS传输线移相器、功分器、缝隙耦合微带天线、过渡以及偏置焊盘。工作频率38 GHz,噪声系数6 dB,最大发射功率4 W。

4.2 单片相控阵

CMOS集成电路成本低,功耗小。计算机集成电路的快速发展促进了射频 CMOS半导体器件的研究与应用,2004年报道了104 GHz的CMOS压控振荡器。

Si CMOS与SiGe BiCMOS单片集成相控阵是当前的研究热点。与SiGe相比,Si CMOS能集成更多的功能,从射频、中频到基带,包括微处理器、存储器、D/A与A/D、可调滤波器都能在一个硅片上实现。

针对通信、测距、定位与遥感应用,California理工学院研究了24 GHz硅集成相控阵[25]。该硅片集成了射频低噪放(接收阵)、功放(发射阵)、射频与中频混频器、三阶频率综合锁相环、16种相位输出的本振压控振荡器、移位寄存器、中频放大器等功能电路。4元发射阵列采用0.18 μm CMOS 工艺,尺寸6.8 mm×2.1 mm,功放饱和输出功率14 dBm,通道之间的隔离28 dB,3 dB带宽大于400 MHz。8元接收阵列采用0.18 μm SiGe BiCMOS工艺,尺寸3.5 mm×3.3 mm。单路噪声系数7.4 dB。两个阵列的功耗分别约为2 W与1 W。

California理工学院采用0.18 μm SiGe BiCMOS工艺,研制了6~18 GHz的相控接收阵列[26],其4位射频移相器由正交全通滤波器、译码器、数模转换与模拟有符号差分信号加法器组成。12 GHz处,每个通道接收增益约20 dB,噪声系数约4 dB。阵列尺寸2.2 mm×2.45 mm。

基于该射频移相原理,California大学还研制了Q频段(40~45 GHz)16元发射阵[27],每个通道增益12.5 dB,饱和发射功率-2.5 dBm,阵列尺寸2.6 mm×3.2 mm。

5 结束语

相控阵天线在最近十多年的发展过程中,半导体材料与工艺技术起着巨大的推动作用,并不断受惠于商用通信与计算机产业,单片微波集成电路已经成为相控阵天线的核心关键技术。要开发低成本、高频段与可扩展的相控阵天线,微波集成电路芯片研发必须走在系统研制的前面。特别地,考虑到国内的技术水平,要研制毫米波二维相控阵天线,开发多功能的单片集成电路是比较可行的途径。

参考文献:

[1] Griffin D W,Parfitt A J.Electromagnetic design aspects of packages for monolithic microwave integrated circuit-based arrays with integrated antenna ele-ments[J].IEEE Transactions on Antennas and Propagation, 1995,43(9):927-931.

[2] Sanzgirl S, Bostrom D,Pottenger W,et al.A hybrid tile approach for Ka band subarray modules[J].IEEE Transactions on Antennas and Propagation, 1995,43(9):953-959.

[3] Eli Brookner.Phased-array and radar break-throughs[C]//Proceedings of IEEE Radar Conference. Boston, MA:IEEE,2006:37-42.

[4] Tolkachev A A, Denisenko V V,Shishlov AV,et al.High gain antenna systems for millimeter wave radars with combined electronical and mechanical beam steering[C]//Proceedings of IEEE Symposium on Phased Array Systems and Technology. Boston, MA:IEEE,1996:266-271.

[5] Whicker L R.Active phased array technology using coplanar packaging technology[J].IEEE Transactions on Antenna and Propagation, 1995,43(9):949-952.

[6] Mcllvenna J F.Monolithic phased arrays for EHF communications terminals[J].Microwave Journal, 1988,31:113-125.

[7] Riemer D E.Packaging design of wide-angle phased-array antenna for frequencies above 20 GHz[J].IEEE Transactions on Antenna and Propagation, 1995,43(9):915-920.

[8] Mark S Hauhe,John J Wooldrige.High density packaging of X-band active array modules[J].IEEE Transactions on Components, Packaging, and Manufacturing Techno-logy(Part B), 1997,20(3):279-291.

[9] Odile Adrian.From AESA radar to digital radar for surface-based applications[C]//Proceedings of IEEE Radar Conference. Pasadena, CA:IEEE,2008:1-5.

[10] Al-Dahleh R,Mansour R R.A novel via-less vertical integration method for MEMS scanned phased array modules[C]//Proceedings of European Microwave Conference. Amsterdam:[s.n.],2008:96-99.

[11] Puzella A, Alm R.Air-cooled, active transmit/receive panel array[C]//Proceedings of IEEE Radar Conference.Rome:IEEE,2007:421-426.

[12] Ananth Sundaram,Maddela M,Ramadoss R,et al.MEMS-Based Electronically Steerable Antenna Array Fabricated Using PCB Technology[J].Journal of Microelectromechanical Systems, 2008,17(2):356-362.

[13] Taeksoo Ji, Yoon H,Abraham J K,et al.Ku-band antenna array feed distribution network with ferroelectric phase shifters on silicon[J].IEEE Transactions on MTT, 2006,54(3): 1131-1138.

[14] Mancuso Y, Gremillet P,Lacomme P,et al.T/R-modules technological and technical trends for phased array antennas[C]//Proceedings of European Microwave Conference.[S.l.]:IEEE,2005:817-820.

[15] Comeau J P, Morton M A,Kuo W-M L,et al.A silicon-germanium ceceiver for X-Band transmit/receive radar modules[J].IEEE Journal of Solid-State Circuits, 2008,43(9):1889-1896.

[16] Corey L, Jaska E, Guerci J.Phased-array development at DARPA[C]//Proceedings of IEEE Symposium on Phased Array Systems and Technology. [S.l.]:IEEE,2003:9-16.

[17] deA Boer, Mouthaan K.GaAs mixed signal multi-function X-band MMIC with 7 bit phase and amplitude control and integrated serial to parallel converter[C]//Proceedings of 30th European Microwave Conference.Paris,France:IEEE,2000:1-4.

[18] vanF E Vliet,de A Boer.Fully-integrated core chip for X-band phased array T/R modules[C]//Proceedings of IEEE MTT-S International.[S.l.]:IEEE,2004:1753-1756.

[19] Wehling J H.Multifunction millimeter-wave systems for armored vehicle application[J].IEEE Transactions on MTT, 2005,53(5):1021-1025.

[20] Yang J M, Lai R,Chung Y H,et al.Compact ka-band bi-directional amplifier for low-cost electronic scanning array antenna[J].IEEE Journal of Solid-State Circuits, 2004,39(10):1716-1719.

[21] Mark A Mitchell.An X-Band SiGe single-MMIC transmit/receive module for radar applications[C]//Proceedings of IEEE Radar Conference. Boston,MA:IEEE,2007:664-669.

[22] Byung-Wook Min,Rebeiz G M.A Ka-band BiCMOS T/R module for phased array applications[C]//Proceedings of IEEE CSICS. Monterey, CA:IEEE,2008:1-4.

[23] Eli Brookner.Phased arrays for the new millennium[C]//Proceedings of IEEE International Conference on Phased Array Systems and Technology. Dana Point, CA:IEEE,2000:3-19.

[24] Caekenberghe K V, et al.Ka-band MEMS TTD passive electronically scanned array (ESA) [C]//Proceedings of IEEE Symposium on Antenna and Propagation. Albuquerque, NM:IEEE,2006: 513-516.

[25] Hajimiri A, Hashemi H,Natarajan A,et al.Integrated phased array systems in silicon[J].Proceedings of the IEEE, 2005,93(9): 1637-1655.

[26] Kwang-Jin Koh,Rebeiz G M.An X- and Ku-band 8-element linear phased array receiver[C]//Proceedings of IEEE Custom Integrated Circuits Conference(CICC). San Jose, CA:IEEE,2007:761-764.

[27] Kwang-Jin Koh, May J W,Rebeiz G M.A Q-band (40~45GHz) 16-element phased-array transmitter in 0.18-μm SiGe BiCMOS technology[C]//Proceedings of IEEE RFICS. Atlanta, GA:IEEE,2008: 225-228.