基于DSP的无线数据传输平台设计与实现

2010-09-26

(成都理工大学 工程技术学院,四川 乐山 614007)

1 引 言

随着现代通信技术的发展以及DSP芯片性价比的提高和广泛的应用,使得用DSP芯片作为无线通信的硬件平台,尽可能多地用软件来实现通信功能,成为现代通信领域发展的一种趋势。频移键控(Frequency Shift Key,FSK)调制是用数字基带信号来控制高频载波频率的变化,调制后的载波信号频率代表了要传送的数字信号。它具有实现起来较容易、抗噪声与抗衰减的性能较好等优点,在无线数据传输中得到了广泛的应用。

本文介绍了一种基于DSP和2FSK全数字调制解调方法的无线传输平台。系统设计的目标是以通用的DSP TMS320VC5416为核心,结合简单的硬件结构,实现低成本的数据和音频传输系统,能够通过本系统实现传输速率为16 kbit/s数字音频信号的传输和可靠的数据传输。

2 系统整体结构

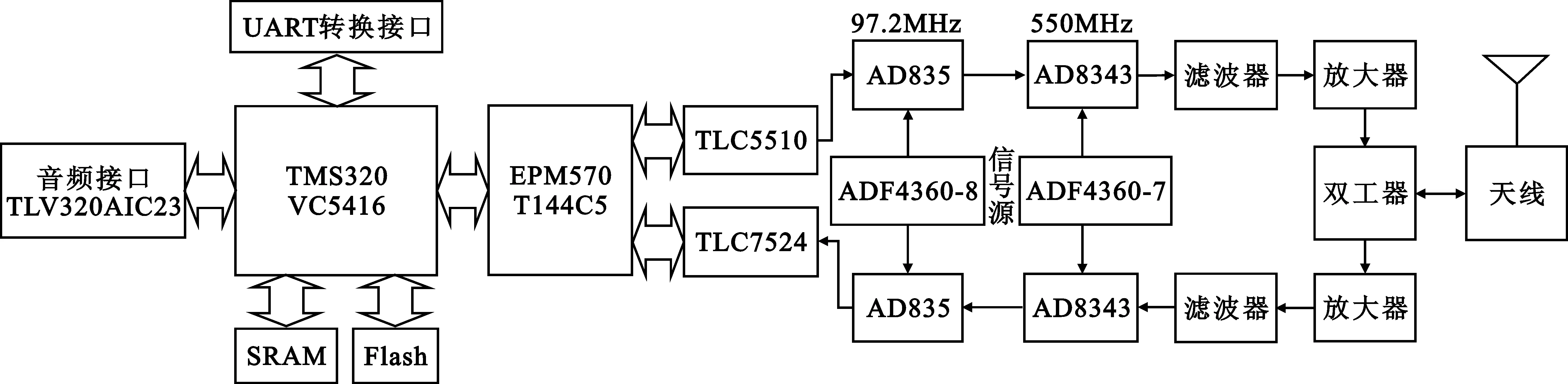

系统以DSP TMS320VC5416和CPLD EPM570T144C5为控制核心,可以实现数据的调制解调、数模转换、模数转换、信号变频以及信号的收发。系统结构框图如图1所示。

图1 系统结构框图Fig.1 System structure diagram

系统中DSP主要完成信号的2FSK调制和解调,并在CPLD的配合下完成对系统中其它模块的控制。TLV320AIC23实现语音信号的转换,工作在DSP模式,以8 kHz的速率通过McBSP0、McBSP1实现与DSP之间的数据交换,而UART串行口实现数字信号在PC机与DSP之间的通信。

DSP的2FSK载波中心频率设置在24 kHz,使用低价位的8位模数转换器TLC5510和8位数模转换器TLC7524以192 kHz的频率对系统输入输出信号进行转换,并经过混频器AD835和AD8343的两次变频实现频率变换。AD835以本振97.2 MHz的频率实现一次变频,AD8343以本振452.8 MHz的频率实现二次变频,进而实现调制载波信号与550 MHz UHF信号之间的变换。

系统所用97.2 MHz和452.8 MHz的本振,由PLL-VCO ADF4360-8和ADF4360-7实现[1],它们在DSP的控制下可以方便地更改输出本振频率。ADF4360共有C寄存器、R寄存器和N寄存器配置寄存器,每个寄存器24位。配置的顺序是上电→R寄存器→C寄存器→N寄存器,前后顺序不能颠倒,否则ADF4360不能锁定。ADF4360通过SPI接口完成数据传输,这可以通过DSP的McBSP2实现。在不改变鉴相频率、控制方式的情况下,只需改变N寄存器内相应数据即可改变输出频率。

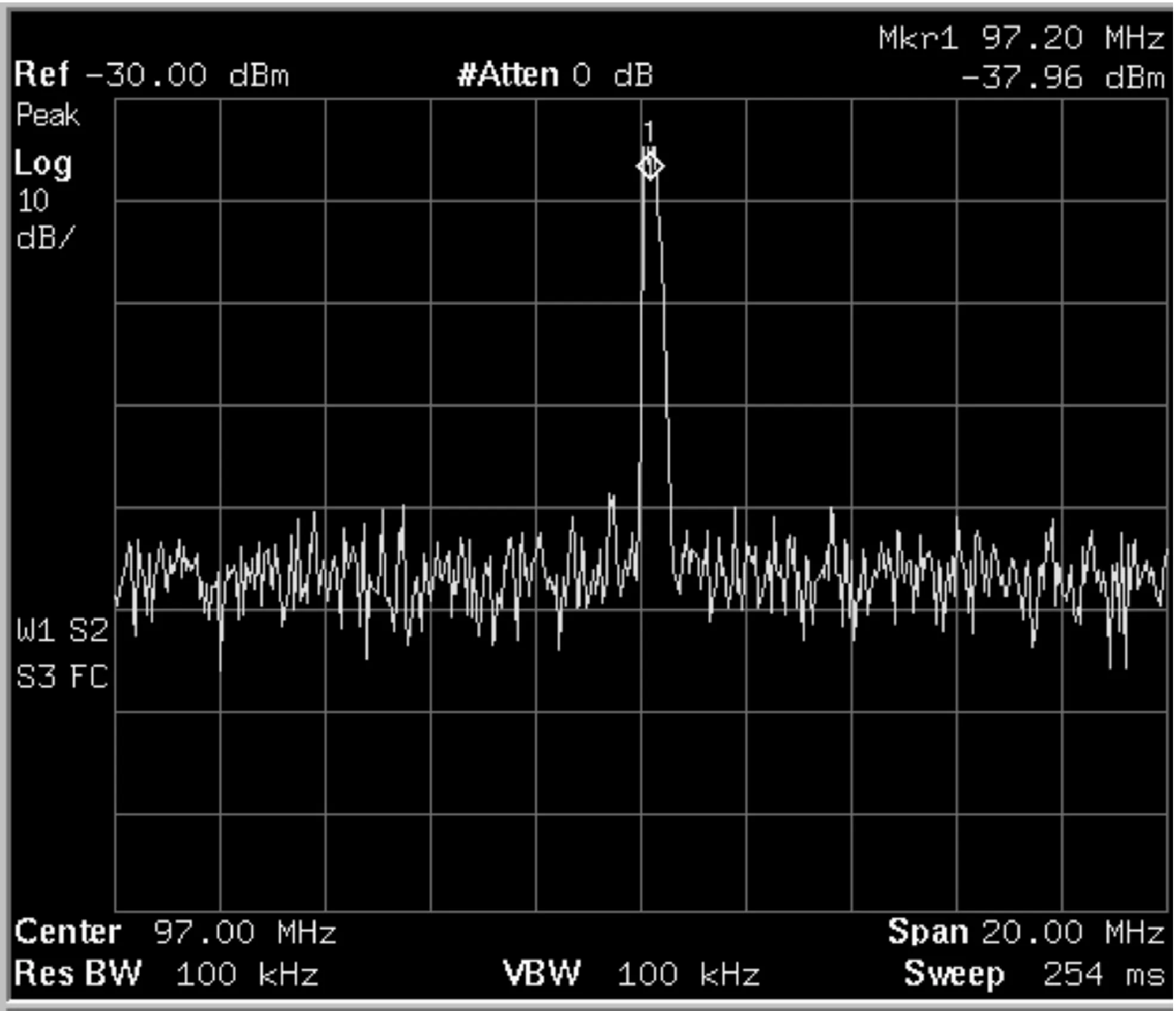

以发射通道作为测试对象,使用频谱仪测试AD835输出的一次上变频信号以及测试AD8343输出的二次上变频信号所得频谱如图2和图3所示。

图2 一次上变频后信号频谱Fig.2 The signal spectrum after once up-conversion

图3 二次上变频后信号频谱Fig.3 The signal spectrum after secondary up-conversion

3 系统软件实现

为了使DSP能够工作在全速状态,DSP系统程序的启动设计为8位并行自举加载的方式,系统所有程序固化在Flash SST39VF040中。在自举加载后,所有程序都被读取到DSP的DARAM中执行,可以使DSP在全速160 MHz的主频下可靠地运行,增加系统处理能力的实时性。系统的2FSK数据调制解调速率设计为16 kbit/s,在此使用中心载波频率Fc=24 kHz,载波F0=16 kHz表示“0”,载波F1=32 kHz表示“1”[2]。系统的AD采样频率Fs设置为192 kHz,每个码元包含12个采样点。

3.1 CPLD控制接口的定义

由于DSP的控制端口较少,因此使用CPLD作为系统中的“胶合”,实现DSP对系统中其它外围设备的控制。外围设备的地址都被分配在DSP的I/O空间,相应的设备端口控制分配如表1所示。

表1 DSP外设的CPLD映射地址Table 1 The CPLD mapping address of DSP peripherals

系统中的两个PLL-VCO器件共用一个地址,在DSP需要对PLL-VCO进行设置的时候,通过不同的子地址实现区分。DSP先将数据以PLL-VCO子地址→ R寄存器→C寄存器→N寄存器的数据写入CPLD进行缓存,然后再由CPLD以SPI的方式将缓存数据写入到PLL-VCO中。以ADF4360-7输出452.8 MHz本振的控制为例,R、C、N寄存器配置字分别是0x300191、0x0FF92C、0xE23602,相关DSP程序如下:

ST #0x0000,*AR7

PORTW*AR7,0x0003;端口写ADF4360-7子地址

ST #0x3001,*AR7;

PORTW *AR7,0x0003; 端口写ADF4360-7 R寄存器高16位

ST #0x910F,*AR7

PORTW *AR7,0x0003;端口写ADF4360-7 R寄存器低8位和C寄存器高8位

ST #0xF92C,*AR7

PORTW *AR7,0x0003;端口写ADF4360-7 C寄存器低16位

ST #0xE236,*AR7

PORTW *AR7,0x0003; 端口写ADF4360-7 N寄存器高16位

ST #0x0200,*AR7

PORTW *AR7,0x0003; 端口写ADF4360-7 N寄存器低8位

3.2 2FSK调制算法

2FSK调制采用查表法,可以实现较好的实时性,特别适用于通信载波的生成。在DSP的程序存储空间,使用Q15定点数格式在[0,2π]上以2π/N的相位间隔固化N点正弦值,以供查表,在此取N=12。这样,对于F0和F1的取样间隔分别为

(1)

使用DSP定时器T0,用来实现对数据解调DAC输出速率的控制。这样,如要实现12 kbit/s的数据传输速率,需要将DSP定时器T0的溢出率设置为192 kHz。

3.3 2FSK解调算法

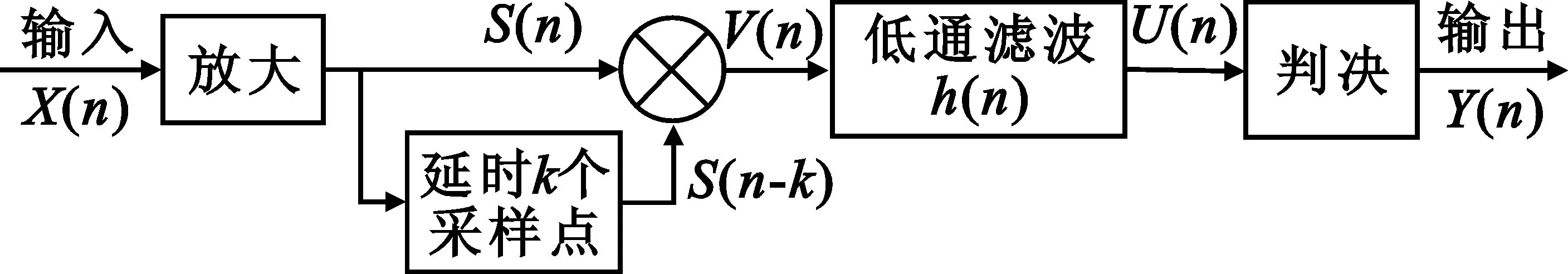

FSK解调有相干解调和非相干解调[3-4],相干解调对通信设备要求较高,一般数字调频系统都采用非相干解调[5]。在此,采用实时性较高的2FSK信号差分检波解调算法[6]。算法的基本思想是已调信号和它的π/2的延时信号相乘,然后经过低通滤波,根据滤波结果的符号判断发送信号的值,从而实现信号的解调。算法原理如图4所示。

图4 2FSK解调算法原理图Fig.4 Schematic diagram of 2FSK demodulation

信号采样值S(n)经延时器延迟k个采样点得到S(n-k)。k要小于每个二进制码元周期内的采样点数,使得S(n)和S(n-k)是属于同一个二进制码元的采样值。S(n)和S(n-k)相乘后的输出样值为

V(n)=S(n)S(n-k)=

A2sin(2πFnTs)sin[2πF(n-k)Ts]=

(2)

前面一部分是仅与k有关的常数,后面一部分是与n有关的高频分量,可通过对称系数低通滤波器h(n)来滤除。低通滤波器h(n)的截止频率设为12 kHz,对称系数经Matlab计算求得:h0=0.000 184 97,h1=0.263 16,h2=0.192 72,h3=0.220 79。通过该低通滤波器后得到:

(3)

k的选择是设计解调器的关键,应使差值:

d(k)=cos(2πF0kTs)-cos(2πF1kTs)

(4)

最大,以利于正确区分两种频率,降低判决的误码率。根据实际的测试得到,当k=2时,可以得到较好的区分度。经过低通滤波后的数据U(n)经过判决算法后,可以得到最终所要的解调数据Y(n)。

系统12个采样数据表示一个码元,当判决算法连续判决12个采样数据(一个码元包含的采样点)满足预设阈值之后,确定一个码元的状态。假设如下判决算法中用到的变量:LPFOUT→滤波器输出,DATA-THD→幅度判决的阈值,DEC-DATA-CURR→当前采样点判决值,DEC-DATA-BE→前一次采样点判决值,DEC-NUM→判决用计数器,DEC-NUM-X→周期计数器。判决算法流程图如图5所示。

4 实验测试结果

发射端以F0=16 kHz与F1=32 kHz调制二进制数据“10001011011”,并经过DAC及两次上变频发射出去。接收端将接收到的信号两次下变频及模数转换后,DSP将采集数据读进来进行解调。为了便于分析,将数据预先存储起来,使用2FSK解调算法,对采集数据进行解调。2FSK解调过程中,关键步骤处理的结果在CCS 2.2下的分析如图6所示。

图5 2FSK解调算法程序流程图Fig.5 2FSK demodulation flow chart

图6 2FSK解调算法实验结果Fig.6 The experimental results of 2FSK demodulation

图6包含了采集的调制原始数据S(n)、延时相乘后的数据S(n-k)、经过低通滤波后的数据U(n)和解调之后的数据Y(n)。由图6可以看到,原始的调制数据“10001011011”经过解调程序后,可以准确地将原来的数据解调出来。2FSK的解调算法使用汇编语言编写,基本做到了程序设计的最优化。经实际测算,解调程序每个码元的解调时间为481个CPU时钟周期。当DSP工作在全速160 MHz的CPU时钟频率下时,解调一个二进制码元的时间为3 μs,完全可以满足系统16 kbit/s的数据传输速率,系统具有较高的实时性。

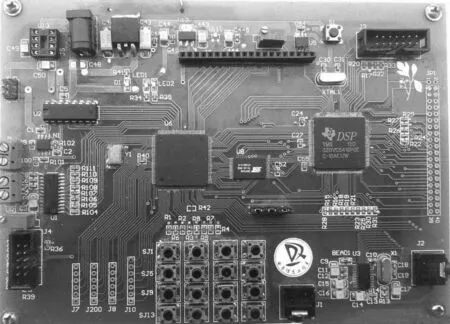

5 系统主控电路板设计注意事项

主控板主要包括DSP、CPLD、音频编解码电路、ADC电路、DAC电路以及与外部连接的接口。主控板使用两层板设计,进一步降低系统的整体成本。在电路板设计调试过程中需要注意以下几点:

(1)以网状线路对电路板不同部分供电。并确认DSP核心供电电压为1.6 V,否则,DSP将不能工作在160 MHz全速状态;

(2)以减小信号回路面积为原则,模拟部分的电路中的电源线、地线以及模拟信号线,与数字部分线路不发生交叉,最好能够将各模拟部分的线路以各自线路独立布线,特别是ADC与DAC的电路;

(3)在焊接调试的时候,一定要步步为营,焊接并调试好一部分后,再进行下一步;

(4)焊接调试步骤:电源电路→DSP电路→CPLD电路→ADC电路→DAC电路→其它电路。系统主控电路板如图7所示。

图7 系统主控电路板Fig.7 System main control circuit board

6 结束语

经过实际测试,系统工作稳定,数据传输及语音传输实现了预期目标。系统的硬件电路设计简洁,可靠性和灵活性高。对所选DSP来讲,系统中所用到的FSK调制解调算法,运算量不大,实现了实时的数据传输。

系统实现的2FSK的调制解调算法,可以应用在电力载波通信以及铁路信号检测等领域。以此平台为基础,经过改进、程序移植可以应用在单兵无线通信、卫星通信等领域,具有较高的实践应用意义。

参考文献:

[1] 沈伟.基于ADF4360-7的宽带雷达信号源设计[J].现代雷达,2006,28(8):39-42.

SHEN Wei. Design of Local Oscillator for Wideband Radar with Chip ADF4360-7[J]. Modern Radar, 2006,28(8):39-42.(in Chinese)

[2] 王伦文, 钟子发.2FSK信号“指纹”特征的研究[J].电讯技术,2003,43(3):45-48.

WANG Lun-wen, ZHONG Zi-fa. Study on Fingerprint Characters of 2FSK Signal[J]. Telecommunication Engineering, 2003, 43(3): 45-48. (in Chinese)

[3] 龙胜春.2FSK信号的相关解码算法[J].通信学报,2003,24(11):172-176.

LONG Sheng-chun. A Correlation Demodulation Algorithm of 2FSK Signal[J]. Journal of China Institute of Communications, 2003, 24(11): 172-176. (in Chinese)

[4] 黄翔东,何宇清,李长滨.一种检测铁路2FSK信号频率的新方法[J].天津大学学报,2007,40(9):1115-1119.

HUANG Xiang-dong, HE Yu-qing, LI Chang-bin. Method for Detection of the Frequencies of Railway 2FSK Signal[J]. Journal of Tianjin University, 2007, 40(9): 1115-1119. (in Chinese)

[5] 赵顺珍.基于DSP的二进制频移键控的实现方法[J].微计算机信息,2008,24(2):183-184.

ZHAO Shun-zhen. Implementation of 2FSK Based on Digital Signal Processing[J]. Microcomputer Information,2008,24(2):183-184.(in Chinese)

[6] TI Inc.Implementation of an FSK Modem Using the TMS320C17[Z].Texas,USA:Texas Instruments Inc,1998.