数字通信系统相位均衡滤波器的 FPGA实现

2010-09-23李海军邳志刚

李海军, 邳志刚, 边 莉

(黑龙江科技学院 电气与信息工程学院,哈尔滨 150027)

数字通信系统相位均衡滤波器的 FPGA实现

李海军, 邳志刚, 边 莉

(黑龙江科技学院 电气与信息工程学院,哈尔滨 150027)

为校正数字信号传输中的相移畸变,针对 CDMA通信系统基带到射频输出部分,设计一种基于 FPGA实现的相位均衡滤波器。该滤波器由反馈延迟、查找表、加法器和解复用输出模块组成。仿真结果表明,该滤波器符合全通均衡滤波器的特性,可较好地修正相移畸变,节省 FPGA资源。该相位均衡滤波器实现方法可应用于数字通信系统。

滤波器;FPGA;相移畸变;仿真

Abstract:This paper proposes a FPGA-based phase equilibrium filter designed to correct phase distortion in the digital signal tran smission occurring between baseband and radiofrequency output in CDMA communication system.The filter is composed of feedback delay,lookup tables,adder and demultiplexer outputmodule.The simulation shows that this filter,consistent with characteristics of all-pass equalization filter,enables a better rectification of the distortion on phase-shift and economy in the FPGA resources.The filter can find application in the digital communication system.

Key words:filter;FPGA;phase distortion;simulation

0 引 言

信号在传输中会产生幅度畸变、相移畸变。对于模拟信号,由于人耳对相移变化的感觉不灵敏,一般可不考虑相移畸变问题[1]。但在数字信号传输中,相移畸变的影响比幅度畸变大,所以,除了校正幅度畸变外,还需校正相移畸变。基于此,笔者针对CDMA基站设计一种基于现场可编程门阵列 (FPGA)实现的相位平衡滤波器,以期较好的校正相移

畸变,尽量减少 FPGA内部资源的占用。

1 相位均衡滤波器的 FPGA实现

1.1 原理

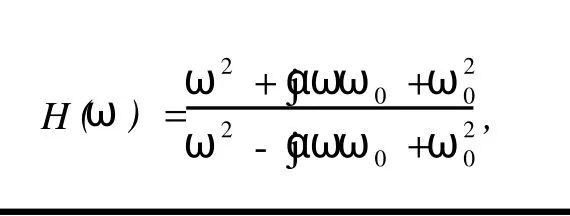

为了对信号进行预畸变,在 CDMA基站系统的基带到射频输出部分加入相位均衡滤波器[2],其传输函数

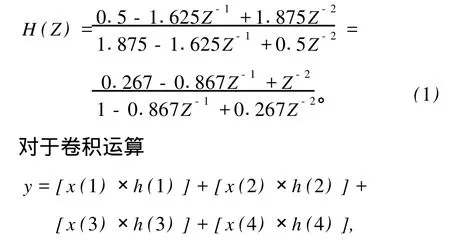

其中,α =3.16,ω0=2π ×3.15 ×105。经转换,得H(Z)表达式

较简单的实现方法是每一位 x(n)利用一个乘法器,但这样将过多地占用 FPGA的内部资源。为此,笔者采用查找表 (LUT)结构,将卷积运算转化为查找表,再用移位求和的方法实现[3-4]。

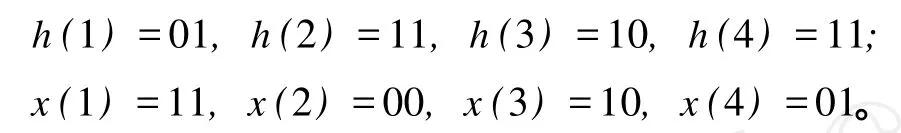

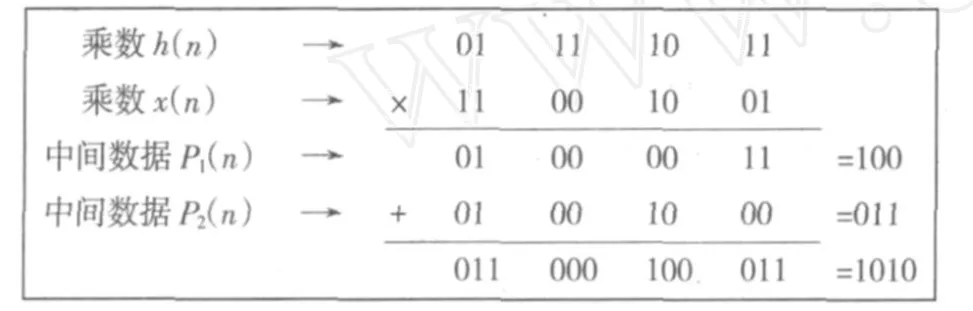

假设 x(n)和 h(n)均是无符号整型二进制数,位宽为 2 bit,取值如下:

其卷积运算过程如图 1所示。

图 1 卷积运算过程Fig.1 Convolution computation process

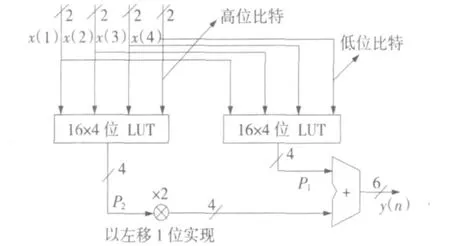

由图 1可见,卷积运算可以纵向、横向分别实现。中间数据 P1(n)是乘数 x(n)的最低位比特与h(n)相乘的结果,其值只可能是 0或 h(n),这是因为二进制的取值只有 0和 1。进一步考虑,中间数据 P1(n)和 P2(n)的值 100和 011是由不同的h(n)之和构成,如何选择 h(n)是由乘数 x(n)的相同位的比特决定的。如图 1中 x(n)的最低位为 1001,则P1(n)的值为 h(1)+h(4);其高位为 1010,则P1(n)的值为 h(1)+h(3)。利用查找表结构[5],预先将 h(n)的各种组合 (在本例中从 0000到 1111共16种)存入查找表,可将原需四次乘法和三次加法的卷积运算转化为一次加法运算。图 2给出了查找表实现结构。

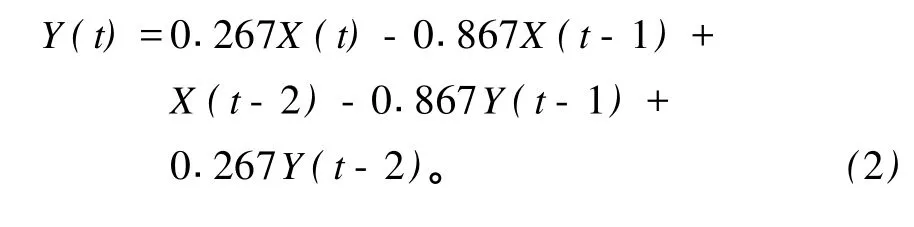

对式 (1)进行逆 Z变换,可以得到滤波器公式

图 2 查找表实现结构Fig.2 I mplementation structure on look-up-table

1.2 复用实现

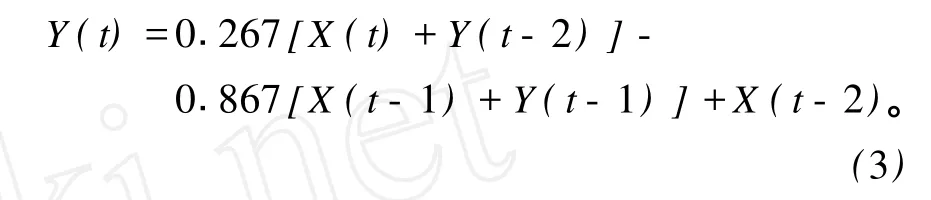

滤波器的前馈和反馈单元系数存在对称关系,故可将式(2)进一步简化为

根据式(3),在卷积运算之前将对应的前反馈信号合并,可以节省 50%以上的资源[6]。

该滤波器采用流水线处理结构,输入信号共分六组,每组信号的速率为 chip2,可以应用复用技术进一步减少 FPGA资源的占用。

由于 FPGA主频采用 chip16(chip2的 8倍),在其时钟周期内,可以复用八路信号,现在只有六组信号,故需在一个 chip2时钟周期内填充两个无用数据,使得数字合并部分的延迟与信道板数目、信号复用的形式与所采用的同步信号相关,以便在解复用时在对应管脚输出正确数据。

2 模块设计

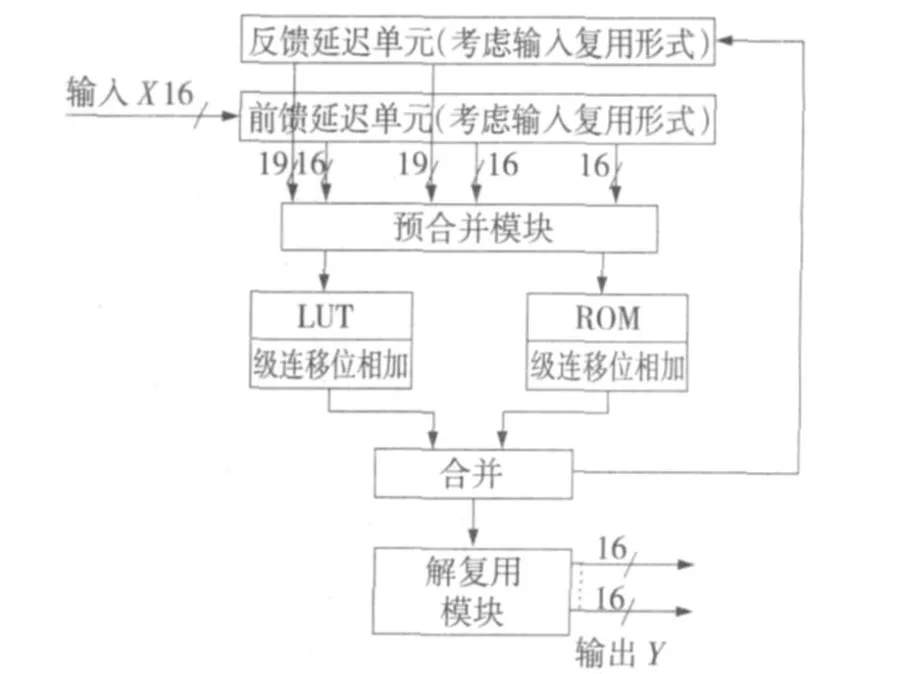

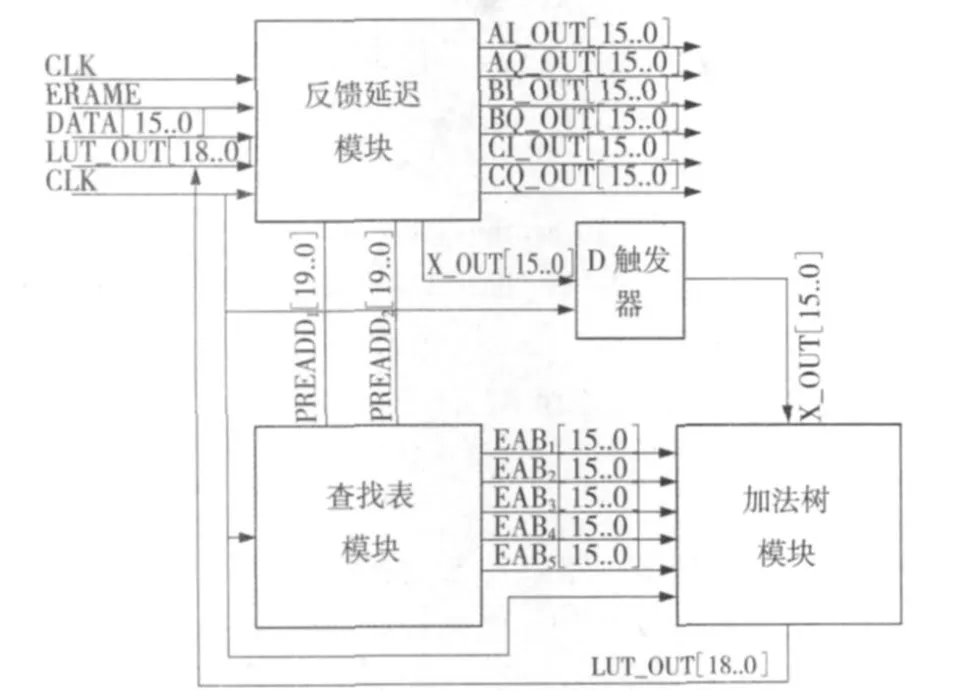

采用模块化思想设计该相位均衡滤波器,模块划分如图 3所示。

图 3 相位均衡滤波器模块划分Fig.3 M odule division of phase equalizer

相位均衡滤波器主要包括前馈、反馈延迟单元,LUT、ROM,级连求和三大模块。

(1)前馈和反馈延迟单元。该模块可用移位寄存器实现。正常前反馈单元仅需两组移存器,该滤波器的信号输入是复用形式,即 A I1-AQ1-B I1-BQ1-CI1-CQ1-X-X-A I2-AQ2-B I2-BQ2-CI2-CQ2-X-X(ABC代表α、β、γ扇区,X代表无用数据),其前反馈单元需用 32组移存器。输入数据宽度为 16位,速率 chip16。

(2)LUT和 ROM。查找表结构既可以用 PLD中的 Lcell实现,也可以用 EAB(内嵌 ROM阵列块)实现。为使 EAB和片内资源的利用率达到最大,采用一部分用 EAB、另一部分用 LUT实现的方案。

(3)级连求和。求和部分为一加法树,对应xin高位比特查找表的输出要乘以相应的权值 (对二进制数左移)后再相加。模块输出 16 bit的滤波信号后,相对于输入具有一个 chip2时钟周期的延迟。

3 模块实现

该滤波器主要由反馈延迟模块、查找表模块和加法器模块等组成,其结构如图 4所示。

图 4 相位均衡滤波器 FPGA实现结构Fig.4 I mplementation structure of phase equilibrium based on FPGA

3.1 反馈延迟模块

反馈延迟模块根据式 (3)将输入的前向数据(A I、AQ、B I、BQ、CI、CQ)和输出的滤波数据做相应的延迟 (注意每一帧数据是由八个 16 bits数据复用组成的,如果按式 (3)延迟两拍需要 16个级连的 D触发器组),并在帧头信号 FRAME指示下将滤波数据并行输出到解复用模块。再将延迟后的数据相减,即可得到两个查找表的输入地址。滤波器的输出数据是八个数据复用,有一拍和两拍的延迟,实现上采用 D触发器组延迟的方式。当复用数据的帧头信号到来时,根据不同的延迟次序将数据解复用后输出。输出滤波后数据时,需根据数据的符号位采取防错措施。这是因为数据是按二进制补码方式表示的,其最高位是符号位的扩展位,也就是说只有正 00和负 11两种情况,如果数据发生溢出,其最高位可能变为 10或者 01的错误状态。

3.2 查找表模块

查找表模块由五个 MAXPLUS内部产生的LPM-ROM组成,ROM的容量为 256*16。查找表的输入是反馈延迟模块的输出。根据输入的地址将数据送出,完成部分乘法器的功能。查找表的地址按以下的方式组成:PREADD1[19..0]的低四位、PREADD2[19..0]的低四位组成第一个查找表的输入地址,对应的 ROM中的内容是 PREADD1四位、PREADD2四位与相应的两个系数的乘积之和。低16位的 ROM的内容相同,高四位由于涉及到符号位,故需做不同的处理。

3.3 加法树模块

加法器模块是一个加法树,将查找表输出的数据加上不同的权值,按照一定的次序相加,得到滤波器的输出数据。EAB1[15..0]、EAB2[15..0]、EAB3[15..0]、EAB4[15..0]、EAB5[15..0]分别对应 PREADD1和 PREADD2的四位地址,在对滤波器卷积结果求和时,EAB1~EAB5应该乘以或者除以不同的权值,即左右移位,再进行加法运算,从而得到正确的结果。

3.4 解复用输出模块

解复用输出模块由三个相同的解复用模块组成,每一个模块对应一个扇区的两路信号。每个解复用模块利用一个三位的计数器,将并行的 16 bit数据转化为串行的 2 bit数据。送出的是 2 bit数据流。在数据流传输过程中加入同步信号,以表示一个数据的开始,同时,对输出的 I、Q两路共 4 bit的数据流进行奇偶校验。

4 仿 真

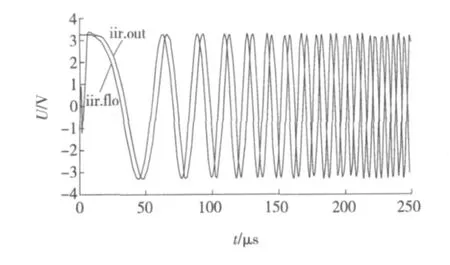

图 5为该滤波器仿真结果,其中滤波器输入数据包含各种频率分量的数据流。

从图 5可以看出,该滤波器符合全通均衡滤波器的特性,可较好的校正相移畸变。

图 5 滤波器仿真结果Fig.5 Filter s imulation result

5 结束语

数字信号在传输中的相移畸变较幅度畸变影响大。为此,笔者针对 CDMA通信系统基带到射频输出部分,设计一种基于 FPGA实现的相位均衡滤波器。通过简化滤波器公式,运用复用技术,减少了FPGA资源的占用。仿真验证该滤波器符合全通均衡滤波器的特性,可较好地校正相移畸变,具有推广应用价值。

[1] 尼俊红,刘泽民.基于 FIR多率滤波器组的盲信道估计方法的改进[J].信息与电子工程,2007(3):161-164.

[2] 王 静,鱼云岐.基于 FPGA的 FIR数字滤波器设计与仿真[J].国外电子元器件,2008(11):90-92.

[3] 张光法.基于 FPGA和Matlab的均衡滤波器设计与实现[J].舰船电子工程,2009(7):204-207.

[4] 仰继连,曾以成,徐茂林.设计有限字长 FIR数字滤波器的蚂蚁算法[J].数据采集与处理,2009(3):375-379.

[5] 朱 武,张佳民,张智明.基于并行结构分布式算法的 FIR滤波器设计[J].电子测量与仪器学报,2007(4):87-92.

[6] 张松华,陆秀令.IIR数字滤波器的粒子群优化设计方法[J].信息与电子工程,2007(4):271-274.

(编辑 荀海鑫)

FPGA implementation of filter with phase equalizer in digital communication system

L I Haijun, PI Zhigang, B IAN L i

(College of Electric&Infor mation Engineering,Heilongjiang Institute of Science&Technology,Harbin 150027,China)

TN919.64

A

1671-0118(2010)05-0383-04

2010-09-06

黑龙江省教育厅科学技术研究项目(11541314)

李海军 (1971-),男,吉林省扶余人,副教授,硕士,研究方向:电子信息工程,E-mail:lhjlhj4@yahoo.com.cn。