视频传输不等差错保护方案设计*

2010-08-10陈孙阳陈颖琪

陈孙阳 ,陈颖琪 ,王 慈

(1.上海交通大学 电子工程系 图像通信与信息处理研究所,上海 200240;2.上海市数字媒体处理与传输重点实验室,上海 200240)

1 概述

视频监控系统在工业控制、保密通信、公共安全、道路交通等领域得到越来越广泛的应用。监控视频的传输主要有两种方式:有线传输和无线传输。无线信道固有的随机性以及宇宙射线、工业火花、雷电等对无线信道的干扰,无线信道中同时存在随机错误与突发错误。不等差错保护机制根据视频流分层的重要性以及信道状况,对不同的数据提供不同的保护级别,提高纠错性能的同时更为有效地利用了信道带宽。

文献[1]提出了基于分层编码和OFDM的不等差错保护方案,文献[2]提出了基于Reed-Solomon编码的不等差错保护方案。然而,前者仅仅考虑了视频流不同分层的权重因子而未考虑实际信道状况,因此不能用于要求自适应能力的信道编码;后者能够纠正大部分的随机错误和一定程度的突发错误,但是当信道连续恶化造成大面积的突发错误时,该方案的纠错容限就无能为力了。为了同时纠正信道中的随机错误和突发错误,笔者提出了多级RS编码器(Multi-level RS Encoder)与信道交织器级联的方案。为了有效地利用信道带宽传输码流数据或者实现双方的保密通信,本系统能在MCU的控制下实时地改变信道纠错编码保护级别和传输码率。

2 多级RS编码与交织器级联方案

2.1 多级Reed-Solomon编码器

现有的差错控制编码分为两大类:分组编码和卷积编码。Reed-Solomon编码是一种分组码、系统码和线性、循环码,能够高效地纠正信道中出现的突发错误。RS码凭借其优异的性能和折中的实现复杂度,在电视广播中得到了广泛应用,如 DVB-T 中的 RS(204,188)。

为了实现不等差错保护机制,设计了4个纠错级别的 RS 码,分别是 RS(255,239),RS(255,223),RS(255,191)和RS(255,255)。系统控制端根据信道状况指定每一个数据包的编码保护级别[4],在信道情况较好时选择RS(255,239)或 RS(255,255),在信道情况较差时选择最高编码保护级别的RS(255,191)。为了通信双方的保密性,控制器可以随机选择编码保护级别,这种随机选择算法大大增加了潜在窃听者识别信息包的难度,即使截获了某个信息包,在不知道包头信息含义的情况下也毫无意义。

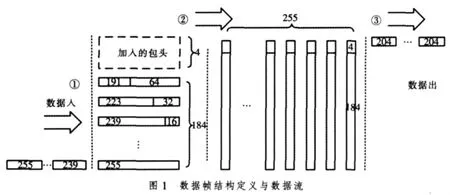

根据重要性、信道状况或者是保密通信的需要,将原始码流分割为191,223,239和255这4种不同长度的数据包,如图1中标号①所示。每个数据包的包头指示当前数据包的编码保护级别,MRSE模块根据该信息确定当前包采用何种级别的RS编码。

2.2 数据交织

各个RS编码器的输出端都是255 byte的数据包。当采用RS(255,191)时,在一个数据包里最多允许有64个错误符号。当错误超过64个符号时,整个信息包无效。无线信道里因为存在雷电、工业火花等干扰而引起的突发错误,很有可能使得差错符号超出上述基于RS编码的UEP系统的纠错容限。为了进一步提高系统的整体容错性能,增加了一级数据交织模块,将突发错误离散化。

数据交织时,将184个255 byte的数据包组成一个内部数据帧(frame)。交织器按照行的顺序将RS数据包写入内部Buffer,当Buffer中填满一帧的数据后,控制逻辑按照列的顺序读出Buffer中数据,并在每列数据的前面加入包头信息。数据帧定义和数据交织过程如图1中标号②所示。

2.3 包头信息位保护

上述的数据交织模块根据交织算法的要求,输入端的数据包按照行的顺序写入帧缓存,输出端按照列的顺序输出数据包,并加入包头信息,形成长度为188 byte的新数据包。因为第一级数据包(255 byte)的前4个字节为包头信息,因此,在按照列的顺序输出数据时,前4列的数据对应于交织器Buffer中数据的所有包头信息。如果这4个包发生错误的话,帧缓存中的信息包就不能正确地得到译码。为了进一步保护这些包头信息,再级联一个 RS(204,188)编码器,将交织后的 188 byte的数据包编码为204 byte的数据包。本级RS编码后的码流如图1中标号③所示。实际上,RS(204,188)编码器的实现和RS(255,239)完全一样,并没有增加系统的设计复杂度。

3 实现架构设计

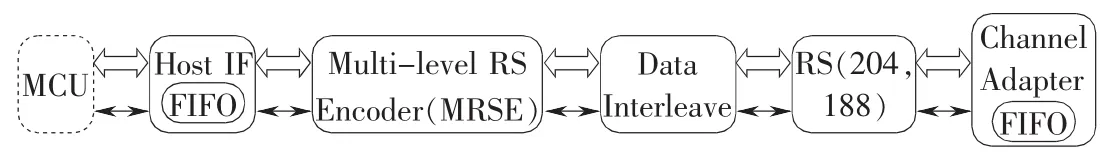

MCU对Host IF模块中的寄存器进行配置,并将编码后的视频流分成含分割指示信息的原始数据包,原始数据包的长度可以为 4 种模式 191,223,239,255,MCU可以根据当前的信道情况或者保密通信的要求将视频流分割成上述的长度后发送到Host IF模块。

Host IF模块作为FPGA端接口模块,缓存来自MCU的32 bit的数据流,提取包头信息,加入负荷符号位后组成待编码信息包发送到MRSE模块进行不同保护级别的RS编码。HOST IF中包括了一个深度为256 byte的异步FIFO用于缓存MCU模块发送的异步数据。

图2 系统整体设计框图

MRSE模块为本系统的核心算法模块,提供4个级别的差错保护编码。其内部包含了4个并行的RS编码器,同时给上一级模块提供了选通逻辑。

Data Interleave模块对经过不同保护级别RS编码后的数据进行交织处理,将184个长度为255 byte的数据包变换255个长度为188 byte的数据包,其中188 byte的前4 byte为交织器加入的包头信息。

RS(204,188)模块对交织后的 188 byte的数据包进行第2级的RS编码,进一步保护了原始数据包的包头信息和信息符号位。

Channel Adapter模块缓存来自前端的数据包,在信道工作时钟下发送数据包(204 byte)给调制模块,同时将当前的信道情况反馈给数据交织模块。

4 子模块设计

4.1 基于专用乘法器的RS编码器

RS编码器实现的关键在于乘法器的实现方式,RS编码器的数学运算基于Galois域,传统的Galois全乘器有着实现方式过于复杂、面积占用多等缺点,因此有必要设计高效的Galois乘法器。

当本原多项式确定了之后,生成多项式的系数就确定了,亦即编码过程中用到的乘法系数就固定了。根据Galois域上运算的定义,Galois域上的乘运算可以转化为位异或运算[3],这个转换过程可以通过高级编程语言将乘系数所对应的参与位异或运算的位找出来。

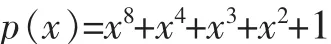

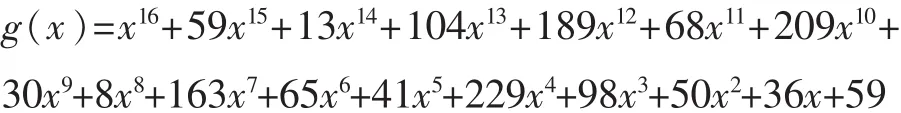

本系统采用GF(28)上的RS编码器,它的本原特征多项式为

生成多项式为

4.2 多级RS编码器

由于RS编码器采用了专用乘法器实现,单个RS编码器的资源占用已经大为降低,本方案采用了3个并行的RS编码器和一个直通通路构成的RS(255,255)编码器,实现4个不同等级的差错保护。采用3个并行RS编码器构建多级RS编码器的优点是前面模块能够快速选通相应级别的编码器,而不需要等待很多时钟周期的配置时间。

4.3 数据交织器

为了处理连续的数据流,交织器模块包含了2块RAM,实现数据流的乒乓操作。当第一块RAM填满数据后,交织器的输入端将新进的数据包填入第二块RAM,同时交织器中的输出控制模块开始逐列读出第一块RAM中的有效数据,同时加入包头信息后形成188 byte的数据包。当第二块RAM 中填满数据后,新进的数据包又开始填入第一块中,同时,输出控制模块开始逐列读出第二块中的有效数据,加入包头信息形成188 byte的数据包。总之,交织器控制模块按照这种乒乓操作的方式处理进来的每个数据包。

4.4 Host IF接口模块

CPU的数据宽度为32 bit,工作频率为60 MHz;后续基于FPGA实现的编码器、交织器的数据宽度为8 bit,工作频率要求根据不同的应用配置为不同的值。因此需要设计一个接口模块对它们之间的数据流进行变换。Host IF模块中含有若干个寄存器,可以对系统的工作环境进行配置,如对复位寄存器进行一次写操作能实现系统的软复位。接口模块中还包括了一个宽度为32 bit、深度为256 byte的异步FIFO用于缓存数据包。当FIFO达到半满状态时,启动读控制模块,按照输出端时序的要求读出FIFO中的数据,具体是在FPGA主工作时钟下,每4个周期读出FIFO中的一个数据(32 bit),读控制模块将其拆分4个8 bit的数据,然后发送到MRSE模块。

4.5 信道适配模块

信道的工作时钟比系统处理时钟低,为了将处理后的数据包(长度为204 byte)发送给后续的调制模块(图中未画出),采用一块宽度为8 bit、深度为256 byte的FIFO缓存数据[5]。FIFO近空时向前级数据交织模块发送读请求,将新的一个数据包读入本模块FIFO中。信道适配模块的读控制逻辑在信道时钟要求的速率下连续输出最终的数据。

5 硬件实现

整体系统采用Verilog HDL编写RTL代码,通过了功能仿真与时序仿真。整体设计在Xilinx ISE 10.1综合后的频率是158.03 MHz,布局布线后的频率为104.5 MHz,在 Virtex-4 XC4VLX100 里仅占用 1 378 个 Slice,即仅占用2.8%的Slice(1 378/49 152)。在基于Virtex-4 XC4VLX100的FPGA自主开发版上实现了D1规格的视频流的信道编码。

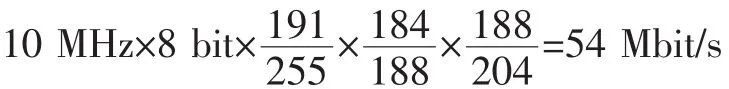

假设FPGA的工作时钟为10 MHz,系统能达到的码率可以这样计算

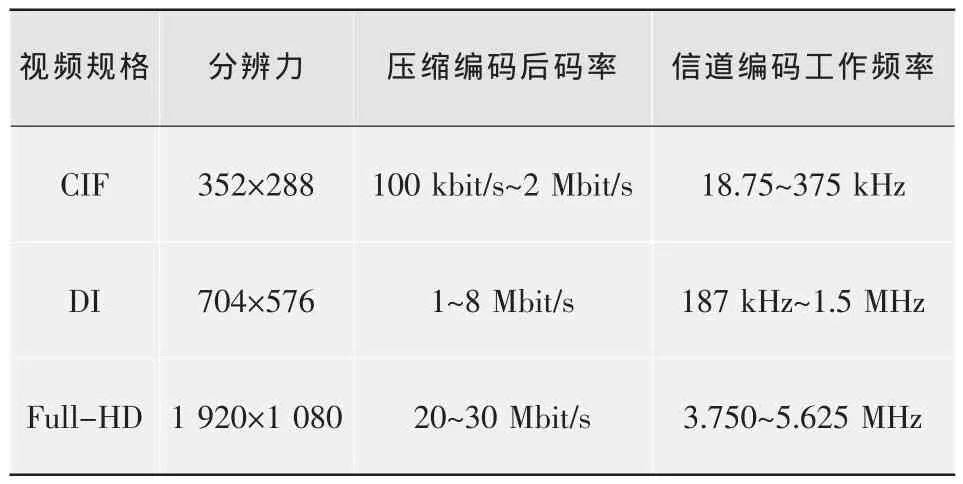

由以上计算可知,当FPGA工作在10 MHz时,本系统提供了54 Mbit/s的码率,能够较好地支持现有的全高清(Full-HD)编码视频流。表1给出了CIF与D1两种视频监控采用的主流规格对应的码率和信道编码工作频率,可与Full-HD进行对比。

表1 视频规格与信道编码工作频率

6 结论

提出了一种将多级RS编码与交织器级联的不等差错保护方案用于传输编码后的视频流。多级RS编码器较好地纠正信道中的随机错误。同时,级联的交织器将信道中的突发错误离散化,进一步提高了该系统的整体纠错能力。理论分析及实验结果表明,本实现方案能够对视频监控的D1码流进行信道编码,同时能够支持Full-HD视频流的信道编码。

[1]郭东亮,吴乐南.基于分层编码和OFDM的不等差错保护[J].电路与系统学报,2003,8(2):18-22.

[2]杨海明,赵明生.多媒体会议中图像通信的不等差错保护技术实现[J].电视技术,2004,28(6):80-82.

[3]SHU L,COSTELLO D J.差错控制编码[M].晏坚,何元智,等译.北京:机械工业出版社,2007.

[4]FANG T,CHAU L P.A novel unequal error protection approach for error resilient video transmission[J].IEEE International Symposium on Circuits and Systems,2005,4:4022-4025.

[5]HUANG C,LIANG S.Unequal error protection for MPEG-2 video transmission over wireless channels[J].IEEE Trans. Signal Processing Image Communication,2004,19:67-69.