基于FPGA的数字图像采集存储系统的设计*

2010-08-10王红亮孟令军

刘 攀,王红亮,孟令军

(中北大学 仪器科学与动态测试教育部重点实验室;电子测试技术国家重点实验室,山西 太原 030051)

1 引言

构建了一种基于FPGA的数字图像采集存储系统,它主要由FPGA、USB单片机、CMOS图像传感器和大容量Flash构成。该系统具有通用性好、成本低等优点。

2 数字图像采集存储系统设计

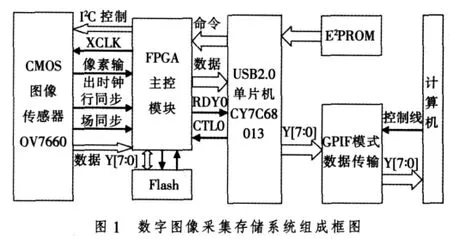

数字图像采集存储系统主要完成数字图像采集存储和实时显示两大功能。系统硬件主要有数字图像采集模块、FPGA逻辑控制模块、Flash存储模块、CY7C68013数据读取实时显示模块(独立)。当系统没有数据读取模块时,可以完成图像的采集存储。当连接数据读取模块时,可以完成Flash存储器内部图像数据的读取以及对CMOS图像传感器实时捕获的图像进行显示存储的功能。数字图像采集存储系统组成框图如图1所示。

3 图像传感器的配置

本系统采用OmniVision公司生产的OV7660数字摄像头模组。OV7660集成了SCCB控制接口用以访问片内寄存器。SCCB接口是OmniVision公司制定的一种用于控制图像传感器的总线 (SIO_C,SIO_D)。SIO_C和SIO_D在功能及使用上与I2C总线兼容。因此,通过FPGA模拟I2C完成对摄像头的配置[1]。

OV7660内部共有165个控制寄存器,可通过配置这些控制寄存器来设定和实现OV7660的各种功能。OV7660写寄存器的设备地址为0x42,读寄存器设备地址为0x43。本设计中OV7660的功能是采集模拟视频信号,并以12 MHz的时钟频率进行A/D转换,输出8 bit宽、格式为YCbCr4∶2∶2的数字信号。在此要求下,只要对OV7660的部分寄存器进行配置即可,其余的寄存器均为系统复位以后的缺省值。关键寄存器配置见表1。

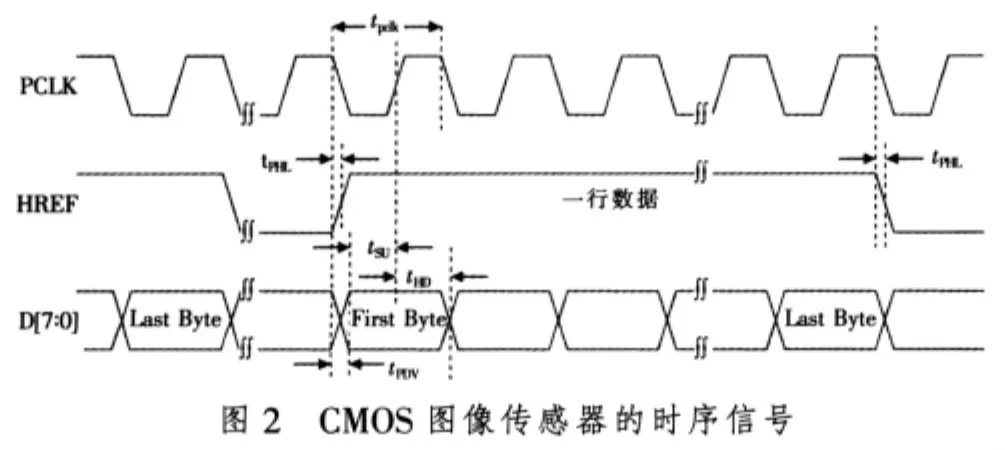

综合考虑采集速率和图像的连贯性,将CMOS图像传感器配置为QVGA工作模式,通过寄存器参数配置,将PCLK配置为 4 MHz。成功配置后产生 VSYNC,HREF,PCLK 3种同步信号,分别为场同步输出信号,行同步输出信号和用来锁存有效数据的时钟,即像素时钟。这3种同步信号作为图像数据获取、传输的状态信号,是整个采集存储系统的重点。

表1 OV7660关键寄存器配置参数

4 图像采集存储模块设计

三星公司生产的K9NBG08U5A具有4 Gbyte容量,相当于 4 片 1 Gbyte 的Flash[2](K9K8G08U0A),因此,在对其读、写、擦除的时候,都要考虑其内部片选切换和对应R/B信号的判断,但是,对每片的基本操作和1 Gbyte的Flash都相同。大容量的Flash保证系统完成长时间的数据采集。

为了保证一帧数据的完整性,系统在收到开始采集命令后在VSYNC场同步的下降沿到来之后才开始采集存储工作。HREF行同步信号为高期间CMOS图像传感器输出的数据才有效,因此,将HREF与PCLK做与处理,再与场同步信号做或处理作为FPGA内部FIFO的写信号。FIFO为FPGA内部扩展,用来作为数据缓冲和时序的匹配,当FIFO半满后就会从中读取数据并写入Flash中。CMOS图像传感器成功配置为QVGA(320×240)模式后输出时序信号如图2所示。

数据输出格式为 QVGA(320×240),每行 320 个像素点,640 byte。图像数据实际输出速率为4 Mbyte/s,即像素时钟 PCLK 为 4 MHz,每帧 QVGA(320×240)图像大小为320×240×2=150 Kbyte。得到的帧率理论值为27.3帧/秒(f/s),保证了视频的连贯性。要求存储器存储速度也要高于4 Mbyte/s才能保证不丢帧。实际应用中经过测试,Flash存储速度完全可以达到4 Mbyte/s,满足系统要求。

5 存储器数据的读取与实时传输显示

系统预留接口电路,可以通过计算机应用软件来控制从CMOS图像传感器获得的图像的实时读取、存储、显示,以及存储器中图像数据的读取及播放。

5.1 存储器数据读取

实际应用中存储器数据读取速度受限于存储器本身和CY7C68013内部的USB2.0的速度。由于存储器数据量大,为了提高效率,完成数据读取,CY7C68013芯片采用通用可编程接口(GPIF)数据读取方式。

GPIF是一个对于FX2端点FIFO的内部主控制器[3],它代替了外部的“胶合”逻辑电路,如果没有GPIF,则在FX2与外界之间必须建立接口电路。FX2固件程序能够分配FIFO读和写波形到4个FIFO中的任何一个,并且GPIF将向外界接口产生正确的选通信号,外界接口用于对FIFO数据的传进传出。

在数据读取过程中充分利用FPGA的可编程特性[4],通过扩展的1 Kbyte的FIFO来匹配时序完成数据的读取,FPGA在收到读指令后,首先从Flash中读取数据并写入其内部FIFO,并一直判断FIFO的满信号,当FIFO未满则一直写数据到FIFO,否则停止,保证数据不丢失。CY7C68013芯片端点FIFO的内部主控制器收到外部提供的握手信号(RDY0)变低后,GPIF也将产生CTL0的读FIFO信号,且当CY7C68013芯片内部FIFO数据满512 byte则自动打包上传,当握手信号(RDY0)变高,即FIFO为空时则停止读取数据。如此循环,直至完成数据的读取操作。

经过测试,完成6 Mbyte/s的数据读取速度,实验测试发现,将FPGA工作时钟由20 MHz提高到40 MHz,数据读取速度并没有改变,可以证明6 Mbyte/s已经达到了存储器的数据最大输出速率,通过分析Flash存储器读时序各个状态建立和保持时间,发现实验结果与理论分析相符。

5.2 实时图像显示

为了实现数字图像的实时传输,必须解决影响实时传输的几大因素:一是计算机中应用软件接收图像、处理并显示图像的速度;二是CMOS图像传感器与CY7C68013的FIFO缓冲区之间的传输速度;三是CY7C68013内部的USB2.0与带有USB2.0接口计算机之间的传输速度。针对这3个关键因素都采取了相应的解决方法。

计算机中应用软件接收图像、处理并显示图像采用MFC开发,以人机交互界面为主体,通过优化代码,采用多线程的方法,合理分配系统时间,确定优先级,完成实时图像数据的读取、存储、显示。计算机应用软件主要用途有:1)建立与外设的连接,发现USB设备,通过USB向图像采集设备发送指令并进行图像数据的实时采集存储;2)对从USB传输来的图像数据进行实时读取、显示;3)读取Flash存储器中的图像数据。

笔者采用由Cypress公司生产的EZ-USB FX2系列芯片中的CY7C68013芯片,该芯片是针对USB2.0的,它支持 2 种传输速率:全速(full speed)12 Mbit/s,高速(high speed)480 Mbit/s。实时数据传输要求CY7C68013芯片数据传输速率高于6 Mbyte/s,因此,将数据传输模式配置为高速(high speed)480 Mbit/s模式,保证数据传输的实时性。实时上传CMOS图像传感器捕获的图像数据与存储器数据读取方式一样。其速率通过实时传输实验验证了图像的连贯性。

6 实验结果

通过采集存储实验和实时显示实验,验证了该系统的可行性和实时性。图3是从实时显示实验中捕获的单帧图片。

7 小结

数字图像采集系统采用FPGA作为采集控制部分,优势有:

1)由于FPGA专门负责采集存储控制部分的实现,降低成本,增加了编程的灵活性。

2)设计结构简单,调试方便。FPGA的外围硬件电路简单,可以减小硬件设计的复杂程度。FPGA的时序逻辑调试可在软件上仿真实现,因而大大降低硬件调试难度。

3)系统具有独立性,可以独立完成数字图像的采集存储,不需要计算机的控制。

4)通过对系统添加视频压缩模块,可以实现更长时间视频信息的采集存储,作为运动目标检测跟踪硬件系统在图像捕获模块中已经得到应用。

[1]马利刚,马铁华.基于FPGA的实时图像采集系统设计[J].计量与测试技术,2009(12):51-56.

[2]Samsung Semiconductor.K9NBG08U5A datasheet[EB/OL].[2010-01-20].http://www.alldatasheet.net/datasheet-pdf/pdf/170554/SAMSUNG/K9NBG08U5A.html.

[3]钱峰.EZ_USB FX2单片机原理、编程及应用[M].北京:北京航空航天大学出版社,2007.

[4]谭树人,张茂军,徐伟.多传感器同步图像采集系统的设计[J].电视技术,2006,30(9):84-87.