2.4GHz CMOS线性功率放大器设计

2010-08-04秦国宾王宁章

秦国宾,王宁章

(广西大学 计算机与电子信息学院,广西 南宁 530004)

0 引言

高性能、低成本的CMOS工艺的进步,使得芯片上单位面积内可以集成越来越多的数字功能,从而可以采用复杂的编解码和调制解调算法,获得高性能的无线通信。功率放大器作为射频收发机中功耗和体积最大模块,其性能直接决定了整个射频收发机的成本、功耗和体积[1]。另外,随着通信技术的发展,信道容量急剧增加,许多无线通信系统都采用了幅度、相位组合调制技术,功率放大器在输出大功率时要防止发生幅度失真,这就对功率放大器的线性度提出了很高的要求[2]。因此,对CMOS线性功率放大器的研究具有重要价值。

1 电路设计

为了提高功率放大器的线性度,一些电路级线性化技术被提出,如源极负反馈,P沟道金属氧化物半导体(PMOS)电容补偿,双重器件等。在源极负反馈电路中,利用沃尔泰拉级数可以证明,电感性源极负反馈是提高线形度有效的方法。但是,源极负反馈对功率增益也会产生负面影响。源极电感只能在一定程度上提高线性度却会显著的降低增益,设计中要在功率增益和线性度之间进行最优选择[3]。

PMOS电容补偿的基本思想是与N沟道金属氧化物半导体(NMOS)功率放大器并行的放置一个互补的PMOS电容,PMOS电容特性与从 NMOS管栅极看进去的电容具有相反的特性[3]。这种方法的缺点是引入额外的PMOS电容,通常为了和NMOS管形成互补的电容特性,而且需要额外的偏置电路产生合适的PMOS管需要的偏置电压。

双重器件电路的基本思想是输出级采用两个并行的A类和B类功率放大器,因此整体的跨导是A类和B类放大器的跨导之和,即:

因为A类功率放大器的跨导和功率增益随输入信号的幅度的增加而迅速压缩,而B类功率放大器恰恰相反。所以在这种并行结构中,当输入信号较小时,A类功率放大器是整

一般MOS的漏极电流等效方程如下:体跨导的主要部分,而信号幅度较大时,B类功率放大器是整体跨导的主要成分,当二者以适当的比例相结合时,B类功率放大器有效地补偿了A类功率放大器的功率压缩,从而可以获得更高的l dB压缩点,也就是提高了功率放大器的线性度[4]。

在该设计中,采用双重器件的方法,在输出级并联辅助功率放大器(PA)电路,来补偿功率放大器的线性度。整体电路架构如图1所示。

由式(2)可知Vgs3对三阶交调失真(IMD3)有直接的影响,因此会影响到功率放大器的线性度。由N沟道金属氧化物半导体场效应晶体管(NMOSFET)的特性:当偏压点接近 VTH时,为正峰值;而当偏压点大于VTH时,gm"为负峰值。

在正常的情况下,输出级PA的偏压点均会大于VTH,其gm"为负峰值。可利用辅助PA偏压点在接近VTH时,gm"为正峰值的特性,与输出级PA并联,使得gm"的峰值相互抵消而变得平整。由于gm"的改善,进而改善整个电路的线性度。

辅助PA偏压点不同时,gm"的正峰值也不相同,因此输出级可以并联多个不同偏压点的辅助 PA电路,从而使gm"更平整近似常数,进而改善整体电路的线性度。但当并联的辅助PA电路过多时,会增加许多面积与产生更多的寄生效应,因此在选择并联PA电路时,并非并联越多的辅助PA电路越好[3]。在综合考虑改善整体电路线性度与相对增加的面积及寄生效应下,该设计采用一个辅助PA电路来改善线性度。

现设计了一个基于TSMC 0.18 µm CMOS工艺,工作在2.4 GHz的线性功率放大器,设计目标为P1 dBm大于20 dBm,效率(PAE)值大于23%,电路结构如图2所示。

图2 线性功率放大器的电路结构

主电路采用两级功率放大器架构,其中漏极偏压是1.8 V,加上电感达到扼流与匹配的效果。栅极偏压是0.8 V,加上电阻达到偏压、匹配、增加稳定度的效果。辅助PA电路在图2中用椭圆框标出,是利用NMOS加上独立的偏压电路所组成,其中源极偏压Vg=0.6 V。辅助PA电路着重于改善整体电路的线性度,因此源极偏压在接近次临界区处。

具体设计流程如下:

①选择A类的输出级以达到较佳的线性度;

②选用两级的架构来达到所需的目标,因为单级功率放大器无法达到较高输出功率;

③输出级:预计线性增益来反推所需的电流值,并利用高级设计系统(ADS)软件的负载拉移功能来测试在不同的Vg偏压下,所得到的输出功率与功率增加PAE值。做完输出级的匹配之后,可得知其输入功率约4.7 dBm、功率增益约18 dB;

④驱动级:也利用 ADS软件的负载拉移功能来测试在不同的Vg偏压下,所得到的输出功率与PAE值。因输出级的输入功率约4.7 dBm,所以驱动级的输出功率至少要有到5 dBm,才可达到输出级的需求;

⑤两级间采用直接电容耦合的方式,以节省不必要的电路元件;

⑥利用输出级并联辅助 PA电路,来补偿输出级的 gm"特性,以改善三阶互调失真(IMD3),提高线性度。

2 仿真分析

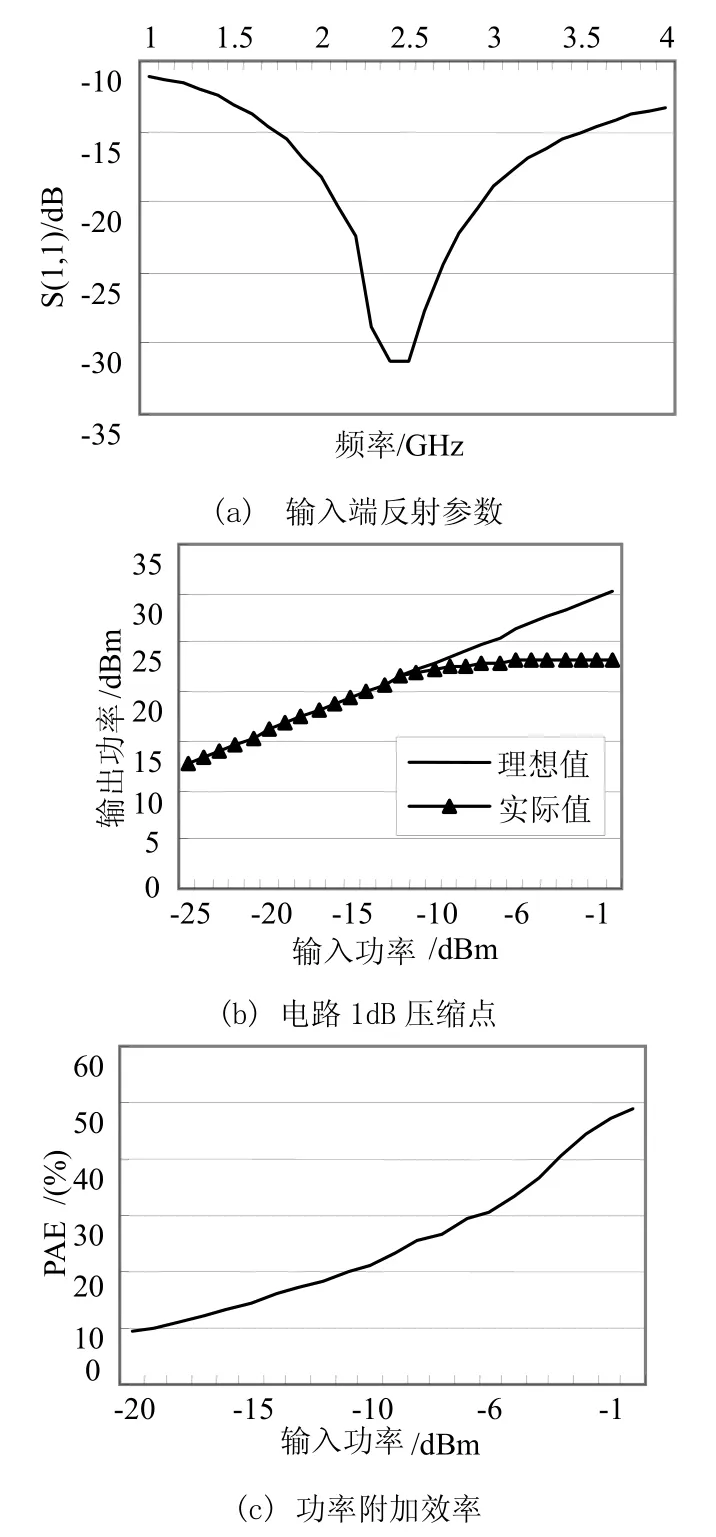

该设计基于 TSMC的 0.18 µm CMOS工艺,利用ADS2008U2软件进行设计和仿真,各项性能指标都取得了较好的效果。仿真结果如图3所示。

在设计过程中,充分考虑了片上电感品质因数不高、电感值较小和占有面积较大的局限条件。采用电流源 SRC2提供稳定的偏置电流,减少电阻的阻值随温度变化的影响。驱动级与输出级之间采用直接耦合电容的方式,减少不必要的元件。

由图3可以看出,图3(a)显示线性功率放大器中心频率工作在2.4 GHz,S11小于-30 dB, 说明回波损耗很小,输入匹配良好。图3(b)显示当输入功率为-7.8 dBm时,功率附加效率达到了26.67 %,相应的功率增益为30.6 dB。图3(c)显示1 dB压缩点为22.79 dBm,具有很高的线性度,各项性能指标均已达到预期要求。

在性能仿真过程中发现,电路各级的阻抗匹配对电路的影响都非常大,阻抗匹配是电路设计成败的关键。利用ADS软件的负载拉移功能是获取最佳输出匹配负载和预测晶体管输出功率和效率的有效且便捷的手段。此外,输出晶体管尺寸对整体电路的输出功率和效率有着密切的联系,存在最佳尺寸,使得电路主要性能达到最优化,但相应对电路的工作条件如驱动级电源电压等的要求更高。

图3 仿真结果

3 结语

分析了3种电路级线性化技术的优缺点,然后在TSMC 0.18 µm CMOS工艺下,采用双重器件,在输出级并联辅助PA提高功率放大器线性度的方式,利用ADS2008U2软件进行了电路设计与仿真,并对性能进行了研究分析,与国内外设计相比,该设计取得了较好的效果[4-6]。随着CMOS工艺和无线通信领域的不断发展,该设计可广泛应用于2.4 GHz开放频段的IEEE802.11b标准协议和蓝牙系统的发射模块。

[1] 王伟峰,夏立诚,王文骐.高速宽带应用的毫米波CMOS集成电路[J].通信技术,2007,42(06):70-72.

[2] 池保勇,余志平,石秉学.CMOS射频集成电路分析与设计[M].北京:清华大学出版社,2006.

[3] WANG C Z, VAIDYANATHAN M, LARSON L. A Capacitance Compensation Technique for Improved Linearity in CMOS Class-AB Power Amplifiers[J]. IEEE Journal of Solid-State Circuits, 2004,9(11):1927-1937.

[4] DING Y W, HARJANI R. A high-efficiency CMOS +22dbm Linear Power Amplifier [J]. IEEE Journal of Solid-State Circuits, 2005,40(09):1895-1900.

[5] 闫涛涛,周健军.1.6GHz高线性度低功耗CMOS驱动放大器[J].信息技术,2008,32(09):68-71.

[6] 李亮,李文渊,王志功.2.4GHz CMOS功率放大器设计[J].电子器件,2006,29(02): 348-350.