基于LVDS的高速数据传输系统的设计

2010-08-04杨翠虹

杨翠虹,文 丰,姚 宗

(中北大学仪器科学与动态测试教育部重点实验室,电子测试技术国家重点实验室,山西 太原 030051)

0 引言

随着信息技术的发展,特别是通信技术的发展,传统的数据传输方式由于速度慢、抗干扰能力弱、难以支持长距离的数据传输等缺点越来越不能满足技术应用的需求。LVDS技术和光纤通信的应用,解决了这一瓶颈。

LVDS是一种低振幅差分信号技术,使用幅度非常低的信号(约350 mV) 通过一对差分PCB 走线或平衡电缆传输数据,驱动和接收不依赖于供电电压5 V、3.3 V甚至2.5 V,保持同样的信号电平和性能[1]。它能以高达数百 Mb/s 的速度传送串行数据。由于电压信号幅度较低,而且采用恒流源模式驱动,故只产生极低的噪声,消耗非常小的功率,甚至不论频率高低,功耗都几乎不变。此外,由于 LVDS 以差分方式传送数据,所以不易受共模噪音影响。LVDS技术与同类技术相比较有以上一些优点,因此得到了广泛的应用。值得注意的是,LVDS信号本身只能满足短距离(不超过几米)传输条件下数据高速传输的要求,不能支持长距离传输。而自适应均衡器可自动为信号损耗提供补偿,使电缆传来的串行数字信号可以重新恢复其原有强度。利用这一特点,采用高速串行数字接口(SDI)自适应电缆均衡器及电缆驱动器芯片构建系统,可以扩大 LVDS技术的数据传送范围。光纤传输系统具有容量大,传输距离远,抗干扰性强等优势,在通信传输方面有着不可替代的地位。目前,单模光纤能以 1.2 Gb/s的速度传输2 km。

提出的基于LVDS的长距离高速串行数据传输系统是将光纤作为传输介质来传送 LVDS信号,以实现高速率条件下长距离传送的要求。

1 总体设计方案

该系统设计需要完成在信号在180 Mb/s以上的速度准确传输2 km以上。根据设计的需求和方案的合理性,弹上采集设备到地面设备之间采用同轴电缆通信,由标准SMA接插件连接,地面之间的传输采用光纤通信,由光模块连接。

图1为原理框图。计算机通过USB模块(USB2.0)下发命令并完成数据从设备到上位机的传输。弹上采编设备接收到命令后,开始采集数据。数据在传输过程中通过LVDS串行芯片DS92LV1023完成并行数据到串行数据的转化,通过解串芯片DS92LV1224完成并行数据到串行数据的转化;通过CLC001/CLC006和CLC012/CLC014一组电缆驱动芯片减小信号的衰减使信号能满足远距离传输的要求;通过光模块实现光信号与电信号的相互转化以满足光纤传输的需求。

图1 原理框

2 硬件实现

2.1 主要芯片简介

LVDS技术已经整合到驱动串行、接收解串等集成电路之内。DS92LV1023和DS92LV1224就是两款LVDS芯片,是美国国家半导体公司推出的10位总线型低压差分信号的应用芯片组。其中,DS92LV1023可将10位并行CMOS或TTL数据转换为具有内嵌时钟的高速串行差分数据流的驱动串行器;DS92LV1224则是接收该差分数据流并将它们转换为并行数据的接收解串器,它同时又可以重建并行时钟。这组器件进行数据串并转换时采用的是内嵌时钟,这样可有效地解决由于时钟与数据的不严格同步而制约高速传输的瓶颈问题。

CLC001/CLC006和CLC012/CLC014分别是高速驱动器和自适应均衡器。高速驱动器可以驱动电缆传输更长的距离。经由电缆长距离传送而来的信号都会出现衰减现象,自适应均衡器的作用就是将经由电缆传送的信号均衡。

2.2 同轴LVDS长线传输电路的设计

LVDS信号的传输必须依靠串行驱动电路和解串接收电路成对出现互相搭配来完成。其中,串行驱动电路和解串接收电路要正常通信,必须由外部提供工作时钟,而且工作时钟频率必须相等。由于 FPGA内部逻辑灵活多变,完全可以提供两个频率相等的时钟[2]。

弹上 LVDS驱动端:弹上采集的数据经过驱动串行器DS92LV1023串化后输出的差分信号压差为200 mV左右,若直接经同轴电缆(SYV-50-3-3系列,内部导体直径0.9 mm,衰减系数≤4.0 dB/m)传输只能传输 10 m左右。但如果这个信号再经过高速驱动芯片CLC001,通过调节电阻R23的阻值,输出压差可以达到2 V左右[3]。这样的差分信号经同轴电缆可以传输200 m以上的距离。具体电路如图2所示。

图2 弹上LVDS驱动端电路

地面转接LVDS接收端:地面转接设备主要接收从弹上设备传输的数据。具体电路如图3示。CLC014为电缆自适应均衡器,与高速驱动芯片 CLC001互相搭配,使经同轴电缆衰减后的信号均衡,增强差分信号强度,便于长距离传输而不失真。其中,R51为同轴电缆匹配电阻。接收解串器DS92LV1224与串行驱动器DS92LV1023互相搭配,使串行的LVDS信号转化为FPGA能够处理的并行数据。其中,R42为接收端终端匹配电阻[4]。

图3 地面转接LVDS接收端电路

2.3 光纤长线传输电路的设计

该传输系统地面转接设备到地面综合测试设备之间由于传输距离需要达到2 km以上,传输速度高达100 Mb/s,所有选用光纤通信。系统所选用光模块 OCM3723,信号输入电平范围为1.5~2.3 V。LVDS驱动串行芯片DS92LV1023的信号输出幅值小于800 mV,这个电压值如果直接接入光模块OCM3723的输入端,光模块根本不能识别。所以高速驱动芯片CLC006是必不可少的,它可以将DS92LV1023输出的弱电压增强到2 V左右,可以满足光模块OCM3723的信号输入电平范围。将光模块与 LVDS芯片连接方式的原理图结合具体的芯片应用到具体电路中如图4所示。

图4 光纤长线传输发送、接收电路

3 关键技术研究

3.1 采集速度与LVDS传输速度的匹配

该系统采用的LVDS传输速度范围是10~66 MB/s,而弹上采集设备采集速度只有576 KB/s。所以,需要将采集到的数据暂时存放在FPGA的FIFO中,存到一定数量,fifohf信号拉低,再将数据送给LVDS模块。LVDS的传输速度比采集速度快很多,fifo中的数据很快会被读完。读完后fifohf信号拉高,LVDS模块等待下一次读数。等到下一次 fifohf信号拉低时,LVDS模块再次同步需要500 µs时间,这样就会丢失掉500 µs的数据。所以LVDS模块通信不能中断。

系统采用以下方法解决LVDS模块通信不能中断问题。

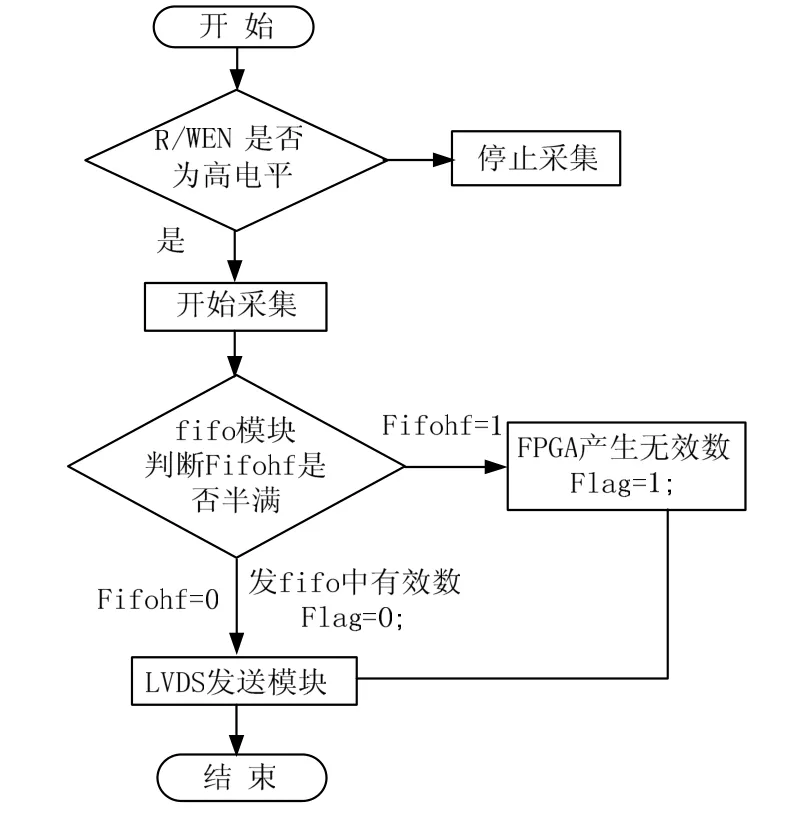

采编器的R/WEN信号高电平时,开始工作。如图5示。当fifo模块里的数全部送完后,将fifohf半满信号拉高。

图5 速度匹配流程

此时在FPGA程序中编译一些数据(无效数),并将这些无效数送给LVDS模块让其一直处于通信状态。由于LVDS模块传输的数据有两种:弹上采集设备采集到的有效数、FPGA产生的无效数,所以需要产生一个标志位 flag和数据一起送给LVDS模块,以方便接收数据端解码出有效数据。当 fifohf半满信号为低电平时,让 flag 为低电平,此时代表有效数即采集到的数据。反之,flag为高电平,代表无效数即FPGA自己产生的数据。DS92LV1023和DS92LV1224芯片有10个数据管脚,系统传输的数据为8位,有两位是空闲的,可以将其中一个管脚作为flag来用。

3.2 LVDS传输速度与光纤传输的匹配

LVDS传输与光纤传输的匹配问题需要解决两个问题:

①LVDS 芯片之间可以传输持续不变的数,但在LVDS与光纤之间不能正常传递,LVDS芯片会失锁。用示波器可观测到DS92LV1224的通信标志位LOCK:正常通讯时,LOCK为低电平,否则为高电平。LVDS可以传输10位数据,需要传输的数据是8位,所以只要让其中一位不断变化,问题就得以解决;

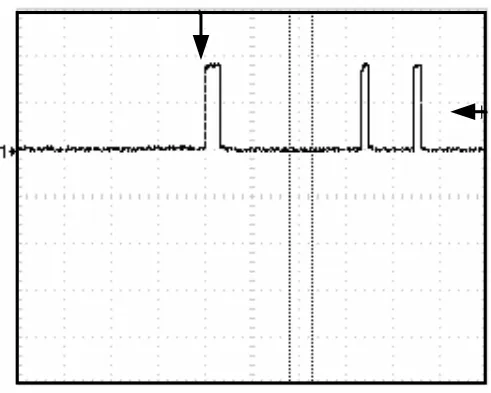

②在传输有效数与无效数分段传输时需要加一个Flag标志位,LVDS芯片数据位共有10位,如果将Flag标志位放在第九位时,在LVDS之间通讯没有问题,但加入光纤传输后,在接收端LVDS芯片会失锁,数据紊乱。如图6所示。图6是用示波器测量到的LVDS解串芯片的通信标志位LOCK,其中横坐标表示时间,纵坐标表示伏值,测量条件为:频率11.96 kHz,周期为83.61 µs,峰峰值3.84 V。从图中可以看出,LOCK信号有失锁的情况[5],故需要将Flag标志位放在第十位。

图6 DS92LV1224标志位LOCK

3.3 数据接收速度与USB传输速度的匹配

地面综合测试设备到上位机之间采用USB模块进行间歇式(GPIF方式)传输。这种方式是以数据包的方式传输数据,每次传输512个字节大小的数据包。LVDS的传输速度为18.432 MB/s(包括无效数),而USB模块传给计算机的速度最快为18 MB/s(只传输有效数据),所以可以将FPGA接收到的有效数据先暂时存放到内部FIFO中,当FIFO中数据达到512个字节时FPGA发出信号通知USB模块进行读数。USB模块将数据读入上位机后进入等待状态,等待FPGA的下一次读数命令。

4 结语

介绍了一种基于LVDS的长距离高速串行数据传输系统的设计方法,分别对同轴电缆传输 LVDS信号长线传输电路和光纤长线传输电路的设计做了详细介绍,并对设计中遇到的关键问题进行了研究,提出了具体的解决方法。该系统已经投入实际应用,图7为系统采集并传输回来的具体波形,可以看出系统可以完成信号在18.432 MB/s速度下不失真地传输2 km以上的距离,性能可靠、稳定,该方法值得推广。

图7 伏值为-10-10V试验波形

[1] 崔维嘉,樊少杰.新一代的总线结构—RapidlO[J].通信技术,2001(04):42-44.

[2] 毛继志,李建周,许家栋.基于FPGA的高速数传系统研究[J].微电子学与计算机,2005,22(11):104-107.

[3] 布明恩,杨文荣,张启平.8位 LVDS串行器的设计研究[J].微计算机信息,2005,21(01):103-104.

[4] 李泉,文鹰.利用FPGA与串行/解串行芯片HP1032/1034设计数字视频的复/分接[J].电子技术,2003(02):43-46.

[5] 李向阳.多通道LVDS的实现及传输错误处理[J].小型微型计算机系统,2005,26(08):1436-1440.