叠图机控制系统的硬件电路设计与实现

2010-07-10刘艳玲张铁锋

刘艳玲,张铁锋

(天津理工大学 机械工程学院,天津 300191)

0 引言

近年来,随着科学技术的不断发展,工程复印、大型绘图机等文印设备越来越普及,叠图机越来越被业界重视,叠图机的控制系统随着科技的发展也不断更新换代。本叠图机的硬件电路系统主要包括CPU主控电路系统,键盘显示系统,传感器系统和步进电机驱动系统,译码与控制信号选通的CPLD控制系统。

1 控制系统的硬件电路设计

在叠图机的硬件电路组成部分中, CPU主控电路采用美国ATMEL公司生产的8位AT89C52单片机,通过检测各个传感器信号、按键输入信号及不同的中断信号,产生各种程序执行过程,从而发出不同的步进电机驱动信号。在主控电路系统中采用一片CPLD,用它与单片机和各种芯片相连,产生各种芯片所需的译码选通信号与控制选通信号。键盘显示部分包括8个LED共阴极数码管,6个普通按键和一片MAX7219芯片。其中按键用来选择需要折叠和装订边的尺寸以及急停。共阴极数码管则用来显示所选择的纵向和横向折叠尺寸和装订边尺寸。MAX7219是串行输入/输出共阴极显示驱动器,他通过串行通信方式接收来自单片机发送的数据DAT,用来驱动数码管显示出所选择的尺寸。传感器系统包括6个端面传感器和2个槽型传感器,其中端面传感器用来检测图纸所处的位置,槽型传感器起导向作用。步进电机驱动系统包括2个步进电机的起停控制、正反转控制及速度控制。

1.1 传感器系统与键盘显示电路设计

CPU主控电路采用AT89C52单片机,传感器和按键的信号均为TTL电平,经两个74LS244N与P0口连接。通过实时的采集传感器和按键信号来控制叠图机的不同程序的运行。图1所示为单片机与传感器和按键的连接图。其中U101到U108分别为来自8个传感器的输入信号,P5.0到P5.5分别为来自6个按键的输入信号。其中6个按键A、B、C、D、E、F分别为:横向折叠尺寸选择键,纵向折叠尺寸选择键,纵向198定尺寸键(有中间折纸),纵向210定尺寸键(有中间折纸),纵向210定尺寸键(无中间折纸),和停止键。按键操作面板如图2所示。

图1 单片机与传感器和按键的连接图

1.2 LED数码管显示电路控制系统设计

主控电路中的AT89C52单片机通过RXD,P1.6,P1.7三个端口通过锁存器74LS240分别控制显示芯片MAX7219的片选CS、脉冲CLK和显示数据DIN。如图3所示为单片机与MAX7219的控制信号接口图。

图2 按键操作面板图

图3 MAX7219的控制信号接口图

显示系统与主控电路系统不在同一个电路板上,通过接插件CON5连接。MAX7219驱动8位LED显示器的电路如图4所示。

图4 MAX7219驱动8位LED显示器的接口电路图

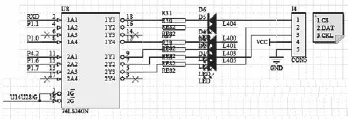

1.3 步进电机驱动控制系统设计

叠图机中用到两个步进电机实现叠图动作。本系统采用了4出线86系列的步进电机,通过配套的步进电机驱动器来实现单片机对步进电机的控制以及细分电路的实现。图5为单片机对步进电机驱动器的控制电路连接图。单片机通过P0口的DB0到DB3的4个IO口实现对2个步进电机驱动器的方向和脱机信号的控制。而驱动控制器的公共端信号接+5V信号。对于步进电机的脉冲信号控制,主要是先通过计算算出所需脉冲信号的频率,然后通过把数字脉冲信号分频成所需要的频率。在本系统中,脉冲信号的产生是通过8253作为单片机的外设,对74HC4060芯片输出的数字脉冲信号进行分频,提供频率可调的数字脉冲信号,实现步进电机的速度调节。如图6为脉冲信号产生的原理图。其中8253通道0和1设置成工作方式4即方波脉冲发生器,而8253的GATE0和GATE1分别由单片机的P1.2和P1.3控制,用以选通8253的通道0和通道1。OUT0和OUT1为8253提供给步进电机驱动器的脉冲控制信号。

图5 步进电机驱动器的控制电路

图6 脉冲信号产生的原理图

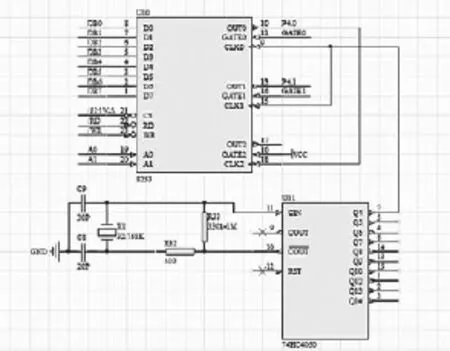

1.4 译码电路和控制信号选通电路系统设计

本系统采用Altera公司的MAXⅡ系统CPLD,利用VHDL语言来设计以上电路芯片的片的译码片选信号以及一些控制信号的选通。系统电路图如图2.7所示,其中A13、A14、A15是来自单片机P2口的输入信号,作为译码输出片选信号/8253CS、/LEDCS、/KEYCS、U14U28/G和U13CLK的状态位。MAXRES为来自看门够的输入信号,控制选通输出信号RST对单片机的复位。P4.0、P4.1是来自8253的输入信号,控制选通输出信号P1.0、P1.1对步进电机驱动器的脉冲输入。P5.3为来自停止键的输入信号,控制选通输出信号P3.3对单片机的外部中断1信号的输入。U103、U104、U105、U106、U107和U108分别为来自传感器的输入信号,控制选通输出信号P3.2、P3.4和P3.5对单片机的外部中断0,定时器0和定时器1的信号输入。

2 结束语

本文研究了基于单片机和CPLD的叠图机的硬件电路设计。详细介绍了叠图机控制系统的硬件电路组成和设计方法。对于步进电机的驱动采用现成的步进电机驱动器方法,提高了系统的稳定性。该系统经过实际验证能够提高叠图机的抗干扰性以及叠图准确性,克服了传统叠图机控制系统的不足与缺陷。

图7 CPLD系统电路图

[1] 吴红星.电机驱动与控制专用集成电路及应用[M].北京:中国电力出版社,2006.

[2] 李朝青,单片机原理及接口技术(第3版)[M].北京:北京航空航天大学出版社,2006.

[3] 王诚.Altera FPGA/CPLD 设计(高级篇)[M]北京:人民邮电出版社,2005.

[4] 高吉祥.数字电子技术[M].北京:电子工业出版社,2003,8.

[5] 宋受俊,等.两项混合式步进电机驱动器的优化设计[M].电气传动,2006,2.

[6] 韩广兴,等.电子元器件与实用电路基础[M].北京:电子工业出版社,2005.

[7] 陈学军.步进电机细分驱动控制系统的研究于实现[J].电机于控制应用,2006.