视频图像采集平台的研制

2010-07-09李世军周惠芳

李世军,周惠芳,李 强

(1湖南工程学院电气信息学院,湘潭411101;2湖南电气职业技术学院,湘潭411101;3.湘潭县电力局,湘潭411101)

随着计算机技术、电子技术、和通信技术的发展,数字图像处理技术在计算机和便携式系统中的应用越来越广泛.实现与应用数字图像处理的方式一般可分为三类:第一种是纯软件方法,独立使用计算机,通过软件的方法实现数字图像处理,采用这种方法的优点是系统资源(软硬件资源)丰富,处理效果好,但是由于不能脱离计算机,缺乏灵活性尤其是不能适应于便携式处理场合;第二种是硬件实现方法,采用基于专用的VLSI实现,例如基于FPGA的方式,处理算法纯硬件实现,并行处理速度高,可实现高速处理,如实现 JPEG压缩算法的 CL550、STII14、LS4702,实现MPEG 的CL950 、STI3500 等芯片.此类方法十分有效,因为可以针对专门算法进行高度优化,同时可以控制将系统的开销降为最低,其缺点在于系统中有大量的专用模块,当算法需要修改时,便无法适应新的需要,只能重新设计;第三种方法是软硬结合方法,其典型代表是DSP在数字图像处理领域的应用,这种方法以DSP为核心辅以少量外围器件构成一个数字图像处理硬件平台,在此基础上通过软件方法实现数字图像处理.

设计了一种基于DSP+CPLD的视频图像采集硬件平台.通过对CMOS图像传感器输出的彩色全电视信号进行视频采集,获得数字图像数据,以便实现数字图像的处理.以DSP搭建的硬件平台不失通用性,采用DSP的CCS软件开发平台的汇编语言和C/C++语言混合程序设计可以高效地实现各类数字图像处理算法,同一系统可以适应不同的数字图像处理应用,只需增加相应的算法功能模块即可,所以方案方便灵活,适应范围广[1].

1 系统硬件设计

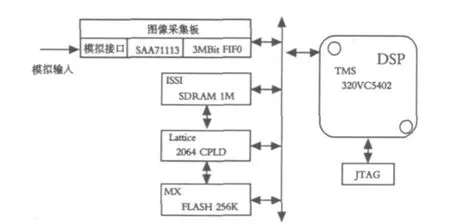

设计的图像采集与处理平台,能完成视频图像信号的采集、处理、存储等系列功能,可作为图像处理的一个通用平台,系统可以在不修改硬件的基础上应用于较为广泛的便携式图像处理场合,只需对其中的算法模块进行修改和扩充即可.如图1所示,TMS320VC5402是本系统的中央处理器,以它为核心扩展了包括存储器扩展、JTAG接口电路、电源监控电路,复位电路,图像采集板接口电路以及这些外围的CPLD时序控制电路等[1,2].

(1)TMS320VC5402DSP为主处理器,主要实现对视频数据的处理.在存储FIFO,存储SDRAM采用DMA方式进行数据传输,可以提高数据传输的速率.

(2)CPLD为系统协处理器,作为视频A/D对FIFO进行写操作,DSP对FIFO进行读操作的时序控制,以及整个系统的时序控制.

(3)图像采集板包括SAA7113和3Mbit FIFO.视频解码A/D芯片Philips SAA7113将模拟视频电视信号(本系统 PAL制)数字化.输出为符合CCIR.601标准的数字视频码流.FIFO AL422B作为A/D与DSP之间的数据缓冲,使A/D的转换速度与DSP读取A/D数据的速度匹配.

图1 系统硬件板原理图

2 CPLD控制外围电路的接口设计

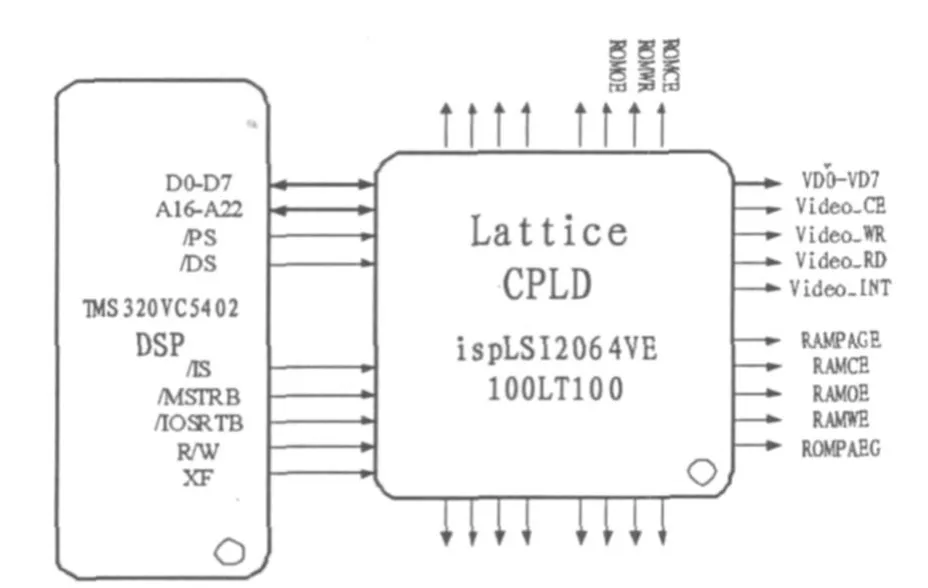

由于在本系统中各种外围接口电路多,系统的时序控制较为复杂,而且由于DSP的通用I/O口少,需要扩展I/O口.所以系统采用了可编程逻辑器件Lattice公司的isp LSI2064VE的贴片芯片.

如图2所示,将 DSP的输出控制信号/PS,/DS,/IS,/IOSTRB,/MSTRB(分别为程序空间、数据空间、I/O空间的选择信号,I/O选通信号和存储器选取通信号)作为CPLD的输入信号.CPLD输出的主要是各个外围器件控制信号,包括存储器(程序存储器、数据存储器)、视频图像采集板的片选,读写信号等.同时图像采集卡与DSP(D0-D7)的数据交换也是通过CPLD(VD0-VD7)进行的,以避免由DSP直接控制产生过多的等待周期[3].

图2 DSP与CPLD连接示意图

3 图像采集板接口电路设计

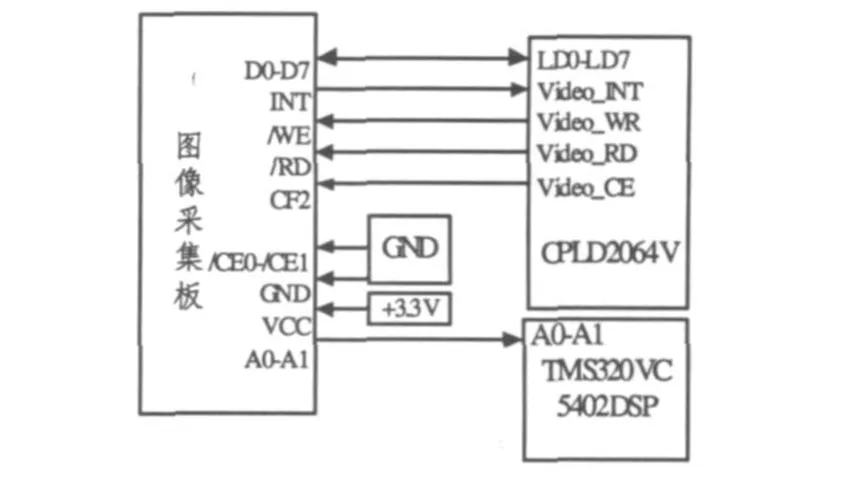

采集板电路由视频解码器、高速FIFO缓存和时序接口以及总线数据电路等组成,如图3中的图像采集板所示.采集板可以采用电源电压为5 V和3.3 V,可以直接与DSP接口.其数据接口是标准的8位并行总线,对其进行的访问方法与读写随机存储器(SRAM)类似.图4给出了图像采集卡连接示意图.其模拟信号输入可以直接输入PAL制彩色复合视频信号,本设计选用的是采集320×240点阵的16位彩色.

图3 DSP、CPLD与图像采集板连接示意图

3.1 图像采集与存储的关键问题

在进行模拟视频信号解码是采用专用的模拟视频信号解码器SAA71113,SAA71l13视频解码器是双通道模拟预处理电路、自动钳位和增益控制电路、时钟产生电路、数字多标准解码器、亮度/对比度/饱和度控制电路、彩色空间矩阵的组合,是一款功能完善的视频处理器.SAA7113接收CVBS(复合视频)或S-video模拟视频输入,可以自动将PAL、SECAM、NTSC模式的彩色视频信号解码为CCIR-60l/656兼容的彩色数字分量值,器件功能通过I2C接口控制.这样图像采集过程可以全部在后台完成,基本上不需要CPU的干预,可以节约大量的CPU时间.但是这样设计有一个难点:由模拟视频信号解码得出的数字视频信号数据量非常大,而且由于是实时视频信号,所以数据输出速率也非常高;但是相反,DSP外部存储器接口的读出速率却比较慢.为了解决这个问题,此板采取的是高速3 Mbit FIFO(数据先进先出),对数据进行暂存以缓解速度上的差异,即采用FIFO来暂存N行图像数据,视频解码器直接向FIF0中写入图像数据.当FIFO中写入了N行图像数据后,由CPLD向DSP发出中断请求;同时,DSP接到中断请求后,启动采集将N行图像数据从FIFO中读入到其外部SDRAM中存放.这样在采集的同时,DSP就可以读取已采集的N行数据,而不必等待一帧图像数据采集完成.这样提高DSP的处理效率.CPLD主要控制解码器向FIFO中写入数据以及DSP从FIFO中读出数据.系统可以采集到一帧图像的尺寸为320(点/行)×240(行),从 SA 71113输出的是 4∶2∶2的YcrCb数据格式,一个像素用2个字节表示,一个字节表示Y,另一个字节为Cb和Cr,那么总的数据量为320×240×2=150 KB.对于亮度信号,每个像素Y占一个字节,一行共320个字节,用320个存储单元存储一行的Y数据,对于色度信号Cb,一行共320点,每两个像素共用一个色度信号Cb,占一个字节,共160个字节,用160个字节单元存放一行的数据,对于色度信号Cr,存储格式与Cb一样.这样一帧图像数据需要的的缓冲区大小为:320×240+160×240×2=150 KB.对此扩展了两片521 K×16 bit的SDRAM,共1 M,而且选用了具有3 Mbit的FIFO来缓冲数据[1][4].

3.2 图像采集卡的输入输出模块逻辑设计

采集板的数据接口是标准的8位并行总线,对其的访问与读写静态随机存储器(SRAM)类似.DSP与采集卡的数据交换是通过DSP的I/O空间进行的,也就是采集板作为一个I/O设备.DSP对这个 I/O口设备进行读写.而且 8位数据通过CPLD缓冲与DSP低8位数据总线相接.采集卡包括三个片选 信号 CE2 、/CE1、/CE0./CE1、/CE0 直接接地,CE2的信号由DSP的IOSTROB,IO信号相与产生高电平片选;采集卡四个寄存器:采集控制寄存器、采集模式寄存器、采集像素数据寄存器和采集状态寄存器的地址AO,A1由DSP的低两位地址线AO,A1组合.它们的读,写信号由DSP在IO、IOSTROB有效下产生[5].其具体的时序控制程序如下:

4 实验结果和平台应用

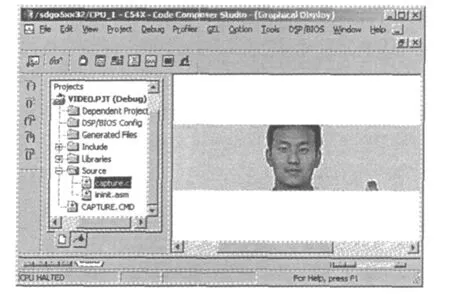

该平台采用“DSP+CPLD”的方案,将图像的采集与数据的处理分而治之,充分利用了TMS320VC5402 DSP进行高速数值运算的优势,同时还能够对图像采集板进行灵活的控制,因此本设计的实用价值显著.图4是采集到本人的头像320点×40行×16 bit彩色图.它们是通过CCS软件自带的Graphical Display功能显示的图像,由三个字节分别表示一个像素点Y、U、V三个分量,大小为37.5 KB,将其进行JPEG压缩编码处理,压缩后的图像大约为4.12KB,其压缩率大约为9.本平台以连续运行可采集连续动态图像,一幅320×240的彩色图像,需要由DSP启动图像采集卡一次,每秒钟可采集、显示达25帧,完全能满足实时视频处理的要求.该系统可以为一个通用的视频图像采集压缩处理平台,在该平台上可以实现JPEG2000,H.263,MPEG-2等多种多媒休压缩标准.

图4 采集的本人原头像(320×40×16位彩色)

[1]李世军,黄 锋,等.基于DSP的数字图像采集、压缩系统的设计与实现[J].电子技术应用,2009,(7).

[2]潘小东,等.FPGA+DSP的红外图像数据采集与显示[J].红外与激光,2007,(12).

[3]张伟伟,等.基于DSP和USB2.0的高速偏振图像采集处理系统[J].电子技术应用,2008,(9).

[4]周根荣,等.基于线阵CCD的织物图像采集系统[J].仪表技术与传感器,2007,(8).

[5]刘金清,等.DSP在网络视频图像采集中的应用[J].仪器仪表学报,2006,(3).