基于FPGA的图像处理电路的设计与实现

2010-07-02任文平申东娅李同宇

任文平,贾 赞,申东娅,李同宇

(云南大学 信息学院,云南 昆明650091)

随着微电子技术的高速发展,数字图像处理技术在电子通信领域和信息处理领域得到广泛应用,因此设计一种功能灵活、使用方便的图像处理系统具有很大实用意义。传统的图像处理系统一般采用单片机或数字信号处理器开发设计,这种设计方式用于数据处理量大、实时性要求高的图像处理时,就很难达到理想的设计要求。本文提出一种基于FPGA的设计方法,通过硬件电路软件化的设计方式,在一片FPGA上完成图像的采集、处理及显示等功能。与传统的设计方法相比较,不仅具有开发周期短、设计效率高、扩展性和升级性良好、设计灵活等FPGA器件的开发特点,而且由于采用硬件电路实现,因此在图像数据处理的速度上具有明显优势。

1 系统的设计方案

本系统是一个基于FPGA的数字图像处理显示电路,可以实现图像的灰阶变换、边缘检测及图像的压缩等功能。系统框图如图1所示,FPGA中包含了以下5个功能模块电路的开发设计。

(1)SDRAM控制模块:控制SDRAM存储器中图像数据的读出和写入。

图1 系统框图

(2)图像裁剪压缩电路:将图像进行压缩变换,使画面宽高比达到不同的比例,例如 16:9、4:3等,以实现不同的视觉效果。

(3)图像灰阶变换模块:对彩色图像进行黑白变化处理。

(4)图像边缘检测模块:对彩色图像进行边缘检测。

(5)显示控制电路:根据VGA显示屏的特点,产生时序驱动信号,控制处理后的图像数据显示。

图中灰阶变换、边缘检测、图像压缩3个模块输出的图像数据,通过切换电路送入VGA显示控制。

2 设计实现

2.1 SDRAM控制模块的设计

FPGA中本身自带容量为4 KB的存储器,但是考虑到图像的大小及今后对动态图像处理功能的扩展,本设计选用了存储容量为8 MB的外存SDRAM用于存储图像数据。SDRAM存储的容量大,但是其内部结构较复杂,8 MB的SDRAM在存储空间上划分了4个BANK区块,每个BANK有16 bit数据宽,因此对该器件的读写必须设计专门的控制器进行控制操作。由于本设计采用的图像色彩为 30 bit,RGB各 10 bit,显然用一个 16 bit宽度BANK不能存储一个像素,因此采用了2个BANK合并存储像素。这样,在SDRAM控制电路上需要仿真成4个虚拟的数据端口(2个写端口+2个读端口),在同一时刻将一个像素RGB从2个BANK中同时写入或读出,合并之后形成一个完整的数据。

SDRAM控制器的读写操作由2个子模块完成:控制信号产生子模块、状态转移控制子模块。控制信号产生子模块根据收到的信号产生各种控制信号,包括:清零操作、读写控制、地址递增信号等。状态转移控制子模块负责SDRAM控制器操作的状态转移及相应数据的传递。

2.2 图像压缩模块

在图像的压缩处理上,本设计采用了抽取算法,通过直接丢弃部分原始数据达到分辨率的压缩。例如将原来 640×480的分辨率变换为 320×240或 120×60的分辨率。这种算法虽然有图像信息损失,但是通过实际测试,图像显示能够满足一定的要求。特别是由于此方法不需要数学运算,所以数据处理速度快,尤其适用于一般要求的动态图像的处理。

2.2.1 像素的抽取

采用抽取法实现分辨率的压缩,必须丢弃行和列的部分像素。以变换320×240分辨率为例,具体的设计方法是,将分辨率为640×480的原图像每隔一行进行行标记,在标记的行里,每隔1个像素进行列表记,最后将行列都被标记过的像素取出,提供给显示控制电路。

2.2.2 双端口RAM控制模块

根据VGA的显示原理,VGA显示器要求行像素读取和显示同步,由于抽取出来的行列像素在时序上是不连续的,电路必须加存储器对提取的像素进行缓存。数据缓存模块可以选用任何存储单元,根据像素存取的特点,本设计选用了双端口的RAM对有效像素进行乒乓操作。双端口RAM乒乓操作的原理如图2所示。

图2 乒乓操作的流程图

在第N个周期,将输入的数据流缓存到“数据缓存模块1”,与此同时,“数据缓存模块2”中缓存的数据通过“输出数据流选择单元”的选择,送到显示电路。在第N+1个周期,将输入的数据流缓存到“数据缓存模块2”,与此同时,“数据缓存模块1”中缓存的数据通过“输出数据流选择单元”的切换,送到显示电路。乒乓操作的最大特点是:通过“输入数据流选择单元”和“输出数据流选择单元”按节拍相互配合切换,将经过缓存的数据流不停顿地传送到输出端,因此非常适合对时序不连续像素进行流水线式处理。

根据双口RAM乒乓操作的原理,被抽取出来的像素,一行被缓存的同时,另一行则被顺序读取,保证了像素显示的连续与同步。

2.3 图像的灰阶变换模块

图像的灰阶变换的处理上,有2种方案可选。一种是使用简便公式:

第二种采用经典公式:

2种方法相比,第一种方法虽然简单易行,但是处理效果不是十分理想。本设计采用第2种方法,但是这种方法涉及到浮点运算,而FPGA及硬件描述语言不能方便地处理浮点运算。解决的办法是对公式进行变形:将整个运算式进行放大缩小处理。针对上式,先将算式左右两边放大 512倍,也就是 29,相当于<<9,公式变形得:

最后将计算出的结果再缩小512倍,就得到了灰阶的真实数据。

2.4 图像的边缘检测模块

2.4.1 Soble边缘检测的原理

常用的边缘检测算法通过梯度算子来实现,经典的梯度算子有:Sobel模板、Kirsch模板、Prewitt模板、Roberts模板、Laplacian模板等,在求边缘梯度时,需要对每个像素位置计算。在实际中常用小区域模板卷积来近似计算,模板采用N×N的权值方阵。在众多的图像边缘检测算法中,Soble算法具有计算简便、检测效果好等优点,是一种被广泛应用的算法。

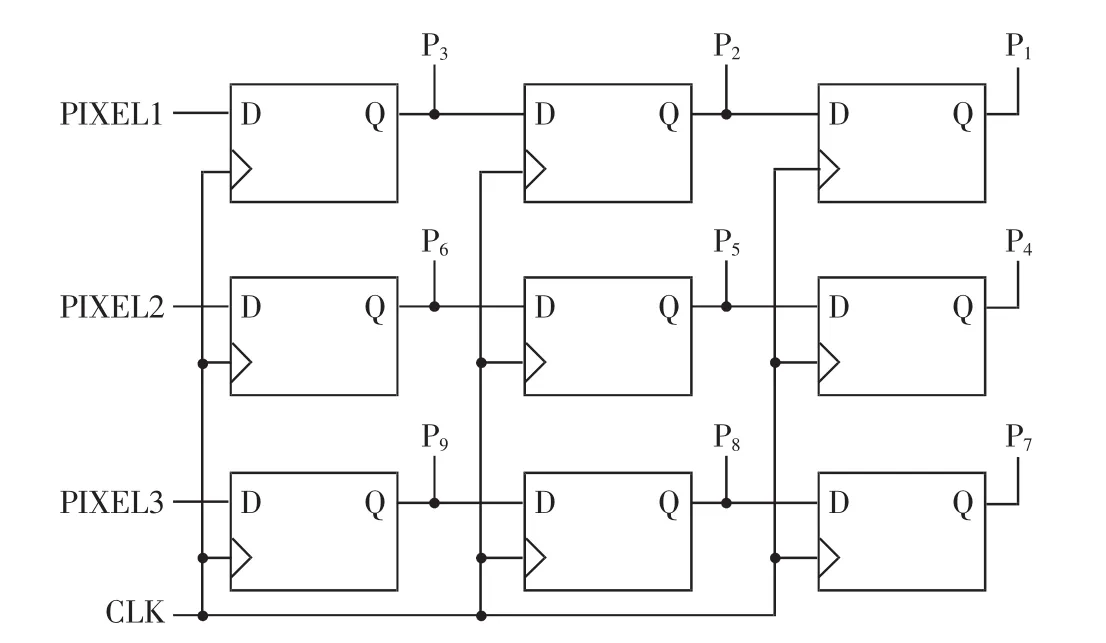

Sobel算法依据图像边缘的灰度值会产生突变的原理,对像素的灰度值进行处理。在图3所示3×3像素窗中,P1-P9为相邻的 9个像素,中间像素P5为待检测像素,根据Sobel算法将对此像素窗中P5进行灰度值滤波运算。计算如公式(4)、公式(5)、公式(6)。

图3 3×3像素

上式中 X、Y是两组 3×3的 Sobel矩阵算子,分别为横向及纵向的权值。A为像素窗中的9个相邻的像素矩阵。Gx及Gy分别代表经横向及纵向边缘检测的亮度差分近似值。G为边缘检测值,若此幅值大于给定的某阈值,则可判定像素点P5为边缘像素,否则为一般像素。边缘检测算法的实现涉及复杂的计算步骤,故对处理速度有较高要求。采用FPGA器件实现系统设计是一种纯硬件的解决方案,该方案可以使系统具备较高的实时性,能比较好地解决处理速度问题。

2.4.2 图像的边缘检测的实现

根据 sobel算法,对于像素 P5点的边缘检测,利用公式(6)计算完成,计算的关键是获得P5像素的8个相邻像素。这8个像素由下面2个模块电路获取:(1)像素窗接收模块,作用是将像素划分成3行成为一个像素处理窗;(2)像素窗数据刷新模块,电路如图4所示,作用是将接收的串行像素并行输出,并随着时钟的节拍,将每个数据向下一列传递,即进行数据的更新。

图4 像素窗数据刷新电路

从图4可以看出,经过上面的电路处理后,可以同时获得与P5相邻的8个有效像素,调用FPGA内的乘加运算、平方运算及平方根运算等电路模块,就可方便地计算出梯度G的大小,并通过与阈值比较来决定此像素是否为边缘像素。

图5 VGA的控制模块输出信号的仿真波形

2.5 VGA显示控制模块

显示控制器主要用于输出VGA显示器所需要的RGB数据信号和控制信号,根据输入时钟,显示控制器可以产生VGA所需要的控制信号,包括场同步、行同步和复合消隐信号等。输出像素则与输入像素相同。

3 系统的测试

本设计通过综合、仿真、下载后对预存在SDRAM中的图像进行了相应处理,处理后的图像清晰,达到了较好的处理效果。

本设计采用了基于FPGA的EDA设计,通过硬件电路软件化的设计,在一片FPGA上完成图像的压缩、边缘检测、灰阶变换及显示等所有功能。实测表明,各模块电路不仅对图像实现了较好的处理效果,而且充分体现了硬件电路的速度优势,这是传统的设计方法所不能比拟的。

[1]张志刚.FPGA与SOPC设计教程[M].西安:西安电子科技大学出版,2006.

[2]薛明星.基于 FPGA器件的 Sobel算法实现.电子元器件应用.2008(10).

[3]萧鸿森.如何 REAL TIME产生灰阶影像.http://www.cm.blogs.com.

[4]ALTERA公司.NIOS2嵌入式处理器设计大赛-2006年优秀作品选.西安:西安电子科大出版,2007.

[5]李国刚,余俊.基于 FPGA的图像 VGA图形控制器的实现方法[J].信息技术,2006(7).