在FPGA设计中ChipScope与MATLAB的应用

2010-06-14李辉,岳田

李 辉,岳 田

(中国电子科技集团公司第五十四研究所,河北石家庄050081)

0 引言

现场可编程门阵列(FPGA)具有规模大、逻辑复杂度高、配置灵活以及可完成复杂时序功能等特性,在当今的数字信号处理领域被广泛采用,且其速度、集成度越来越高,功耗却越来越小。通过对FPGA加载不同的程序可以实现不同的功能,达到设计重用的目的,从而可以大大缩短开发时间。在进行FPGA内部设计时,如果要观察FPGA内部节点的信号,传统方法是通过编程,把内部节点信号连接到FPGA的外部管脚上,通过示波器或逻辑分析仪观察,但这种方法存在很大局限性。为解决这些问题,Xilinx公司推出虚拟逻辑分析仪ChipScope Pro工具将硬件逻辑分析模块和源设计都集成到FPGA中。不需额外的测试管脚,通过JTAG(Joint Test Action Group)口就可看到内部节点信号,改变了传统的测试方法,缩短了开发周期。

1 与MATLAB结合应用

1.1 问题提出

在ChipScope中对信号采样的数据为逻辑值,可以将ChipScope作为逻辑分析仪来使用,用以观测信号的逻辑变化是否满足实际要求。或者将多个信号的采样数据设置为总线形式观测,将ChipScope作为一个简易示波器来使用,用以观测信号的幅度范围、直流点变化等信号特性。但是这种观测只是一种直观的观测,数据量较小时,可以对数据一一对比,确定是否正确,但若想得到观测数据的准确特性,就需要对采样数据做进一步分析,而这是ChipScope不能做到的。尤其当采样数据量非常大、需要对数据做统计分析时,单纯采用ChipScope就无能为力了。而目前在数字信号处理方面应用最广泛的数据分析及仿真软件是MATLAB,于是产生是否可将采样数据导入MATLAB进行进一步分析的想法。通过笔者进行实验,发现这是可行的,而且效果很好,并且还可以作为一种测试手段使用。下面以数字白噪声产生模块为例说明如何将ChipScope与MATLAB结合应用。

1.2 解决方法

首先白噪声产生模块采用的是Box-Muller算法与中心极限定理,具体描述如下:

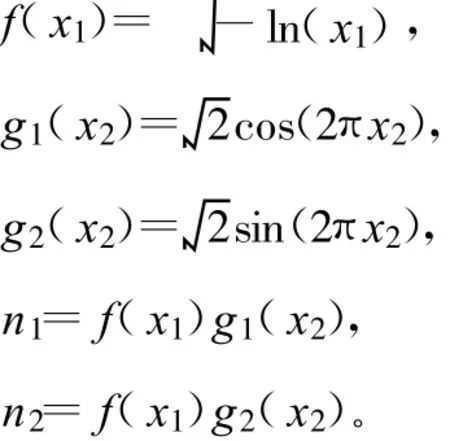

式中,x1和x2为2个独立的在(0,1)上服从均匀分布的随机变量,利用上述公式进行变换后产生的n1和n2即为服从N~(0,1)的白色高斯随机数。上述变换即为Box-Muller变换。

数字白噪声算法的FPGA实现原理如图1所示。

图1 随机噪声产生示意图

在进行算法的FPGA设计时,一般情况分为3个阶段:①在MATLAB下进行算法仿真,分析各模块的性能,确定各模块采用的算法及量化比特;②FPGA硬件描述实现,功能及时序仿真;③FPGA设计程序编译,下载程序文件产生,实际数据输出测试。第1步算法仿真完成后硬件的实现模型也就建立完成了,剩下的任务就是在FPGA中实现算法,并且验证算法的正确性。在FPGA实现过程中,第2步的功能及时序仿真都可以通过仿真软件将仿真结果存成文件交到MATLAB中进行输出数据的比较及分析,以验证仿真结果是否与MATLAB仿真吻合,不断修正算法的FPGA设计,最终完成算法的实现。而在最后的程序下载到FPGA阶段,对最终实现的模块输出数据的验证只能通过ChipScope对输出数据采样来实现。在对类似于数字白噪声产生模块这种FPGA设计,尤其需要对最终实现结果进行大量的数据采样、统计分析,验证结果是否正确,而不能只靠很少的采样就认为模块设计符合要求。对最终模块设计进行数据统计分析操作步骤如下:

①在完成功能及时序仿真的FPGA设计中,加入ChipScope调试工具的ICON核(集中控制核)、ILA核(集成逻辑分析核)及VIO(虚拟输入输出核),选择需要采样的感兴趣信号,如白噪声模块中的n1和n2以及噪声输出OUT1和OUT2。其中VIO核用以模拟外部控制信号,在例子中模拟的是信噪比的量化值。然后对整个工程进行编译产生比特流文件,通过JTAG口下载到FPGA中;

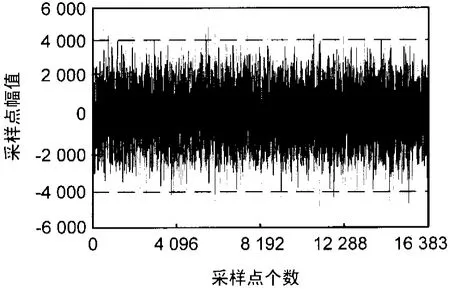

②打开ChipScope Pro Analyzer,可自动检测到设计中包含的ICON核、ILA核及VIO核,选择感兴趣的信号,建立总线形式,根据实际信号形式选择有符号数还是无符号数,通过VIO配置模拟的信噪比值,然后采样,选择Bus Plot项,即可观测到采样的波形,类似于在示波器上观测信号。例如在数字白噪声产生模块中选择对OUT1采样,采样长度为16 384(可设置的最大长度),信噪比配置为 6 dB,在ChipScope Pro Analyzer中信号波形显示如图2所示。

图2 ChipScope对 OUT1采样波形图

MATLAB仿真的结果在信噪比为6 dB时,噪声幅度大致分布在[-1.5,1.5]区间之内。而在数字白噪声产生模块设计时,规定信号为1,设定1量化为4 096,从图中可以看出,数据大致分布在[-6 000,6 000]区间当中,归一化后,噪声输出大致分布在[-1.5,1.5]区间当中,与仿真结果吻合。这只是从采样波形上的一个直观判断,而具体的数据特性如何,是否符合高斯白噪声特性,在ChipScope Pro Analyzer中无法得到。

如此大量的采样数据靠肉眼是无法判断结果是否与MATLAB算法结果吻合。测试步骤为:首先在ChipScope Pro Analyzer中选择File菜单中的Export…,选择文件格式为ASCII,然后在Core栏中选择感兴趣的ILA单元,在Signals Export中选择要导出的信号形式。例如笔者感兴趣图2中所示波形,因此选择Bus Plot Buses项,然后点击Export按钮,选择保存的目录及文件名,然后可得到一个扩展名为*.prn的ASCII文件。在MATLAB中可以将此ASCII文件直接打开,可看到文件格式如表1所示。

表1 ASCII文件格式

从表中可以看出,第1行表示变量名称,其他行为数据,文件的前2列为采样计数,实际意义不大,数据处理时可不用考虑,最后一列对应DataPort(即OUT1)的采样值。在MATLAB中编辑此文件,将第1行删除,只留下数据,然后保存。在MATLAB里面利用[load ASCII文件名]指令即可将采样值导入到MATLAB工作空间中,得到的数据为16 384行、3列的矩阵变量,变量的第3列即为采样数据。然后可以利用MATLAB工具箱的各种数据处理及分析函数对采样数据进行处理和分析。

2 实例分析

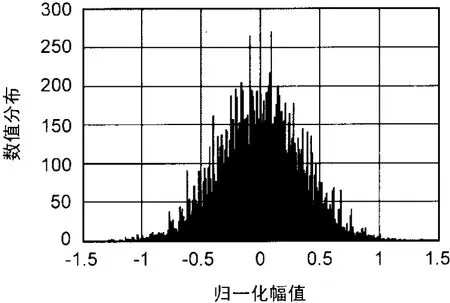

本文采用此方法对所设计的高斯白噪声产生模块的输出进行分析,以验证所设计的白噪声输出是否正确。我们知道,高斯白噪声的概率分布由其均值μ和标准差σ唯一确定,需要对采样数据进行统计分析,得到均值和标准差。设定信噪比为6 dB(此时高斯白噪声标准差 σ为 0.354 4),采样点为16 384,采样波形如图2所示。由于设定1量化为4 096,所以将得到的采样数据除以4 096得到幅值归一化的数据,然后对幅值归一化后的数据导入到MATLAB后利用统计函数MEAN(求均值)和STD(求标准差)对数据进行分析得到如下结果:

mean is……-9.031296e-004

std is……3.548564e-001

可以看出,输出结果的均值近似为0,标准差接近设定的标准差,出现的小偏差是由于统计数据量较小的原因,设计输出结果满足要求。为了更直观地观察产生数据的分布,在[-1.5,1.5]归一化幅值区间上做二维直方图,如图3所示。可以看到数值的分布接近正态高斯分布。对数字白噪声产生模块设置不同的信噪比值,得到不同的数据采样,采用以上方法估计得到不同信噪比条件下的均值与标准差,均得到与MATLAB仿真吻合的结果。根据均值及标准差的统计结果可以得出以下结论:设置不同的信噪比值,得到符合设置条件的数字白噪声输出,数字白噪声输出模块满足设计要求,工作状态可靠。

图3 白噪声数据的归一化二维直方图

3 结束语

随着FPGA规模的不断增大,通过示波器或逻辑分析仪观察FPGA内部节点信号的传统方法已越来越凸现其局限性。ChipScop作为内嵌的IP核,为设计者提供了一种可以观测FPGA内部节点信号的方法,而且通过与MATLAB相结合使用,极大方便了设计者对FPGA的调试、结果分析和故障判断,大大缩短了设计开发时间,提高了FPGA设计的可靠性,并且提供了一种对FPGA中模块输出数据进行统计分析的有效方法。可以预见到,在今后的FPGA设计中,ChipScope与MATLAB结合应用将是一个趋势。

[1]UG029.ChipScope Pro 10.1 Software and Cores User Guide[S],2008.

[2]GHAZEL A,BOUTILLON E,DANGER J L,et al.Design and Performance Analysis of a High Speed AWGN Communication Channel Emulator[C].IEEEPACRIM Conference,Victoria,B.C.,2001:374-377.

[3]万 翔.ChipScope Pro在FPGA调试中的应用[J].计算机与网络,2005,31(21):58-59.

[4]薛小刚,葛毅敏.Xilinx ISE 9.X FGPA/CPLD设计指南[M].北京:人民邮电出版社,2007.

[5]董长虹.Matlab信号处理与应用[M].北京:国防工业出版社,2005.