基于ITS信道模型的HF信道模拟器的实现

2010-06-14焦培南李铁成

谭 帅,焦培南,李铁成

(中国电波传播研究所青岛分所,山东青岛266107)

0 引言

长期以来,HF信道模拟器一直被认为是研究短波系统性能的有效手段。通过使用HF信道模拟器有利于短波系统的验证,以及在相同的信道状态下研究不同信号的适应性,降低前期研发的难度和成本。然而要能够真实地反映HF信道,信道模型的选取很重要。目前使用较多的是Watteron信道模型和ITS信道模型。由于ITS信道模型能够精确地仿真出各种类型的传输条件,适用于窄带以及带宽高达500 kHz的信号,故本文中的HF信道模拟器是在ITS信道模型的基础上实现的。

1 信道模型与系统结构

1.1 ITS信道模型[1]

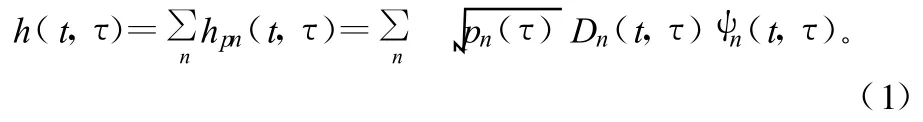

无线电信号通过电离层传输后会产生时间展宽、多普勒频移和多普勒展宽,即通常所说的时间色散和频率色散。在ITS信道模型中用下面的脉冲响应函数来描述[1]:

式中,n为路径数;pn(τ)为时延功率剖面函数,其服从Gamma分布;Dn(t,τ)为确定性相位函数,表示多普勒频移;ψn(t,τ)为随机调制函数,用来描述多普勒的展宽,有Gaussian和Lorentzian两种方式[2]。

1.2 HF信道模拟器的系统结构

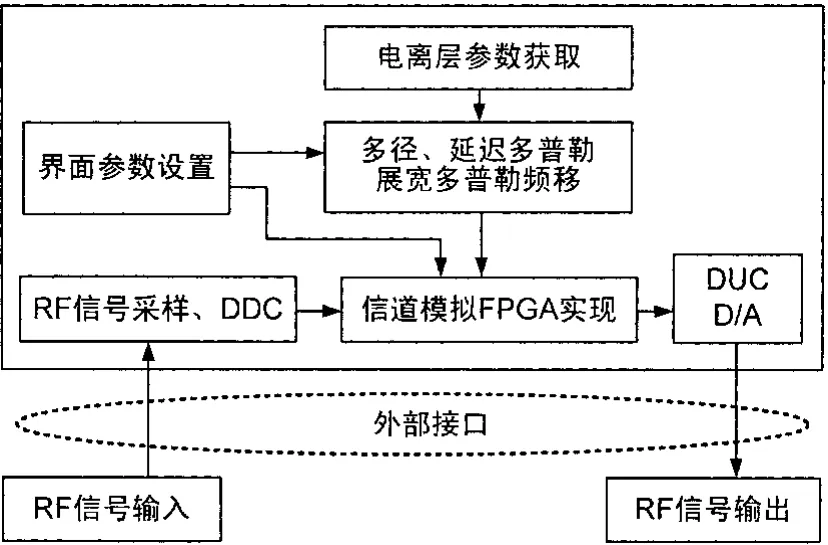

HF信道模拟器基于软件无线电的思想,通过对输入信号的采样,采用数字下变频方法把得到的数据流下变频到1.024 MHz,然后输入到现场可编程逻辑门阵列(FPGA)中。信号的时域展宽、频移和频谱展宽以及加性噪声都在FPGA内实现。变换后的数字基带信号通过数字上变频、DA转换后变换到需要的频率后输出。

HF信道模拟器的结构框图如图1所示。

图1 HF信道模拟器的系统结构

模拟器内部能够提供信道的激励信号和采样脉冲信号。内部激励信号和采样脉冲信号分别由2个AD9852产生。由于AD9852能够产生正弦波、线性调频信号等多种信号形式,而信号的幅度可通过系统内部的数字衰减器任意调节,调节精度达到0.5 dB,故基本可以脱离外部的激励器。采样脉冲输出固定为正弦波。同时模拟器以板卡的形式通过PCI总线与主机连接,信号的各种参数控制可以通过主机轻松设置,这就给研究不同信号的在短波信道种的适应性带来了很大的方便。由于输入信号和采样脉冲信号都具有内外切换的功能,故在具有特殊要求的情况下可以使用外部提供的信号。

主机内部运行的控制程序主要由电离层模型和参数控制组成。电离层的各项参数可以通过外部提供或内部产生。外部提供的方式主要由具体的实验数据,经过特定的电离层反演算法得到。内部产生主要是在给定的电离层模型的基础上,利用射线追踪技术得到不同时间、地点的信号的传播模式和时延。

2 信道模拟的FPGA实现

2.1 时延展宽

由于FPGA的速度高,时钟频率能够轻松达到上百MHz,实现μ s级的信号延迟分辨率很容易做到。主机通过解二元方程后得到的信号时延展宽参数存储到时延展宽寄存器中。利用与数据速率相等的时钟信号做触发,读取寄存器中的数据与相应延时的信号做乘积运算,实现时延展宽。

2.2 信号的多普勒频移

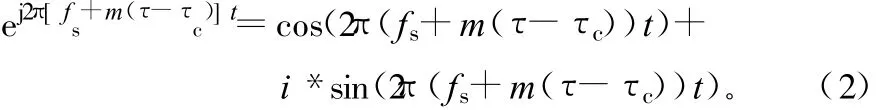

信号的频移由确定性相位函数Dn(t,τ)确定。其中fs为信号延迟为 τc时的信号频移,m为信号在时延宽度内的多普勒频移倾斜的斜率,τc为利用射线追踪方法计算出的信号延迟。通过查找表的方法实现信号的频移。

根据欧拉公式有:

由式(2)可知,多普勒频移值只与时延τ有关,并假设在积累的时间内信号频移不变。

已知下变频后数据的速率为1.024 MHz,在本设计中设定的信号频率精度为0.05 Hz。则相邻2个采样点数据的相位精度为:

由于相位是作为查找表的寻址地址,则要满足上面的要求,在2π弧度内所需的信号的存储单元为20 480 000个,所需要的存储器的长度为:

计算得N≥25,故可知要到达0.05 Hz的分辨率使用的存储器的容量为32 M与使用数据位的长度的乘积,如此海量的存储器价格昂贵,同时增加了设计难度和成本。故需要通过使用优化算法,在满足要求的同时降低存储空间。

2.3 信号的多普勒展宽

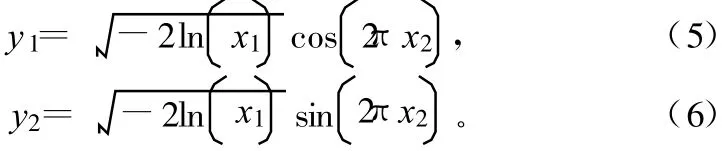

根据随机过程理论可知,通过HF信道的信号是一个随机过程。从时域上看,每一个触发周期即为一次样本函数。在每个时延点处的信号幅度是一个随机变量,同时各延时点处的信号幅度是独立的。而对相同延时的信号来说在时间上具有一定的相关性,时间上的这种相关性决定了信号的多普勒展宽和形状。通常使用的多普勒展宽为Gaussian和Lorentzian型。实现多普勒展宽的方法有多种。此HF模拟器中通过采样高斯滤波器得到FIR滤波器,用2路高斯白噪声通过该滤波器实现多普勒的展宽。2路高斯白噪声由m序列码产生的均匀分布的白噪声通过Box-Muller变换得到。

Box-Muller[3]变换公式如下:

式中,x1,x2为服从(0,1)上的均匀分布,并相互独立。

根据ITS信道模型理论,产生每一路延迟信号的多普勒展宽的均匀分布的随机信号相互独立。故对于时延展宽为n的信道来说,需要产生2*n个独立的随机序列。已知在多普勒频移的产生中已经建立了正余弦表,因此这里的正余弦也由查表法产生。故这里只需增加对数表就可以利用查表法,用产生的均匀分布序列作为地址得到需要的高斯白噪声信号。信道的加性高斯白噪声,同样使用上面的方法来实现。

3 线性调频信号的仿真

在已知信道的脉冲响应后,需要把抽象的数学公式通过硬件来实现,则需要大量的前期仿真。通过仿真实现算法的可实现性。本文对广泛使用的线性调频信号进行仿真。高斯白噪声经过高斯滤波后的时域图如图 2所示。

图2 高斯白噪声经过高斯滤波后的时域图

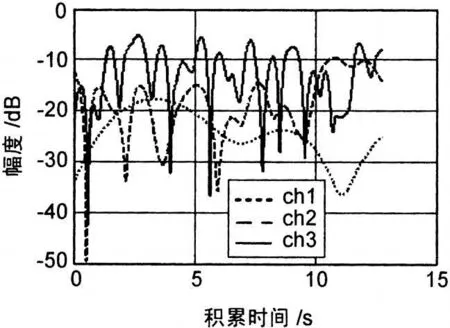

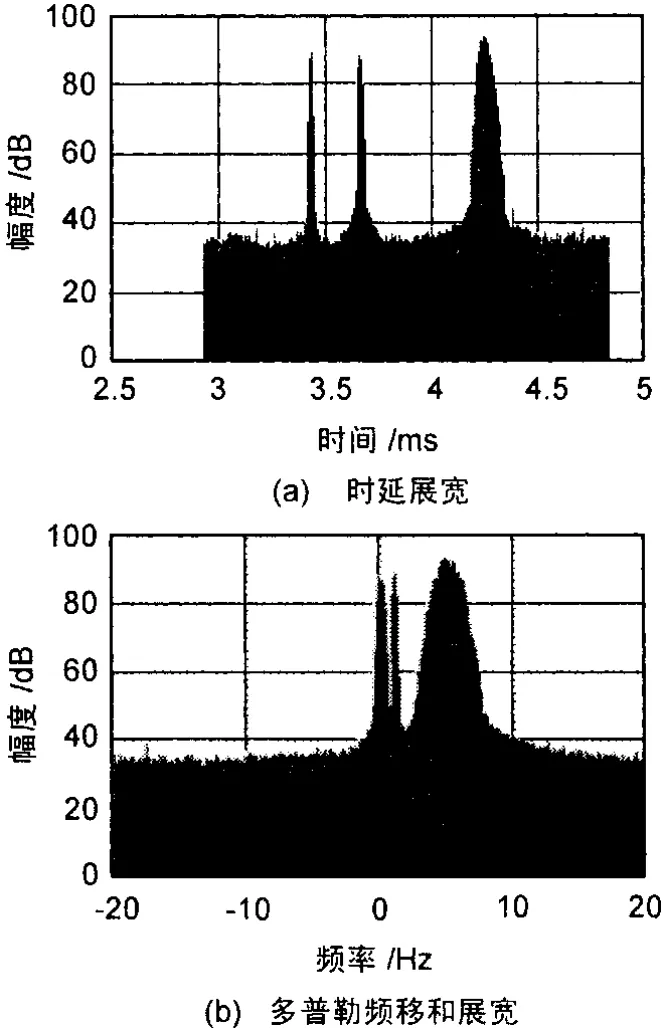

信号的频移和展宽如图3所示。

图3 信号的频移和展宽

线性调频信号参数设定如下:带宽为500 kHz,重复周期为40 Hz,脉冲宽度为5 ms,下变频后的速率为1.024 MHz。路径数为 3,分别为 ch1、ch2和ch3。tao为时延,其中ch1的参数为:信号时延为taoc1=3.431 ms,信号展宽为31 μ s,当tao=taoc1 时的多普勒频移为1 Hz,当tao=taoc1L(tao1L为路径1的时延最小值,下同)时的多普勒频移为1 Hz,多普勒展宽为0.1 Hz。ch2的参数为:信号延迟时间taoc2=3.663 ms,信号展宽为40 μ s,当tao=taoc2 时的多普勒频移为0 Hz,当tao=taoc2L时的多普勒频移为0 Hz,多普勒展宽为0.2 Hz。ch3的参数为:信号延迟时间taoc3=4.244 ms,信号展宽为150 μ s,当tao=taoc3时的多普勒频移为5 Hz,当tao=taoc3L时的多普勒频移为5 Hz,多普勒展宽为1 Hz。

4 结束语

随着技术的进步,FPGA的处理速度得到很大的提高,外部时钟很容易达到几百MHz。同时片上集成了大容量的RAM、乘法器和丰富的外部接口。利用FPGA来实现HF信道模拟器,使设计得到简化,利于算法的优化。利用VHDL语言编程实现的各功能模块不受器件本身的限制,具有很强的可移植性。由于ITS信道模型同时考虑了信道对宽带信号的时延展宽和频谱展宽,这就给信道模拟器带来了很大的难度。然而利用FPGA可以很容易地实现信号的时延展宽。通过FPGA能够很容易产生均匀分布的M码信号[4],便于实现信号的频谱扩展。由于ITS模型能够精确模拟各种信道传输条件,故设计一种基于ITS信道模型的信道模拟器具有很重要的意义。

[1]MASTRANGELO J F,LEMMON J J,VOGLER L E,et al.A New Wideband High Frequency Channel Simulation System[J].IEEE Trans.Commun.,1997,45(1):26-34.

[2]VOGLER L E,HOFFMEYER J A.A Model for Wideband HF Propagation Channels[J].Radio Science,1993,28(6):1131-1142.

[3]BOX G E P,MULLER M E.A Note on the Generation of Random Normal Deviates[J].The Annals of Mathematical Statistics,1958,29(2):610-611.

[4]管 宇.用FPGA产生高斯白噪声序列的一种快速方法[J].设计参考,2008,10(11):55-58.