基于数字电视基带SoC芯片的可测性设计

2010-06-07乔树山

孙 博,黑 勇,乔树山

(中国科学院 微电子研究所 专用集成电路与系统实验室,北京 100029)

1 引言

随着半导体技术的发展,芯片的集成程度不断提高,规模不断增大,越来越多的设计出于开发时间以及开发效率的考虑,开始采用SoC设计方式,将已有的可复用IP核集成在一个芯片上实现某种功能。虽然SoC有诸多优点,但其复杂程度也使芯片的测试面临新的考验,需要付出更多的时间和成本。典型的SoC芯片中通常包含PLL,A/D,D/A等模拟单元,片内存储器,CPU核和ASIC核等IP核,这些模块都有不同的故障表现形式,因此,需要根据各自特点采用不同的测试方法。选择合适的测试方案对于SoC的可测性设计非常重要。

近年来,国际组织以及企业都对数字电视产业投入了极大的热情,并制定出许多成熟的标准,比如欧洲的DVB-T标准、日本的ISDB-T标准以及中国的CMMB标准。本文以一款500万门级数字电视SoC芯片作为设计实例,描述基于该款SoC芯片的可测性设计方案。由于SoC芯片中多种模块需要不同的测试方法,本设计采用测试控制模块统一控制各种测试,节省片外管脚。针对片内存储器,采用存储器内建自测试(Memory Build-In-Self-Test,MBIST)的方法进行测试。其余数字逻辑采用基于扫描链的扫描测试,利用片内PLL进行实速测试,可测试多种故障类型,最大程度地覆盖所有故障点,以达到较高的测试覆盖率。同时采用测试压缩减少芯片的测试成本。

2 芯片结构及测试目标

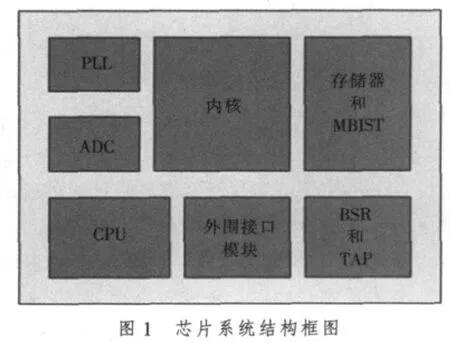

本文介绍的数字电视基带SoC芯片包含1个PLL,2个AD,1个8051处理器核,215块片内存储器以及大量数字信号处理模块和外围接口模块,芯片结构如图1所示。

该芯片可测性设计的主要目标是对逻辑部分以及存储器部分提供较高的测试覆盖率,同时尽可能减少测试所消耗的硬件资源、测试时间和测试数据,以减少芯片的测试成本。

3 边界扫描

边界扫描测试主要用于检测芯片与PCB板级以及芯片与芯片之间的互连故障,也用于检测芯片内核的功能。同时边界扫描由于其灵活的应用方式也被广泛地用于芯片功能的调试以及芯片内部多种工作参数的配置。

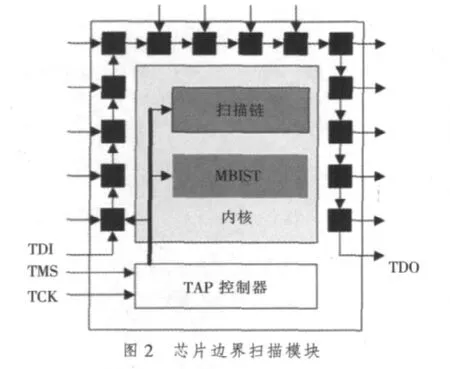

本设计中,芯片的边界扫描模块除了实现IEEE1149.1强制要求的EXTEST,BYPASS,SAMPLE,PRELOAD这4条指令之外,还增加了对片内存储器内建自测试模块以及扫描链的控制,通过这个集中的测试控制单元可以灵活地在这几种测试模式之间切换,减少了专门用于测试的管脚,同时使芯片的多个测试单元能够整合起来形成一个测试系统[1],芯片的边界扫描模块如图2所示。

4 存储器内建自测试

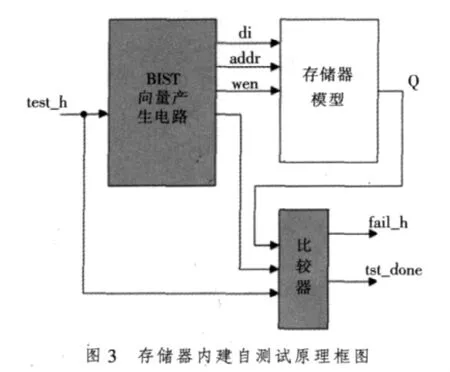

存储器内建自测试(MBIST)是目前大规模嵌入式存储器测试的主流技术。MBIST技术的基本原理是在存储器的外部产生一整套外围电路,包括测试控制电路、地址发生器、数据发生器和结果比较电路等,如图3所示。通过施加几个激励信号,实现存储器自动测试,最后输出故障或者测试结果。虽然MBIST增加了芯片的面积,但是其存储器测试自动化以及可以实速(At-Speed)测试的优点仍然使其成为存储器测试最理想的技术[2]。

数字电视基带SoC芯片的片内存储器多达215个,约占芯片面积的70%,因此存储器的成品率对芯片的设计和制造至关重要。如何合理的划分存储器,让多个存储器共用MBIST,在增加的芯片面积和测试时间之间折中,是本次MBIST设计的重点。根据芯片的布局规划,考虑到芯片的时序问题,将215个存储器划分为6组,相应地设计6个MBIST,每个MBIST控制多个RAM或ROM,每组存储器的内建自测试并行进行,组内存储器的内建自测试串行进行。为了测试和诊断的方便,通过TAP灵活配置MBIST的控制寄存器,可以激活全部MBIST,让其并行进行,也可以激活部分或单个MBIST以便于诊断。

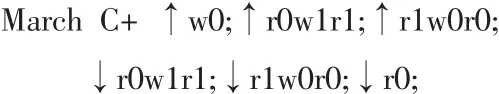

MBIST采用March C+算法,覆盖固定型故障、转换故障、耦合故障以及开路故障。算法描述如下,其中,↑表示存储器地址递增,↓表示存储器地址递减,w表示写操作,r表示读操作:

MBIST的实现极大地提高了片内存储器的测试效率,其增加的芯片面积对SoC芯片总的芯片面积影响非常小,仅占总面积的0.3%。

5 基于扫描链的ATPG

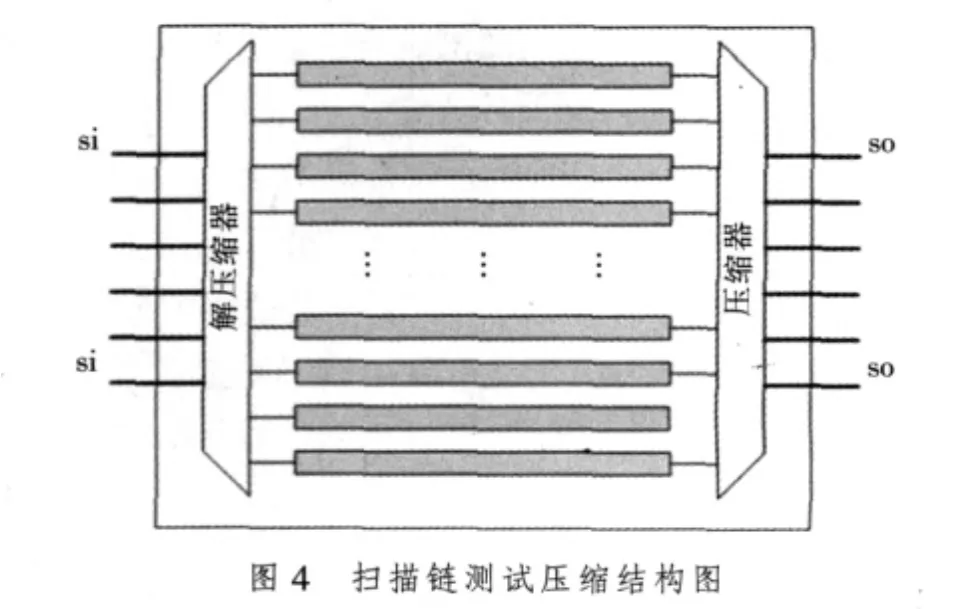

数字电视基带SoC芯片采用130 nm标准CMOS工艺制造,由于130 nm以下芯片会带来更多的时序相关的故障,因此仅测试Stuck-At故障无法满足实际生产需要,必须对芯片进行实速测试。同时为减少测试时间和测试数据,采用了测试压缩结构[3],如图4所示。

芯片包含20条扫描链,在测试压缩模式下压缩比为20,包含480条扫描链。基于MUX的扫描触发器结构,采用类全扫描设计,只有不到1%的触发器没有连接到扫描链中,主要是时钟单元、复位单元、FIFO和边界扫描模块中的触发器。

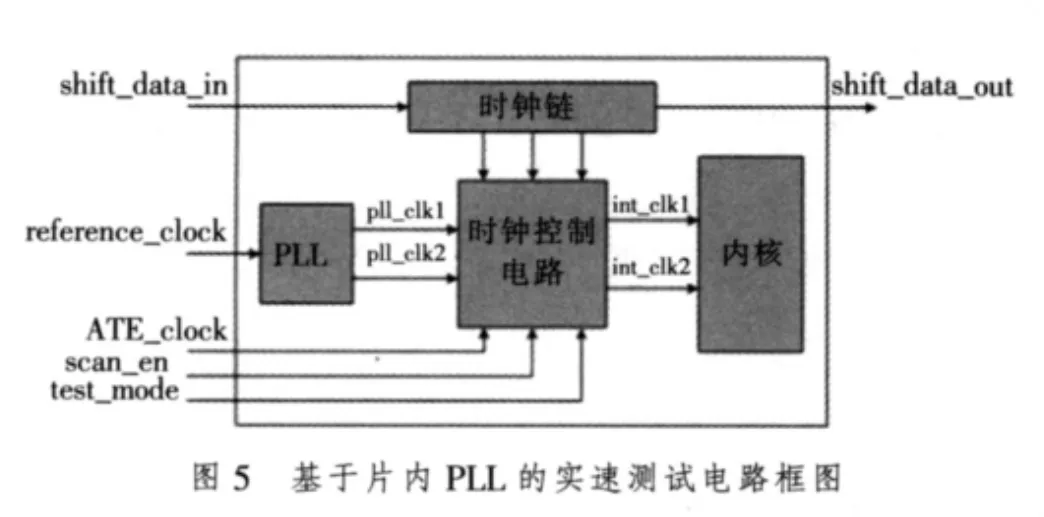

在实速测试模式下,用于测试的Launch Clock和Capture Clock由片内PLL提供,如图5所示。在切换(shift)过程中,扫描链时钟由低速的ATE_clock时钟提供。在捕获(capture)过程中,由片内PLL提供芯片正常工作模式下的时钟,由Clock Controller控制两种状态的切换。基于片内PLL进行实速测试的设计既提供了精准的实速测试时钟,又降低了对ATE设备的要求和测试成本[4]。

芯片包含215块片内存储器,如果不做任何处理,这些存储器在自动测试图形生成(Automatic Test Pattern Generation,ATPG)过程中将被视为黑盒子,即ATPG工具仅知道这些模块的端口,不知道这些模块的逻辑行为。在测试模式下,与存储器数据线、地址线相连接的逻辑不可观,与存储器输出端相连接的逻辑不可控,存储器周围的逻辑均不可测,严重影响测试覆盖率。为了提高芯片的测试覆盖率,需要针对这种情况对存储器做特殊处理,可以选择的方法有:1)利用多路选通器旁路存储器;2)在存储器的周围插入测试点;3)为ATPG工具建立特殊的存储器模型。考虑到前两种方法会增加很多的测试逻辑并增加芯片的面积,同时有可能对芯片的时序约束产生负面的影响,本设计最后采用的是第3种方法,即为存储器建立简单的ATPG工具可以识别的行为模型,在利用ATPG工具生成测试向量时,让ATPG工具分析存储器的逻辑行为,并生成测试向量,覆盖与存储器相连接的逻辑。在芯片测试过程中,会对片内存储器进行数据读写操作,在捕获阶段,需要多个时钟周期。这种方法可以得到最大的测试覆盖率,不仅包括存储器周围的逻辑,也包括存储器内部的逻辑[5]。与将存储器设置为Black-Box的方法相比较,测试覆盖率有3%的提高。

6 实验结果

本次可测性设计的对象为数字电视基带SoC芯片。芯片采用130 nm标准CMOS工艺制造,工作频率为60 MHz,所用EDA工具软件均为Synopsys公司产品。

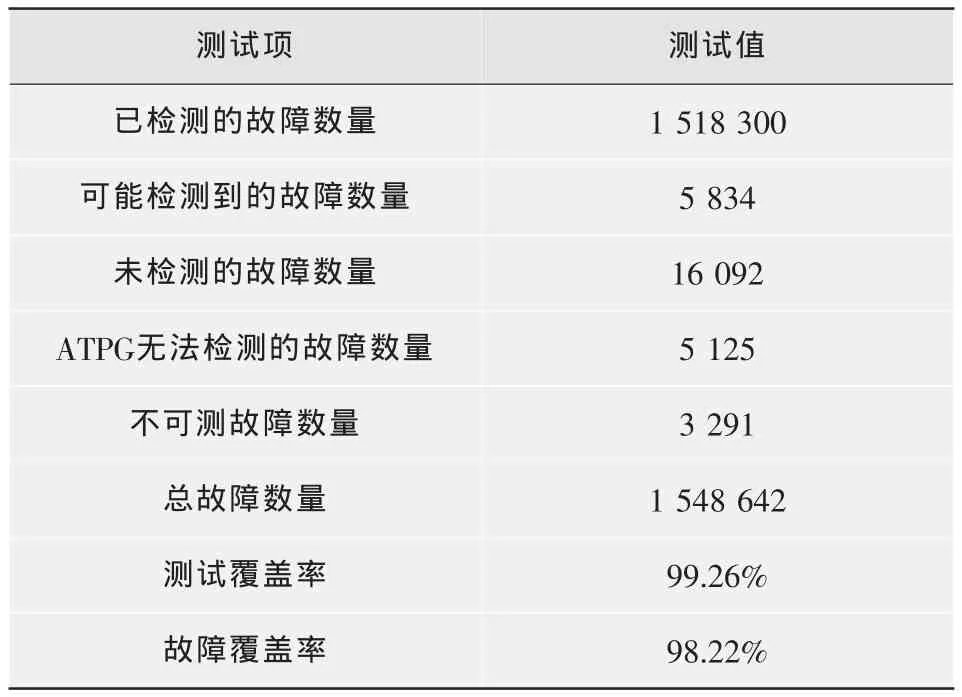

实验对Stuck-At故障和转换故障两种故障模型进行测试,以下给出SAT(Stuck-At-Transition)故障的测试结果。表1是在没有测试压缩的情况下的测试结果,扫描链条数为20条,扫描深度最大为2041。表2是在有测试压缩的情况下的测试结果,压缩倍数为20倍,扫描深度为74。

表1 非测试压缩条件下SAT故障覆盖率

表2 测试压缩条件下SAT故障覆盖率

由测试数据对比可知,非测试压缩条件下的测试覆盖率和故障覆盖率稍小于测试压缩条件下的数据。对两种情况下没有覆盖到的故障点进行分析可知,在非测试压缩情况下,测试压缩模块被旁路,该模块内的电路无法测试,造成了覆盖率的降低。

同时对比分析两种情况下的测试时间,在没有测试压缩的情况下,测试时间为测试压缩的11倍。如果不考虑测试压缩模块对覆盖率的影响,两种情况下的测试覆盖率没有明显的变化。硬件开销上,测试压缩模块增加的芯片面积不足0.4%。经过测试压缩之后,芯片的测试成本大大降低。

7 小结

笔者针对一款500万门级数字电视基带SoC芯片进行了边界扫描测试设计和存储器内建自测试设计,以及可以利用片内PLL进行实速测试和可以测试压缩的扫描设计。实验结果表明,经过合理的可测性设计,可以得到很高的测试覆盖率;同时经过测试压缩,可以大大降低测试成本。一款SoC芯片中不但包括数字部分,也包括模拟部分,本文的可测性设计仅针对数字部分,对于SoC芯片来说,这是不全面的。模拟部分的测试将在接下来的工作中继续进行,以完成一个全面的、高质量的SoC芯片可测性设计。

[1]ERLANGER S,BHAVSAR D K,DAVIES R.Testability features ofthe Alpha 21364 microprocessor[C]//Proc.International Test Conference 2003.Charlotte,NC,USA:[s.n.],2003:769.

[2]王晓琴,黑勇,吴斌,等.嵌入式存储器MBIST设计中内建自诊断功能研究[J].电子器件,2005,28(4):893-895.

[3]蔡志匡,黄凯,黄丹丹,等.Garfield系列SoC芯片可测性设计与测试[J].微电子学,2009,39(5):595-596.

[4]范小鑫,李华伟,胡瑜,等.采用片内PLL实现实速扫描测试的方案[J].计算机辅助设计与图形学学报,2007,19(3):367-369.

[5]TAN P J,LE T,NG K,et al.Testing of UltraSPARC T1 microprocessor and its challenges[C]//Proc.IEEE International Test Conference,2006.Santa Clara,CA,USA:[s.n.],2006:1-10.