基于NiosⅡ处理器的TFT-LCD图形显示设计

2010-05-18石红晓吴光敏

石红晓,吴光敏

(昆明理工大学 理学院,云南 昆明 650093)

随着工艺技术的发展与市场的需要,超大规模、高速、低功耗的FPGA不断推出,并且被广泛地应用在高速、高密度的数字电路设计领域。SoPC[1](System on a Programmable Chip)是一种基于FPGA的SoC设计方案,它将FPGA及微处理器的核心嵌在同一芯片上,构成一个可编程的SoPC系统框架,具有高度的集成能力,很大程度上减小了产品体积以及外部信号对系统的干扰,大大增加了系统的可靠性、稳定性和灵活性。本文介绍一种基于NiosⅡ软核处理器实现对LCD控制显示图形的方法。在设计中,利用Altera的FPGA的 SoPC Builder定制NiosⅡ软核处理器及其与显示功能相关的“软”硬件模块,来协同实现控制显示的软硬件设计。

1 系统设计

在工业控制和消费电子领域,LCD的显示技术呈现出越来越多的方式。本设计采用基于NiosⅡ处理器的液晶显示图形的设计方法,在SoPC Builder中以自定义接口的形式利用总线方式对LCD控制器进行设计,LCD控制器[2]一端接收用户控制,一端实现LCD复杂时序,并集成多种功能。用户只需要与控制器的简单接口交互,便能达到控制LCD的目的,进而编写应用程序,实现显示汉字、图片、画图等功能。本文的设计方法大大降低了工作量,加快了数据的处理速度和扫描频率,提高了各个功能模块的集成度,改善了系统的性能和可靠性。

本设计最终实现了一个基于Altera公司的DE2开发板的TFT—LCD控制器对已知图形的显示。

2 硬件设计

2.1 系统的整体结构

SoPC系统基于Avalon总线与其他系统构件来通信,整个SoPC系统设计中的外设通过Avalon总线模块连接起来,并且总线规范为外设端口与总线模块之间的数据传输提供了互连模型。

本设计的SoPC系统整体结构如图1所示。

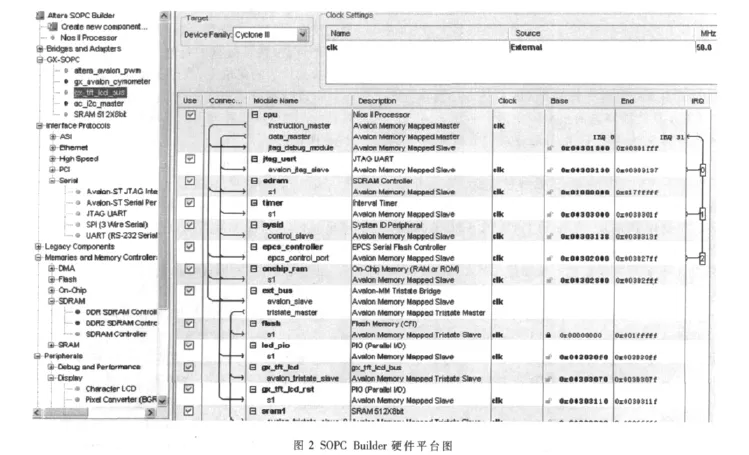

2.2 SoPC系统建立

基于FPGA的SoPC方案[3]的可配置性表现在搭建硬件平台时,用户可以根据自己要实现的功能来灵活选择所需要的存储器以及外围接口设备,而不用把所有提供的元件添加到系统中,这样就可以因功能不同而有针对性地设计每一个系统,从而也避免了添加无用元件占用FPGA资源而引起浪费。例如,由系统的整体结构可知,本系统所需要的基本组件有CPU、SDRAM控制器、JTAG-UART、SRAM、定时器以及用三态桥来连接的CPI-FLASH,因为在 TFT-LCD已经带有控制器了,所以就不需要以自定义组件的形式在SoPC Builder中添加该元件的控制器。

图1 系统整体结构图

本系统的构建基于QuartusⅡ8.0版本的SoPC Builder工具,它使用CPU、存储器接口和外围设备(例如本设计中添加的挂接在三态桥上的接口gx_tft_lcd)生成系统模块,并在Avalon总线模块和所有系统组件上的从属设备端口之间自动生成互连逻辑。由于利用总线方式来访问已经带有控制器(TCB8000A)的TFT LCD,因此需要在NiosⅡ系统模块中手动添加一个三态接口gx_tft_lcd。因为是只创建一个接口,因此不需要HDL文件和HAL文件,但是在信号设置时,应根据Avalon总线三态从端口写时序图和TCB8000A的控制接口来添加需要的信号。

设置生成新元件后就可以将新定制的gx_tft_lcd添加到Nios系统中,产生Nios II系统模块,并添加到工程中。保存编译,通过之后可将编译生成的sof文件下载到FPGA芯片,至此硬件方面的工作基本完成。

图2所示为搭建本设计的硬件平台中使用SoPC Builder工具来添加生成的系统模块。

3 软件设计

Nios II处理器的软件程序设计使用HAL(Hardware Abstraction Layer)系统库。HAI系统库[4]为程序员提供了应用程序与底层硬件交互的设备驱动接口,简化了应用程序的开发,同时还为应用程序与底层硬件驱动划分了一条很清晰的分界线,从而大大提高了应用程序的可复用性,使得应用程序不受底层硬件变化的影响实现系统硬件和应用程序之间的通信。HAI API[5](Application Program Interface)集成了 ANSI C标准库,使上层程序像访问C函数库一样访问系统硬件和软件。软件设计不用考虑底层硬件实现的细节而直接编写应用程序。系统软件结构如图3所示。

软件系统主要分为两部分:系统的初始化对LCD控制器的控制以及显示数据的处理。

系统初始化,调用HAL的各模块初始化程序,并定义在后面程序当中要用到的各个对LCD显示屏背景颜色、字体颜色设置的函数。

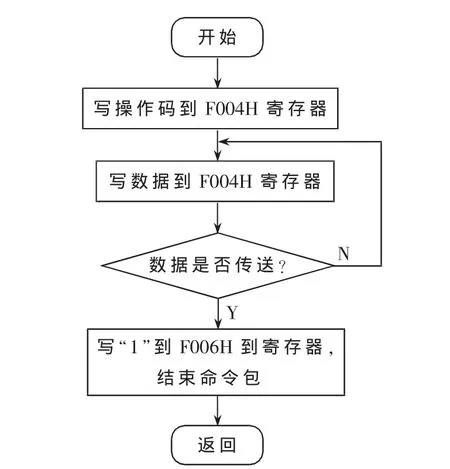

本设计采用总线方式[6]对 LCD控制器(TCB8000A)的时序进行控制,利用SoPC Builder添加完一个挂接在三态桥上的接口,将TCB8000A的控制引脚与Avalon总线相关联。由于TCB8000A的控制时序与Avalon总线三态接口的时序吻合,因此只需在定制接口时调整等待、建立时间便可以达到控制目的。在Nios程序内用简单的写操作产生Avalon总线时序,需要注意的是TCB8000A只需一个地址控制线A1,且与总线的A1相连,因此写操作应使总线上的地址线A1符合TCB8000A对A1管脚的时序要求。即在并行模式下,MPU首先把完整的命令包送入地址为F004H的只写寄存器(A1=0),然后将“1”送到地址为 F006H的寄存器(A1=1),结束一个命令包,并打开显示。对于地址线A0,A2~A17使用的控制板已经设定好了,所以只需要控制A1便可完成命令的送入。流程图如图4所示。

图3 系统软件结构图

图4 设计流程图

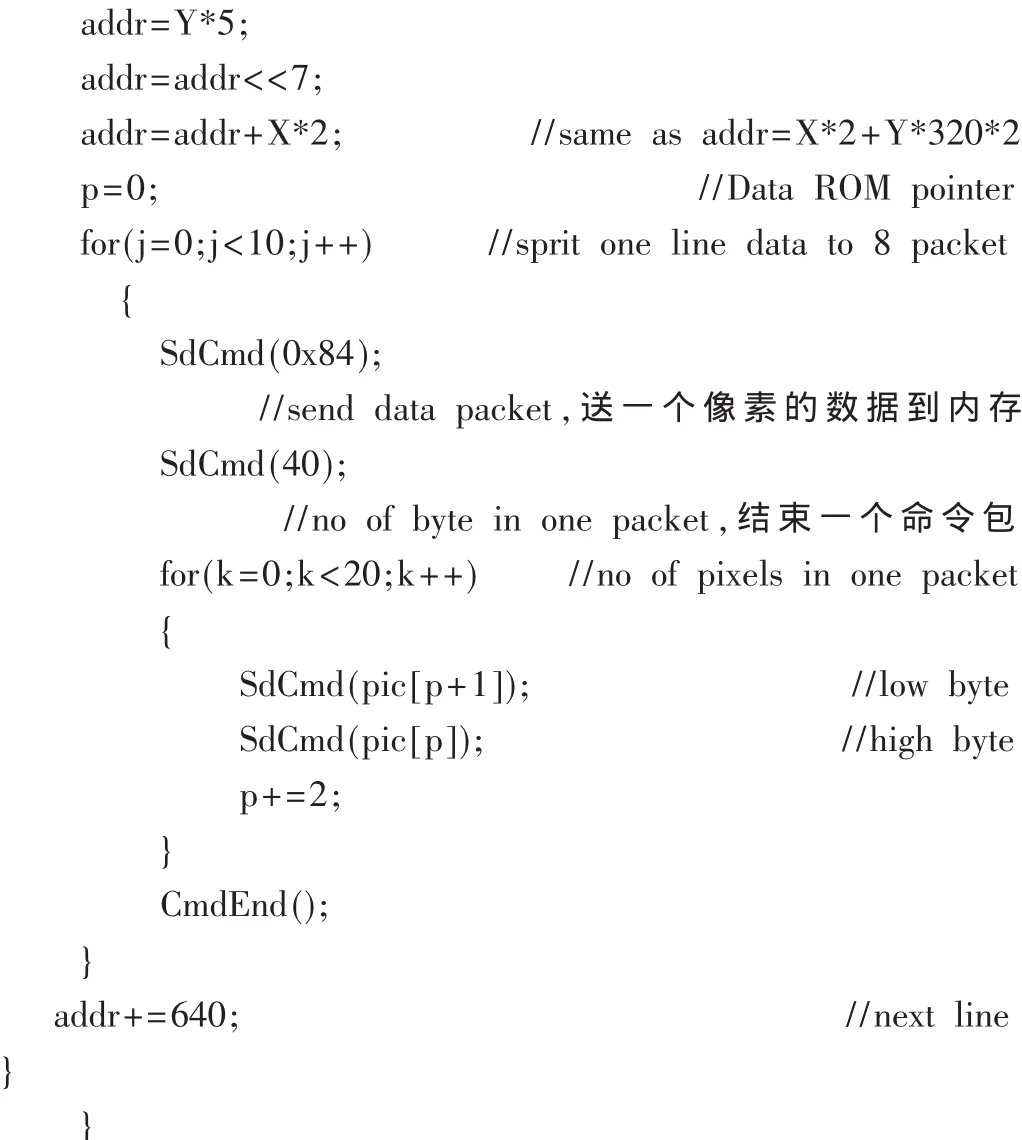

代码如下:

在控制时序的基础上,程序中的显示图片部分[7]首先把要显示的图片用Bmp2HexPro.exe软件工具转换成数据信息,把图片的数据信息以头文件的形式(picture.h)添加在工程中。

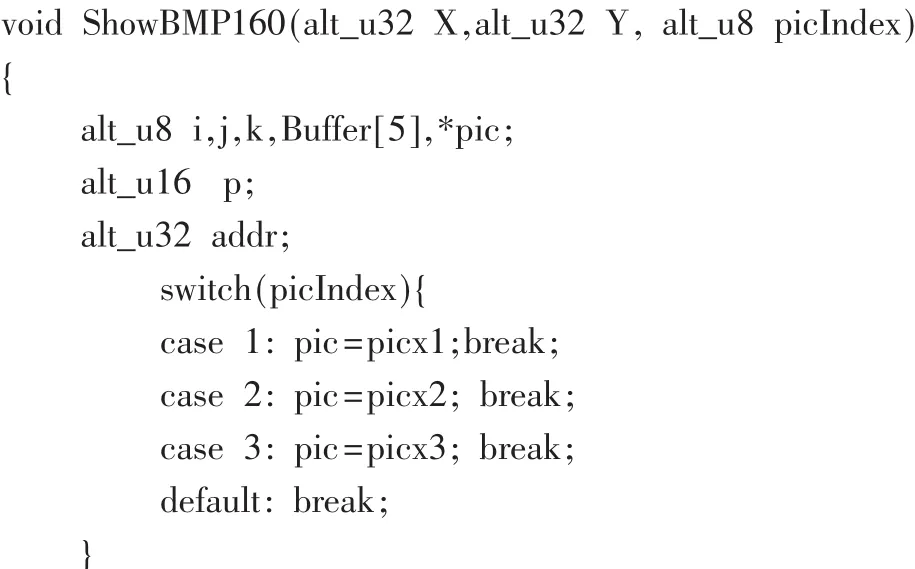

对储存的多张图片进行分类标号(例如picx1、picx2、picx3等),然后在 C主程序中用 switch语句[8]来分别调用表示该图片信息的索引号码,示例程序如下:

接下来就是给LCD的RAM分配地址,把要显示的图片的数据信息以数据指针的方式从左到右依次写入目的地址。而SdCmd()函数为自己编写的发送数据命令的子函数。

对于汉字以及字符的显示也是通过定义PrintGB()函数,类似上述程序以命令包的形式把要显示的信息送入目的地址,在后面的程序中直接调用该子函数来进行显示。

随着LCD显示越来越多地应用于生产生活的各个方面,各种各样的处理器控制LCD显示的方案也相继出现,本文通过整个系统设计和在硬件平台上实验提出了一种基于FPGA的SoPC方案,并最终在平台上面验证了其可行性。该方案的优势在于系统功能改进的灵活性,在不改变硬件平台的情况下对系统进行增删和优化,降低了系统成本,这是传统ARM方案无法达到的。由于微处理器和用户逻辑接口都集成在一块Cyclone芯片上,编程人员可以灵活地定义I/O接口,基于FPGA有更好的灵活性和可靠性[9]。对基于NiosⅡ的微处理器,用户能根据显示屏的大小灵活调整硬件逻辑设计以实现对显示屏的控制,而不需要改变其原有硬件构成。但是16位微控制器却只能对固定大小的显示屏进行控制。从长远来看,基于NiosⅡ的微处理器,可以通过更改其硬件逻辑配置方便地进行版本升级,节省了成本。开发人员通过处理器[10]指令集中增加定制指令,可以加速软件算法,定制指令可以在一个周期的时间内完成复杂的处理任务,为系统优化提供了一种高性价比的解决方案。

[1]潘松,黄继业,曾毓.SoPC技术实用教程[M].北京:清华大学出版社,2005.

[2]王刚,张潋.基于FPGA的SoPC嵌入式系统设计与典型实例[M].北京:电子工业出版社,2009.

[3]王晓迪,张景秀.SoPC系统设计与实践[M].北京:北京航空航天大学出版社,2008.

[4]蔡伟刚.NiosⅡ软件架构解析[M].西安:西安电子科技大学出版社,2007.

[5]田秀伟,郑喜凤,丁铁夫.基于 SoPC的 LED显示屏控制器设计[J].液晶与显示,2007,22(6):737-741.

[6]孙恺,程世恒.NiosⅡ系统开发设计与应用实例[M].北京:北京航空航天大学出版社,2007.

[7]郭强.液晶显示应用技术[M].北京:电子工业出版社,2003.

[8]郭书军,王玉龙,葛纫秋.嵌入式处理器原理及应用—Nios系统设计和C语言编程[M].北京:清华大学出版社,2004.

[9]孙伟,龚兆岗,杨忠根.基于 NiosⅡ的 LED显示屏控制系统[J].上海海事大学学报,2005,26(2).

[10]高兵,陈莉平.液晶和矩阵键盘SoPC外设组件设计开发[J].微计算机信息,2008,3(2):152-154.