基于AD7655的鱼雷声靶数据采集系统设计分析*

2010-04-26王楠

王 楠

(海军驻昆明750试验场军事代表室 昆明 650051)

1 引言

鱼雷声靶是一种用于鱼雷水下声纳试验的声学靶标。它利用数据采集系统接收水中的声信号,并从中检测鱼雷声纳“寻的”信号的有无,然后将接收到的“寻的”信号经过目标强度设置、多普勒频移设置、辐射噪声设置等处理后将回波信号转发出去,鱼雷检测到声靶回波信号后,根据鱼雷对信号的检测结果来判断鱼雷对水声目标的检测能力。根据分析水声信号的特点及鱼雷声靶的技术要求[1],声靶数据采集系统需要满足以下参数的指标要求:A/D转换器具有4路输入模拟信号同步采样的能力,每路采样通道具有16bit的采样精度,每个采样通道的采样速率最高可达200kSPS,接收换能器的输出电压信号幅值±10V。根据以上对数据采集系统的要求,由于AD7655[2,4]的转换速度可达1MSPS;当4个通道同时采集时,每个通道最高的采样频率可达250kSPS;转换精度可达16bit;支持串、并行数据输出方式;能够满足数据采集系统对AD芯片的要求,且单芯片就能完成多路模数转换功能,组成的数据采集系统简单可靠,所以,选择AD7655作为数据采集系统的模数转换芯片。

本文在分析数据采集系统的总体构成的基础上,详细介绍了前置调理电路、模数转换单元和DSP数据接收模块等组成部分的主要功能和设计原理[5~6],最后给出了系统设计合理性的结论。

2 系统总体构成

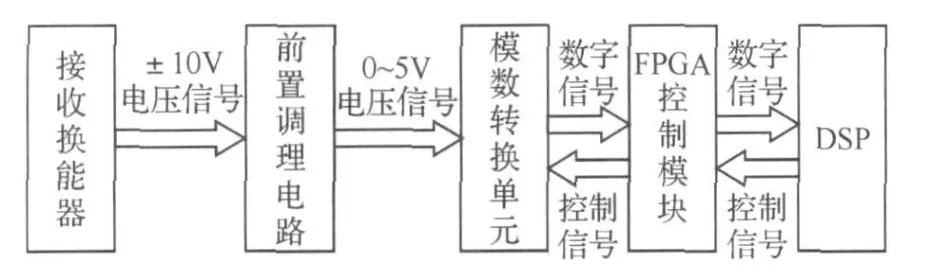

根据数据采集系统的功能要求和数据处理流程,该系统可由接收换能器、前置调理电路、模数转换单元、FPGA控制模块和DSP数据接收模块组成,如图1所示。

图1 数据采集系统结构图

◦接收换能器:声靶系统中的外部信号都是以声波的形式到达接收换能器,需要首先将声信号转化为对应量级的电信号,声纳信号通过接收换能器后转化为连续的电压波形信号。

◦前置调理电路:对于A/D转换器件而言,其对模拟信号输入的幅值有特别的要求,所以需要对接收换能器的输出信号进行调理,使之满足A/D转换器对输入信号的要求。

◦模数转换单元:对经过调理后的模拟信号进行采样,得到对应的数字量信号,供系统对这些数字信息进行进一步处理。

◦FPGA控制模块:由于AD7655正常工作需要较复杂的一些控制信号,AD7655将转换后的数字信号传送到DSP的过程也有严格的时序要求,所以,运用FPGA强大的可编程能力,可以方便的完成上述控制要求。

◦DSP数据接收单元:实时接收AD7655传送来的数字信号,DSP的数据接口要有足够的数据吞吐率,本系统选择ADSP21060作为声靶系统的数字处理器,因为它有多种与外部器件传送数据的接口方式,可以根据实际需要灵活选择。

3 系统设计

AD7655可以有多种工作方式:根据数据输出方式的不同可分为串行数据输出方式与并行数据输出方式;根据工作时钟是否由外部提供可分为主模式与从模式。ADSP21060与外部器件之间数据传输接口也有多种方式,如主机接口方式、串口方式、外部DMA方式等。因为通过串口传送数据可以充分利用DSP的串口资源,避免在其它方式下占用DSP的外部数据总线与地址总线,所以本系统中设置AD7655工作在串行从模式下,利用ADSP21060的串口实现AD7655与ADSP21060的数据传送,用于输出的数据线大幅减少,从而简化了系统的硬件结构。从模式下AD7655工作时钟由外部提供,通过FPGA产生的控制信号,可以方便的实现传送数据的同步。在介绍数据采集系统的设计之前,先对涉及到的AD7655的管脚做出简要说明[2~3]:

1)SER/(/PAR):(数字输入)串行/并行模式选择。为低时,选择并行数据输出模式;为高时,选择串行数据输出模式。

2)D[4]/[EXT/(/INT)]:在串行模式下(数字输入),作为时钟来源的选择信号。该引脚位低时,内部时钟信号将出现在SCLK引脚上;当该引脚被设置成逻辑高时,数据的输出与SCLK引脚上的时钟信号同步,而该时钟信号由外部提供。

3)A/(/B):(数字输入)数据通道选择。在串行模式下,为高时,通道A的数据先被读出,然后再读通道B的数据;为低时,通道B的数据先被读出,然后再读通道A的数据。

4)A0x:(数字输入)多路(复用)器选择,当为低时,INA1和INB1通道同时采样并转换;为高时,INA2和INB2通道同时采样并转换。

5)/RD:读数据。当片选信号/CS和/RD都为低时,接口总线使能。

6)/CS:芯片选择。/CS也用于打开外部串行接口。

7)INB1,INB2:模拟输入通道B。

8)INA1,INA2:模拟输入通道A。

9)D[9]/SCLK:在串行模式下,作为时钟输入信号。

10)BUSY:(数字输出)当转换开始的时候置高该引脚,并且一直保持为高,直到两个通道的转换完成和数据锁存到片上移位寄存器内。BUSY信号的下降沿用作数据准备好信号。

11)/CNVST:(数字输入)开始转换。该信号的下降沿使内部的采样/保持进入保持状态并开始转换。

12)D[8]/SDOUT:在串行模式下,作为串行数据的输出引脚(与SCLK信号同步)。转换结果存储在内部的一32位寄存器内,AD7655同时提供两个转换结果,最高位在前。

3.1 前置调理电路设计

因为接收换能器的输出电压幅值为±10V,而AD7655的模拟电压输入范围为单极性的0~5V,所以,需要对每路的AD信号输入进行极性和幅值的调整,其调理电路设计如图2所示。

图2 前端调理电路图

图2中,由两个集成运算放大器配合电阻电容,组成了一个两级的信号调理电路。通过配置合适的电阻值,第一级运放将信号进行1/4倍的增益放大后,输出信号的幅值变为±2.5V;而第二级则在第一级输出值的基础上,添加一个2.5V的偏置,所以对应于±10V的外部电压信号输入,经过调理后的输出电压范围为0~5V,满足了AD7655对输入电压的要求。

3.2 模数转换单元

FPGA控制模块所需的信号输入格式为数字信号,而前端调理电路输出地信号格式仍然为模拟信号,所以需要利用AD7655把经过调理的电压信号转换为数字信号,AD7655工作在串行从模式下的控制管脚状态与工作时序如图3所示。

图3 AD7655串行从模式工作时序图

经过复位信号对芯片复位后,向芯片输入转换信号CNVST,下降沿启动芯片的采样保持器。BUSY下降沿指示转换完毕。通过SCLK引脚向AD芯片输入串行时钟,读取串行数据SDOUT。SDOUT一次输出32位数据,前16位为A1通道数据,高位在前。后16位为B1通道数据,高位在前。在CNVST为高电平时可以对A0X信号置反,在下一次采集时换成另外两个通道采集数据。

在本系统中,AD7655的控制时序由FPGA产生,设置好AD7655工作状态后,通过FPGA控制A0x输入频率为200KHz,CNVST输入频率为400KHz,FPGA中用40M时钟采样BUSY信号的下降沿,检测到后向AD输入33个40M的串行时钟信号。该信号以上升沿开始,在第二个上升沿读取第1bit数据,并作串并转换。在第17和第33个下降沿锁存串并转换结果,获得两路16位采样数据。当A0x状态改变后,通过同样过程得到另外两路的16位数字信号,则AD7655数据输出流量为:

3.3 DSP数据接收单元

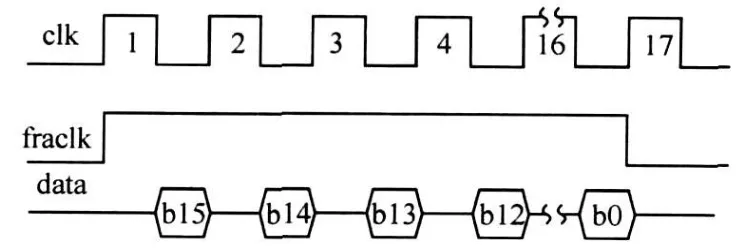

利用ADSP21060串口接收AD7655转换后的数字信号,ADSP21060的串口接收数据时序图如图4所示,控制时序由FPGA产生。

图4 ADSP21060串口接收时序图

clk为串口接收时钟信号,fra clk为串口帧同步信号,data为串口接收数据信号。串口接收数据过程为:向ADSP21060串口的接收时钟管脚输入时钟信号,启动帧同步信号,在帧信号有效过程中,在串口时钟下降沿对数据进行采样,接收采样数据。

在本系统中,串口时钟 clk输入频率为20MHz,帧同步信号为800KH,则串口的数据吞吐率为:

能够满足AD7655的数据输出流量,AD采样数据能够正常传送到DSP而不存在瓶颈。

4 结语

随着鱼雷武器的不断发展和研制试验力度的不断加大,鱼雷声靶在降低试验费用、提高试验效率等方面功不可没。数据采集系统作为鱼雷声靶的核心部件,其性能对鱼雷声靶具有决定性的影响。本文介绍的以 AD7655芯片为主要组件的数据采集系统不仅在硬件设计中简单易行,而且在实际的应用过程中,工作稳定性、试验精度和可靠性都比较高,满足了声靶对数据采集系统的需要。

[1]李飞,李斌.水声定位系统数据彩集单元设计[J].声学技术,2009,28(5)

[2]Analog Devices.Inc.AD7655 Datasheet[M].2004

[3]王庆利,刘奎,袁建敏.单片机设计标准教程[M].北京:北京邮电大学出版社,2008

[4]王芳,严胜刚,陈勇.基于CPLD的多路数据采集系统[J].弹箭与制导学报,2005,25(4)

[5]刘东亮,焦彦军,张新国.基于DSP和嵌入式系统的便携式数据采集分析装置设计[J].电力自动化设备,2007,27(8)

[6]杨胜,房建成.基于DSP和POS数据采集与处理系统的设计与实现[J].仪器仪表学报,2008,29(9)