基于USB的GPS数据采集系统

2010-03-21张建喜李金海阎跃鹏

张建喜,汪 峰,李金海,阎跃鹏

(中国科学院 微电子研究所,北京 100029)

1 引 言

在GPS高动态接收机研制中,要对捕获、跟踪及定位等算法进行仿真及验证,优化算法性能。为得到算法仿真及测试所需的真实数据,需要数据采集系统对GPS信号进行实时采集。目前比较通用的数据采集系统只支持采集信号的实时流盘或暂存在FLASH中的单一模式。本文设计了一套既可实现数据实时传输又可在特殊环境下将数据暂存到FLASH中的GPS数据采集系统。

外设与主机的通信接口一般基于PCI总线、RS-232串行总线或通用串行总线(Universal Serial Bus,USB)。PCI总线虽具有较高的传输速率,支持“即插即用”,但存在插拔麻烦、扩展槽有限的缺点。RS-232串行总线虽连接简单,但是传输速度慢,且主机串口数目有限。USB具有速率高、易扩展、安装方便等特点,已成为主流的数据传输总线。本文所设计的采集系统基于USB,有效地克服了其它总线的缺点。

2 采集系统硬件结构

GPS数据采集硬件系统主要包括GPS射频前端、FPGA控制模块、USB数据传输单元(CY7C68013)、FLASH 存储模块及EEPROM,系统结构示意图如图1所示。

GPS信号经天线接收送至射频前端,在射频芯片中经ADC将模拟中频信号转化为数字中频信号送入FPGA中,FPGA对数字信号进行实时处理并缓存到RAM中,在采集系统与主机连接的情况下将数据批量地发送到CY7C68013的FIFO中,通过FIFO将数据送至主机,主机对数据进行实时流盘,完成对GPS信号的采集。在一些特殊环境下,采集系统与主机无法连接,此时,需将RAM中的数据暂时存储到FLASH中,以后再从FLASH中读出数据,完成特殊环境下的信号采集。

2.1 GPS射频前端

GPS射频前端采用SiGe半导体公司的SE4110L芯片,该芯片具有集成度高、功耗低、性能高等优点,广泛应用于GPS接收机中。SE4110L包括带通滤波器,低噪声放大器,自动增益控制器,模数转换器(ADC)等[1]。L1频段(1575.42GHz)的GPS信号下变频到模拟中频经ADC后进行2 bit量化变成数字中频信号,采样频率为16.368MHz,每个采样点包括符号位Sign和幅度位Mag。采集系统的工作时钟也为16.368MHz,每4个采样点拼接成一个字节,则系统实时传输速率达4 Mbit/s。

2.2 FPGA控制模块

FPGA作为系统的控制核心,分别与射频前端、CY7C68013及NAND FLASH接口,产生CY7C68013及NAND FLASH所需的控制信号,完成对信号的采集、数据缓存/传输、CY7C68013读/写控制、NAND FLASH块状态信息管理及FLASH读写等功能。

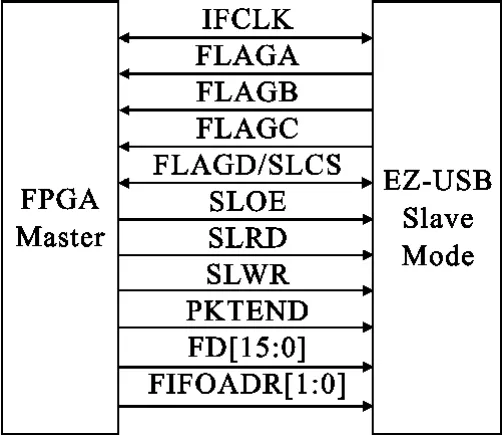

2.2.1 FPGA与 CY7C68013、NAND FLASH的接口设计

FPGA作为主端控制从端CY7C68013芯片,接口管脚连接如图2所示。其中,IFCLK为CY7C68013同步模式下接口时钟;FLAGA 、FLAGB、FLAGC、FLAGD为FIFO的工作状态标志位。在FPGA可控的输入信号中,SLCS为片选信号;SLOE为输入使能信号;SLRD为读使能信号;SLWR为写使能信号;PKTEND为数据包结束信号,当发送比FIFO小的数据包时,FPGA可通过发送PKTEND信号完成;FIFOADR[1:0]为端点缓冲区选择信号,00选择端点EP2,01选择端点EP4,10选择端点EP6,11选择端点EP8;FD[15:0]为FPGA与FIFO之间的数据总线,数据宽度为16位。

图2 FPGA与CY7C68013之间的接口Fig.2 Interface between FPGA and CY7C68013

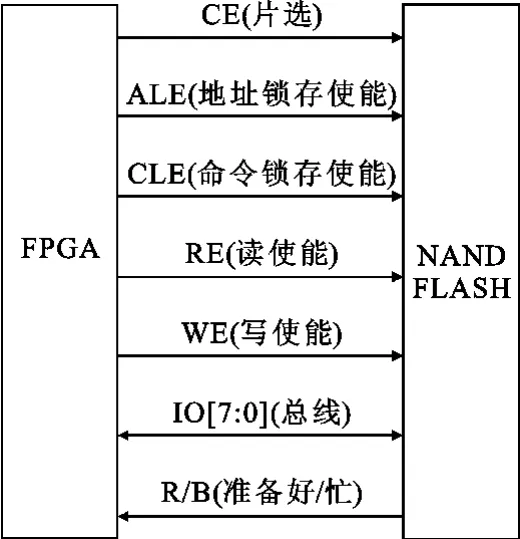

NAND FLASH与其它存储器不同,没有指定的地址总线和命令总线,只有通用的总线,通过命令锁存使能和地址锁存使能,将命令和地址写入命令寄存器和地址寄存器,来完成FLASH的读、写及擦除等各项操作。接口设计如图3所示。

图3 FPGA与FLASH之间的接口Fig.3 Interface between FPGA and FLASH

2.2.2 双缓冲

在采集系统中,普遍存在丢失数据(以下简称丢数)现象。由于该系统采样率和数据传输速率非常高,就会导致USB主机没有及时响应而发生丢数现象,严重影响系统的可靠性。为了解决上述问题,采用双缓冲技术。在FPGA内开辟大块RAM,分成大小相等的两部分,进行乒乓操作,使读出RAM的频率为写入RAM频率的2倍,这样可以在数据量不变的前提下增加数据包之间的时间间隔,为USB主机预留出更多的响应时间。

2.3 USB传输单元

在USB传输单元中采用Cypress公司 EZ-USB FX2LP系列中的CY7C68013芯片。EZ-USB FX2LP系列芯片集成8051内核及串行接口引擎(SIE),SIE能够完成数据解码、位填充、差错控制等与USB协议相关的工作,减轻增强型8051的负担,降低了USB固件程序的开发难度[2]。

该系统中选择CY7C68013的从FIFO(Slave FIFO)工作模式,如图4所示。在这种工作模式下,外围控制电路可像对普通FIFO一样对CY7C68013的端点缓冲区进行读写,而不需要8051内核参与,极大提高了传输速度。在USB协议中端点为数据的接收器和发送器。CY7C68013中的EP0是唯一的控制端点,大小为64 byte,所有的控制命令通过EP0传输。EP2、EP4、EP6、EP8为数据传输端点,其中EP2和EP6最大为1024 byte,EP4和EP8最大为512 byte。

图4 Slave FIFO工作模式Fig.4 Slave FIFO mode

CY7C68013集成I2C总线协议,可外接EEPROM等片外存储器件。芯片上电时,如果检测到I2C总线上连接EEPROM,且其首字节为0xC2,则EEPROM提供USB设备描述符及USB固件程序。EEPROM具有掉电时内部数据不丢失的优点,这样,系统在上电时可以自动加载固件程序到片内RAM。

2.4 FLASH存储模块

在采集系统无法与USB主机连接的情况下,采集到的GPS信号要暂存在FLASH中。NAND型FLASH具有容量大、改写速度快及数据非易失性的特点,在业界得到了广泛应用。本系统中的NAND FLASH采用Samsung公司的K9K8G08U0A,存储单元为(1G+32M)×8 bit,共由8192个 block 组成,每个block包含64个page,每个page含有2 k+64个字节,其中2 kbyte为数据存储区,用来存储用户数据;剩余64 byte为辅助存储区,用来保存坏块标志位、ECC码等状态信息。

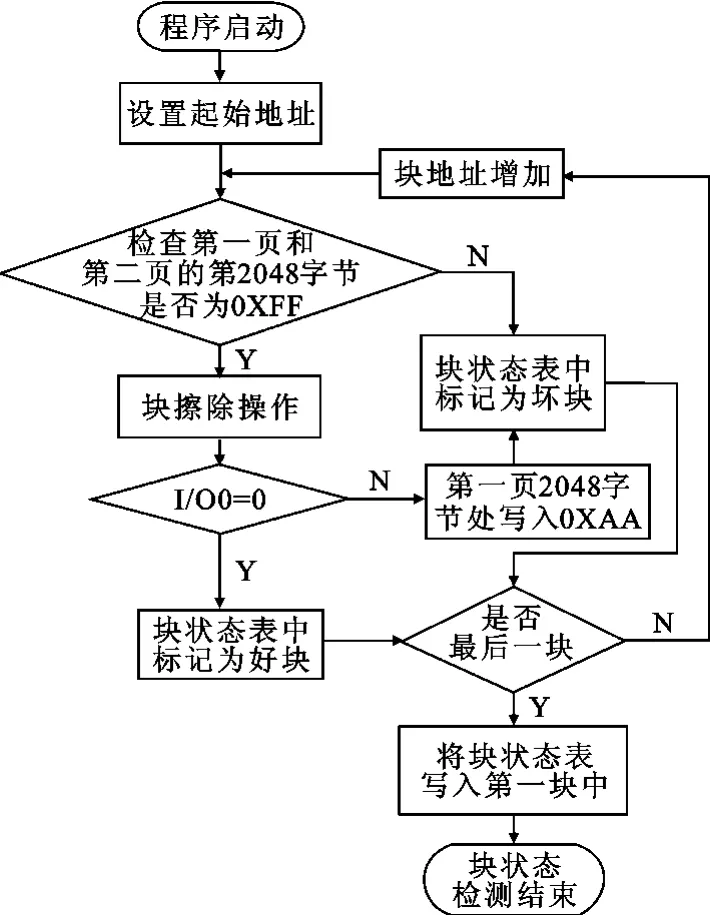

NAND型FLASH芯片在出厂时会存在一块或多块坏块以及在使用过程中也会出现坏块,这在NAND结构的FLASH中无法避免。因为FLASH中的每个block相互隔离,坏块的存在不影响对其它块的操作。但是,坏块会导致数据丢失及误读,影响采集数据的有效性和完整性。因此,在进行数据读写及擦除操作前需要将坏块剔除,防止数据的丢失,保证系统的可靠性。在FPGA中建立块状态表,将FLASH中的每个block的状态加以标记,整个流程如图5所示。FLASH芯片在出厂时会对坏块进行标记,每一块的第一页和第二页的第2048 byte为非0XFF表示块无效,0XFF表示块有效[3]。这些块信息在读取之前可能被误擦除,因此在进行坏块检测时,首先判断当前块是否有效,若为无效块则直接在块状态表中标记为坏块;若为有效块则进行擦除,读取状态寄存器IO第0位是否为0,如果为0在块状态表中标志为有效块,否则标记为坏块,同时在第一页的第2048 byte写入0XAA,其时序图如图6所示。对FLASH中的每块状态标记完后,将块状态表写入FLASH的第一块中。

图5 块状态表建立流程图Fig.5 Flowchart of the foundation of block state table

图6 坏块标记时序图Fig.6 Timing diagram of the marking of invalid block

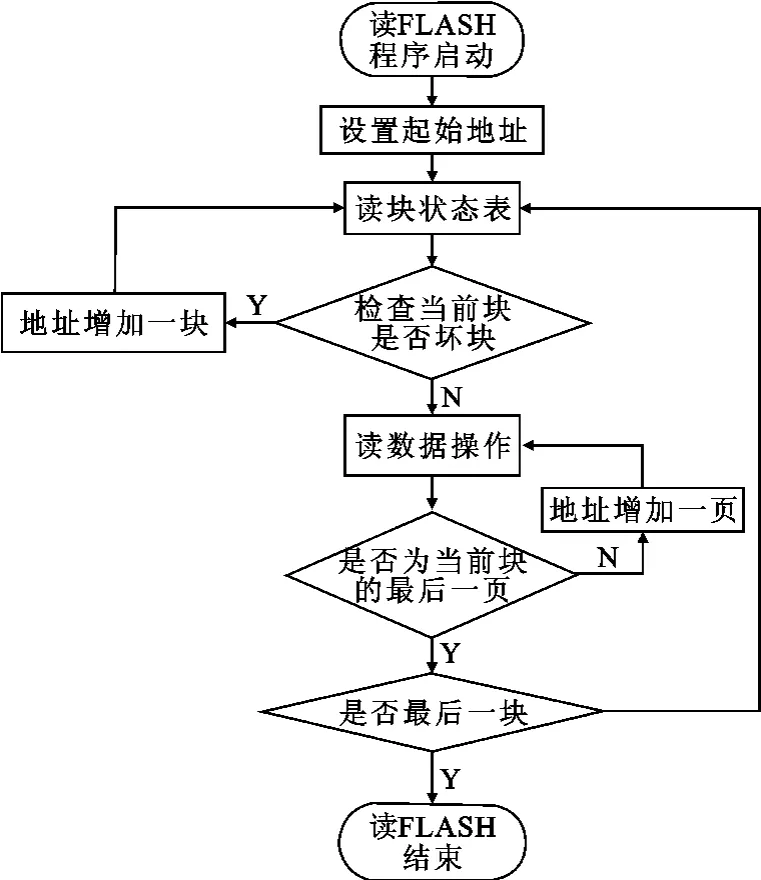

FLASH是按块擦除,按页读写。在FPGA中用Verilog语言设计状态机完成对FLASH的操作。对每一块Block操作之前需要根据块状态表判断当前块是否有效,如果为坏块,则把当前块跳跃过去;如果为有效块,则按页进行读写操作,以读数据流程为例,如图7所示。块状态表有效地防止了对坏块的操作,保证数据的完整不丢失。

图7 读取数据流程图Fig.7 Flowchart of read data

3 采集系统的软件设计

采集系统的软件设计包括USB固件程序和USB主机控制软件。CY7C68013芯片根据USB固件程序响应USB请求、中断处理、端点选择及数据读写。CYPRESS公司为USB主机提供了通用控制函数库CyAPI.lib,主机调用库中接口函数便可完成与采集系统之间的数据传输。同时,CYPRESS公司还为USB芯片提供通用的驱动程序CYUSB.SYS,可以直接驱动USB芯片。

3.1 USB固件程序

CYPRESS公司的开发包提供基本的USB固件程序开发包框架,其中头文件介绍如下:fx2.h为头文件定义EZ-USB的通用常量、宏、数据类型和库函数;fx2regs.h定义EZ-USB的寄存器声明和位标志;EZUSB.lib为EZ-USB的库文件,提供和外部芯片的控制封装;dscr.a51为汇编文件定义USB设备的各种描述符;syncdly.h为同步延时的宏定义,用于需要同步延时的寄存器。

开发包中的fw.c为USB固件程序的主文件,包括main函数、任务调度、SETUP命令处理等。periph.c完成USB的初始化和任务处理函数:开发者在TD-Init函数里对CY7C68013芯片的寄存器进行配置,完成芯片的初始化;开发者可添加任务函数,如产生采集系统启动和停止等控制信号[4]。

本系统中启用EP6为数据接收端点,配置大小为1024 byte,传输模式为异步全自动模式。USB固件程序经I2C总线存储到EEPROM中,系统上电后自动加载到片内RAM。

3.2 USB主机控制软件

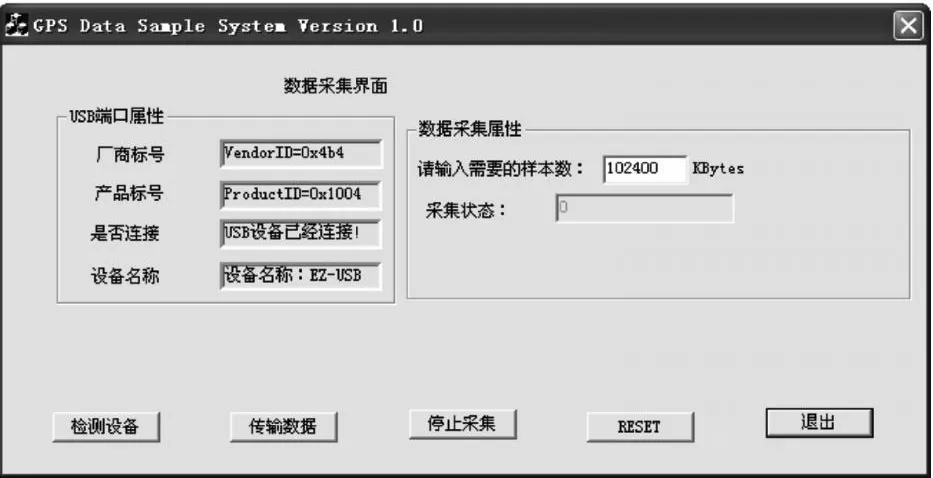

USB主机控制软件是采用MFC设计的一种应用程序,主要完成上位机对USB设备的检测、系统启动、数据传输、停止采集及系统复位等操作。EZ-USB FX2LP系列芯片的CyAPI控制类函数定义了详尽的控制接口。MFC利用类的方法把API函数根据用途进行分类封装,通过分类管理实现对同类函数的调用,从而实现采集系统的控制和通信。主机控制软件界面如图8所示。

图8 主机控制软件界面Fig.8 Interface of host control software

采集系统经USB传输线连接到主机后,主机控制软件检测USB设备是否连接,并读取设备描述符如厂商标号、产品标号及设备名称。检测完设备后,输入所需的样本数,启动数据传输。主机发送启动采集命令到USB设备,设备响应命令,将CY7C68013芯片IO管脚PA0电平置低,FPGA检测该管脚为低时,启动采集。将采集到的数据经USB总线写入主机硬盘,实现对数据的实时采集与流盘。当采集完成时,主机程序提示采集已完成。同样,主机发送停止采集命令到USB设备,将PA0电平置高,FPGA检测到该电平时进入空闲状态,即停止采集。

4 采集数据的仿真验证

GPS信号是由直接序列扩频码对载频进行二相调制的CDMA信号[5]。直接序列扩频码包括粗/截获码(C/A码)和精密码(P码),SPS用户使用C/A码。GPS系统在轨卫星32颗,每颗卫星有各自专门的扩频码。为从GPS信号中解调出卫星导航电文,必须得到C/A码的码相位和载波多普勒频移这两个重要参数[6]。采集到的数据通常含有多颗卫星信号,每颗卫星的C/A码相位和载波多普勒频率各不相同。捕获过程即是找到每颗卫星的C/A码相位和载波多普勒频率。图9所示为采集数据中3号GPS卫星捕获结果。跟踪过程根据捕获到的C/A码相位和载波多普勒频率实现本地信号与输入信号的精确同步,如图10所示,码相位与载波相位已经锁定,I路输出为导航数据,Q路输出只包含噪声。

图9 捕获结果Fig.9 Result of acquisition

图10 导航数据Fig.10 Navigation data

5 结束语

本文设计的GPS数据采集系统可实现采集数据的实时流盘,也可作为非实时传输系统将采集数据暂存在FLASH中。采用双缓冲技术,有效地解决了采集系统中数据丢失的问题。该系统基于USB总线,具有较高的传输速率,系统工作稳定,便于维护和升级,广泛应用于采集GPS中频信号,在GPS接收机开发、产品化过程中发挥了重要的作用。

[1] 杨秋波.基于SE4100L设计GPS接收机射频前端电路[J].电子技术,2007(z3):115-116.YANG Qiu-bo.The Design of Radio Frequency Front Circuit of GPS Receiver Based on SE4100L[J].Electronic Technology,2007(z3):115-116.(in Chinese)

[2] 倪明辉,周军,杨庚.USB在FPGA控制的高速数据采集系统中的应用[J].计算机测量与控制,2006,14(2):268-271.NI Ming-hui,ZHOU Jun,YANG Geng.Application of USB in High Speed Data Acquisiton System Controlled by FP GA[J].Computer Measurement&Control,2006,14(2):268-271.(inChinese)

[3] 秦丽,何慧珠,张会新.基于USB2.0的通用FLASH存储器检测系统设计[J].电测与仪表,2008,45(4):61-64.QIN Li,HE Hui-zhu,ZHANG Hui-xin.Design of universal check and measure system for flash based on USB2.0[J].Electrical Measurement&Instrumentation,2008,45(4):61-64.(in Chinese)

[4] 徐夏,雷明.基于CY7C68013的数据通信系统设计[J].微计算机信息,2009,25(17):198-200.XU Xia,LEI Ming.Design of data communication system based on CY7C68013[J].Microcomputer Information,2009,25(17):198-200.(in Chinese)

[5] Elliott D Kaplan.GPS原理与应用[M].邱致和,王万义,等,译.北京:电子工业出版社,2002:52-59.Elliott D Kaplan.Understanding GPS Principles and Applcation[M].Translated by QIU Zhi-he,WANG Wan-yi,et al.Beijing:Publishing House of Electronics Industry,2002:52-59.(in Chinese)

[6] James Bao-Yen Tsui.GPS软件接收机基础[M].陈军,潘高峰,等,译.北京:电子工业出版社,2007:108-153.James Bao-Yen Tsui.Fundamentals of Global Positioning System Receivers A Software Approach[M].Translated by CHEN Jun,PAN Gao-feng,et al.Beijing:Publishing House of Electronics Industry,2007:108-153.(in Chinese)