一种增益增强型套筒式运算放大器的设计*

2010-03-14蔡坤明何杞鑫陶吉利丁扣宝

蔡坤明 ,何杞鑫 ,陶吉利 ,丁扣宝

(1.浙江大学 宁波理工学院,浙江 宁波315211;2.浙江大学 微电子与光电子研究所,浙江 杭州310027)

随着数字信号处理技术的不断发展,信号处理系统对模数转换器(ADC)提出了更高的要求:需要能够处理更高频率、达到更高精度的ADC。运算放大器作为高速高精度ADC中的重要部分,其性能好坏直接决定整个系统性能的高低。然而在电源电压和沟道长度不断减少的趋势下,高性能运放的设计成了一项越来越具挑战性的工作。国内外对运放的研究与设计从来没有停止,研究领域主要集中在运放的高增益、高带宽、宽摆幅、低功耗等高性能的实现上[1]。国外起步早,技术先进,研究已经进入比较成熟的阶段[2]。而国内的研究还存在着较大的差距。

本文针对 12 bit精度,100 MS/s Pipelined ADC的要求,设计了一个能够应用于其中的高性能运算放大器,仿真结果表明,运算放大器能满足系统要求。

1 电路结构与设计

CMOS运算放大器的实现结构主要有3种[3]:两级运放(Two-stage OTA)、折叠共源共栅运放(Fold-cascade OTA)和套筒式运放(Telescopic OTA)。两级运放的增益很大,差分输出摆幅也大,但它的高阶极点造成了有限的稳定带宽,需要进行米勒补偿,这增加了电路设计的复杂性;折叠共源共栅运放的频率特性好、输出摆幅大,但支路较多、功耗较大。相比之下,套筒式运放的输出摆幅与折叠共源共栅运放差不多,频率特性好,功耗相对较低,本文采用这种结构。

1.1 增益增强技术

单级的CMOS运放很难达到高增益,多级运放在频域方面又需要额外处理。这个矛盾激励着人们探索新的电路结构来实现高增益和高带宽运放的要求。一种称为“增益增强”的技术[4]应运而生,如图1所示。其基本原理是:在小信号分析中,M1相当于一个反馈电阻,其两端的小信号电压正比于输出电流。M2构成一个从电流到电压的负反馈环路,通过运放的反馈,调节了M2管的源极电压,使其趋近于Vref。通过反馈使得M1的漏极电压随输出电压的变化很小,流过M1的电流更加恒定,因而产生了更高的输出阻抗。电路产生的输出阻抗为[5]:

其中,r01、r02分别是 M1、M2管的小信号等效电阻,gm2是M2的跨导。未加反馈时,输出电阻值为gm2r01r02。可见,利用增益增强技术可以使输出电阻提高A倍,从而也使得增益增大了A倍。

增益增强技术在提高增益的同时也带来了一个缺点。在图1电路中存在着2个极点,一个在输出端,另一个在M2的源端,前者是运放的主极点,而后者是运放的次主极点。在这个电路中,经常会产生极零点对,尽管极零点对不会影响运放的频率响应,但它却使运放的建立特性变差。为解决这个问题,通常辅助运放A的单位增益频率要介于闭环-3dB频率和主运放的非主极点之间[6]。

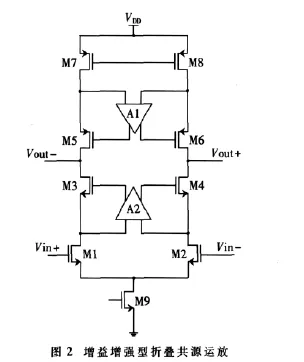

1.2 运放的设计

利用增益增强技术设计的增益增强型套筒式运算放大器如图2所示。电路由3部分构成:主运放、辅助运放、共模反馈电路[7]。主运放是套筒式架构,可以达到很高的带宽;辅助运放不需要有大的摆幅,采用折叠共源共栅架构;共模反馈电路用来稳定电路的输出,由开关电容共模反馈电路和连续时间共模反馈电路组成,在图2中省略。

1.2.1 设计参数

不同的电路系统,对运算放大器的要求不同。本节将从 12 bit、100 MS/s的 Pipelined ADC对运放的要求出发确定高性能运放的参数指标。

运放有限的直流增益将造成系统建立的误差。

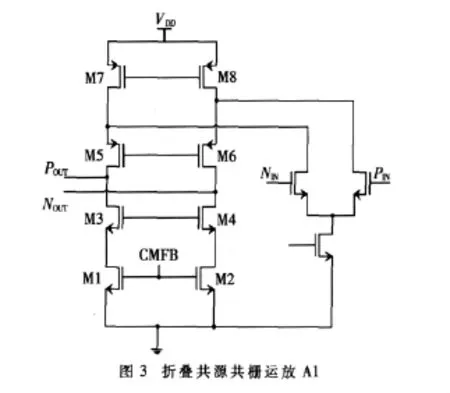

对于精度为12 bit的ADC来说,要求运放的建立误差Verror必须小于LSB/2。其中:

由式(2)、(3)可得,A>8 192,即 78.26 dB。

运放有限的建立时间也将造成系统建立的误差。对于采样频率为100 MHz的ADC,要求运放在半个时钟周期内(t=5 ns)建立到所需要的精度。在简单的单极点阶跃响应中,运放的输出为:

其中:Videal是运放理想的输出。建立误差应该小于LSB/2,所以有:

根据式(5)可以求得运放的单位增益带宽应大于358 MHz。若综合考虑时钟馈通、电荷注入、工艺误差等非理想因素,应适当放宽对指标的要求[8]。因此本文的设计目标是增益大于90 dB,带宽大于500 MHz。

1.2.2 运放的设计

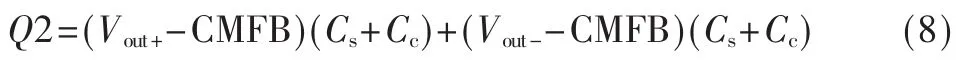

如图2所示,为了达到高增益和高带宽,运放的设计主要包括主运放的设计和辅助运放 A1、A2的设计[9]。主运放采用套筒式架构,辅助运放则采用折叠式共源共栅架构。电路的增益表达式可以表示为:

其中,Rout=A1gm5r05r07||A2gm3r01r03。

由式(6)可知,提高输入管的跨导或提高辅助运放的增益都能达到提高增益的目的。

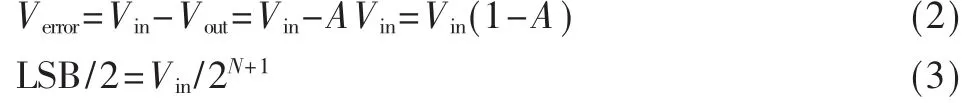

在相同的宽长比下,NMOS管的跨导值比PMOS管大,所以选择NMOS管作为主运放的输入管。电路的主极点存在输出端,临近输出端的2个MOS管的宽长比要合理选择,既要满足一定的电流要求,又不能引入太大的寄生电容而使频率特性变差。2个辅助运放A1、A2是全差分的折叠共源共栅结构[10]。以A1为例,NMOS输入管接M7、M8的漏极,经过放大后输出到 M5和 M6的栅极,A1只需提供 M5、M6饱和工作所需的共模电平,因而不需要大的摆幅。同时由于M5和M6的栅极电容构成A1的容性负载,所以2个管子不能太大。辅助运放A1如图3所示。A2的拓扑结构和A1类似,但采用PMOS管作为输入管。

1.2.3 共模反馈电路的设计

运算放大器的设计通常采用全差分结构,因为它对共模扰动有很好的抑制作用。但在高增益的放大器中,输出共模电平对器件的特性和失配相当敏感,而且不能通过差动反馈达到稳定,必须增加共模反馈网络来调节输出信号。共模反馈电路[11]的工作可以分为3个部分:感应输出共模电平、与理想输出比较、反馈调节信号。

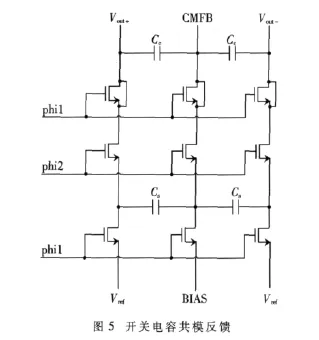

全差分运算放大器的难点在于共模反馈电路的设计。本设计用到了2种主要的共模反馈电路:连续时间共模反馈和开关电容共模反馈。前者常常会在最大化信号幅度上存在不足,从而导致输出摆幅上的局限性,因而用在对输出摆幅要求不高的辅助运放中。后者一般用于开关电容电路中,在非连续时间的应用中具有很好的共模电压调节作用,而在Pipelined ADC中,运放工作于非连续时间状态,因而在主运放中采用开关电容共模反馈电路。

连续时间共模反馈电路如图4所示。在1.1中已经提到,辅助运放的单位增益频率要介于闭环-3 dB频率和主运放的非主极点之间,因而构成辅助运放的共模反馈电路工作速度必然要快,连续时间共模反馈电路正好可以满足这个要求[12]。在图4中,PMOS管 M1~M4的宽长比相同,当辅助运放的2个输出端与理想的输出VCOM相等时,流过这4个管子的电流是一样的,通过NMOS管的电流源镜像作用产生CMFB反馈信号,反馈到辅助运放中,达到调节输出电压的目的。图5为开关电容共模反馈电路,phi1、phi2是两相不交叠时钟,Vout+、Vout-是主运放的2个输出端,CMFB是共模反馈电路产生的调节信号,Vref是主运放理想的输出电压,BIAS是理想的共模调节电压。

当phi1是高电平时,电路总电荷为:

当phi2是高电平时,电路的总电荷为:

根据电荷守恒定律Q1=Q2可得:

2 仿真结果与对比

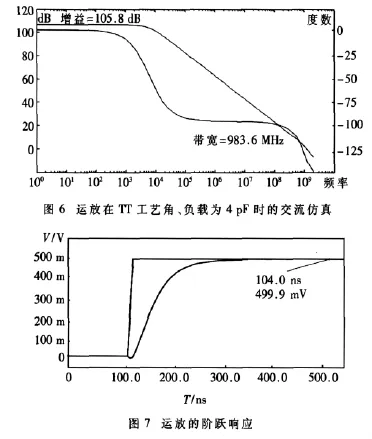

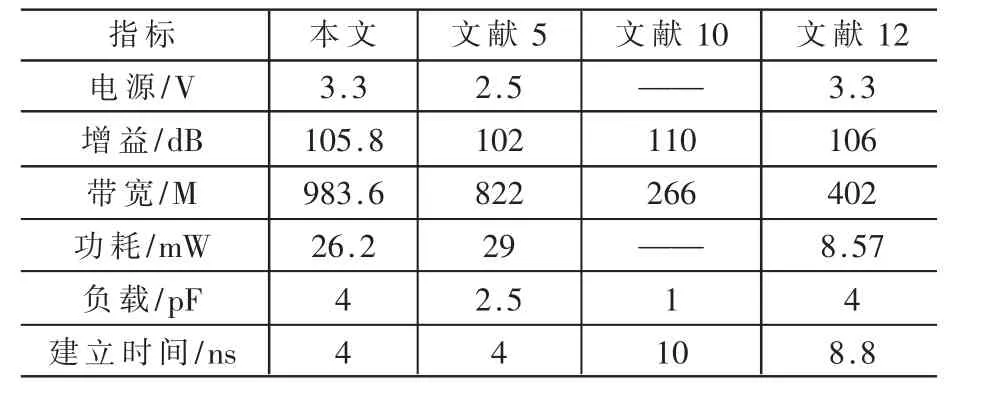

通过以上分析,设计了一个全差分的增益增强型套筒式运放。 基于 SMIC 0.13 μm、3.3 V工艺,Spectre交流仿真结果如图6所示。该运放可以达到105.8 dB的直流增益、单位增益带宽为 983.6 MHz、在负载为 4 pF时相位裕度是53°,功耗仅为26.2 mW。运放的瞬态建立特性如图7所示,在建立精度为0.01%时,运放在4 ns内建立到所需要的精度。该运放在不同工艺角下的仿真结果如表1所示。在3种工艺情况下,该运放均能满足设计目标。表2给出了本文同其他文献的比较。由比较可知,在衡量运算放大器的关键指标上,本文均具有良好的性能。

表1 不同工艺角下运放的仿真结果

表2 本文同其他文献的比较

基于单级架构、增益增强等技术设计了一个套筒式运放。Spectre仿真结果表明,该运放能够达到105.8 dB的高增益,单位增益带宽可以达到983.6 MHz,瞬态建立时间只需4 ns,而功耗仅为26.2 mW。该运放可以满足12 bit、100 MS/s Pipelined ADC对高性能运算放大器的要求。

[1]LLOYD J,LEE Hae-Seung.A CMOS op amp with fullydifferential gain-enhancement[J].IEEE Analog and digital signal processing,1994,41(3):241-243.

[2]YUN Chiu,PAUL R.G,NIKOLIC B.A 14 b 12 MS/s CMOS pipeline ADC with over 100 dB SFDR[J].IEEE Journal of Solid-State circuits,2004,38(12):2139-2151.

[3]GERMANO N,PIERANGELO C,DANIEL S.A fully differential sample-and-hold circuit for high-speed applications[J].IEEE Journal of Solid-State Circuits,1989,24(5):1461-1465.

[4]CHOKSI O,RICHARD L C.Analysis of switched-capacitor common-mode feedback circuit[J].IEEE Analog and digital signal processing,2003,50(12):906-917.

[5]苏立,仇玉林.一种全差分增益提升运放的设计与建立特性优化[J].电子器件,2006,29(1):162-165.

[6]YAO Zhi Jian,MA Cheng Yan,YE Tian Chun,et al.Design and analysis of a Gain-Enhanced,fully differential telescopic operational transconductance amplifier[J].Journal of semiconductors,2008,29(2):269-274.

[7]CHOKSI O,RICHARD L C.Analysis of switch-capacitor commom-mode feedback circuit[J].IEEE Transactions on circuits and systems-2:Analog and digital signal processing,2003,50(12):906-917.

[8]AMINZADEH H,DANAIE M,LOTFI R.Design of highspeed two-stage cascade-compensated operational amplifiers based on settling time and open-loop parameters[J].INTEGRATION;The VLSI journal 41(2008):183-192.

[9]拉扎维,陈贵灿等编译.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2003:75-77.

[10]朱颖,何乐年,严晓浪.高速高增益运算放大器的设计及应用[J].电路与系统学报,2008,13(2):31-35.

[11]何峥嵘.运算放大器电路的噪声分析和设计[J].微电子学,2006,36(2):148-153.

[12]ZHANG S,HUANG Lu,LIN Bei Yuan.Design of a lowpower,high speed op-amp for 10 bit 300 Ms/s parallel pipelined ADCs.Proceeding fo the 2007 IEEE International Conference on Integration Technology,2007:504-507.