基于FPGA+DSP的雷达信号处理模块的设计

2010-01-27闫大伟向建军

闫大伟,吴 军,向建军

(空军工程大学 工程学院,陕西 西安 710038)

基于FPGA+DSP的雷达信号处理模块的设计

闫大伟,吴 军,向建军

(空军工程大学 工程学院,陕西 西安 710038)

针对现代机载雷达信号处理系统的通用性、灵活性要求,提出了一种基于 DSP+FPGA的雷达信号处理系统的设计方法。以机载PD雷达信号处理系统为例,给出了测试结果,完成的系统具有高可靠性和实时性。

雷达信号处理系统;现场可编程逻辑阵列;数字信号护理;模块

1 雷达信号处理机方案设计

1.1 雷达信号处理的目的

现代机载雷达信号处理的任务繁重,主要功能是在空空方式下将AD数据录取后进行数字脉压处理、数据格式转换和重排、加权降低频谱副瓣电平,然后进行匹配滤波或相参积累(FFT或 DFT)、根据重复频率的方式进行一维或二维CFAR处理、跟踪时测角等运算后提取出点迹目标送给数据处理机。空地方式下还要进行地图(如RBM和SAR)等相关图像成像处理,最后坐标转换成显示数据送给显控处理机。

上述任务需要基于百万门级可编程逻辑器件FPGA与高性能DSP芯片作为信号处理模块,以充分满足系统的实时性要求,同时为了缩短机载雷达系统的研制周期和减少开发经费,设计的基本指导思想是通用化的信号处理模块,可以根据不同要求,通过软件自由修改参数,方便用户使用。

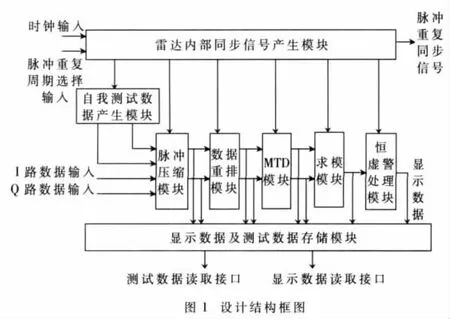

1.2 系统模块化设计方案

如图1所示的功能模块,除了信号处理所必需的脉冲压缩模块、为MTD模块作准备的数据重排模块、FIR滤波器组模块、求模模块、恒虚警处理模块和显示数据存储模块外,还包括雷达同步信号和内部处理同步产生模块、自检数据产生模块以及不同测试点测试数据采样存储模块。这些模块更加丰富了系统的功能,使得雷达系统的研制者能够更方便地测试和观察信号处理各功能模块的工作情况。

主要功能模块的具体功能描述如下[3,4]:

(1)正交采样是信号处理的第一步,担负着为后续处理提供高质量数据的任务,中频接收机输出的信号先通过A/D转换器进行采样,然后进行正交解调,以获得中频信号的基带信号(也称为中频信号的复包络)的I、Q两路正交信号,采样的速率和精度是需要考虑的首要问题,采样系统引起的失真应当被限定在后续信号处理任务所要求的误差范围内。

(2)脉冲压缩模块是在发射峰值功率受限的情况下,使用匹配滤波器将接收到的宽脉冲信号变成窄脉冲且保持能量不变,以获得更高的距离分辨力和较远的探测距离,使得雷达作用距离和距离分辨力之间的矛盾得到较好的解决。

(3)MTD模块通过各种滤波器,滤出杂波而取出运动目标的回波,从而大大改善了杂波背景下检测运动目标的能力,而且提高了雷达的抗干扰能力。

(4)采用恒虚警模块能够随着观测目标的背景杂波大小而自适应调整地门限代替固定门限,以防止杂波干扰增大时虚警概率过高,从而保证当杂波功率或其他参数发生变化时,输出端的虚警概率保持恒定。

2 系统硬件实现

基于以上实现方案,雷达信号处理器的硬件结构如图2所示,主要硬件资源为:一片Xilinx公司Virtex-4系列的XC4VSX55芯片,该系列器件整合了高达200 000个逻辑单元,系统时钟高达500 MHz,并具备高密度和低功耗的特点;一片TI公司的TMS320C6416芯片,系统时钟达600 MHz~1 GHz,运算速度可以达到4 800 MIPS,用户可根据对处理速度的需要,选择不同的工作主频;12片ADI公司的数模转换器 AD9765。

该信号处理流程可分为 3个阶段:(1)预处理,由雷达接收机接收到的信号经过放大器,滤波后通过A/D进行采样,包括数据格式转换及数字脉冲压缩;其次是信号处理阶段,信号处理系统根据工作方式,完成相参积累、MTD检测及 CFAR,或者完成图像处理,例如实波束地图(RBM)和SAR,主要通过写入主处理FPGA算法完成;(2)处理主要完成结果的汇总、噪声统计以及诸如抗干扰之类的处理,这一过程主要由扮演协处理器的DSP芯片组处理,并进行转存结果并显示。通讯接口采用RS-232串行接口连接器的9针DB9,实际使用时只使用了其中的RXD、TXD、信号地三条线;(3)由于RS-232电气规定与常用的TTL或CMOS电平不兼容,故在与相关电路连接时,要使用专门的电平转换芯片[6]。

3 系统软件设计

雷达信号处理机的软件设计包括两方面:FPGA内部功能模块设计和DSP控制程序设计。

3.1 FPGA内部功能模块设计

FPGA内部功能模块设计是整个系统的核心,主要功能是雷达回波数字信号的处理以及DSP接口和其他对外接口逻辑设计。雷达回波信号处理是本系统的核心,包括数字正交解调、脉冲压缩处理、MTD、恒虚警处理等算法的硬件实现。

另外,FPGA还需要完成与计算机、DSP以及数模转化器的通讯功能。与通用计算机采用RS-232串行通讯接口,与DSP通过EMIF连接实现FPGA与DSP之间数据交换与存储。因此,FPGA在逻辑设计时主要包括RS232接口逻辑、与DSP接口逻辑、信号处理算法逻辑以及输出逻辑4个部分。

3.2 DSP控制程序设计

DSP在整个系统中起着控制、调整的作用,DSP与FPGA之间通过 EMIF连接实现相互间的数据交换。系统的DSP软件设计包括接收程序和串口程序两部分。接收程序完成从FPGA读取目标处理结果任务,数据接收后存储在内部RAM中。串口程序完成处理后信号到下位数据处理系统的发送任务。程序从判断串口的 FIFO为空引起中断开始,读取DSP内部RAM缓冲区中数据,并按照通信协议由串口发送目标结果信息。

4 主要特点

设计的信号处理系统最突出的特点是高度并行、数据吞吐量大及实时性高。以大规模FPGA及高性能DSP共同构造的信号处理系统具有以下优点:

(1)软硬功能的重新划分及软硬协同。对于一个算法,用硬件实现的特点是速度快实时性强,但硬件设计较为复杂、灵活性差、精度较受限制。此系统可以在速度与精度要求上达到相对平衡。

(2)对外具有丰富的接口,既可以当作一块独立的板卡使用,也可以在CPCI机箱上作为标准板卡使用;同时,其具有丰富的底层软件库,可以提供良好的二次开发空间。

(3)设计的通用化的信号处理模块,可以根据不同的要求,通过软件自由修改参数,方便用户使用。

(4)高速串行互联技术的成熟,解决了多年来一直困扰系统发展的带宽不足问题,用串行通道取代并行总线已成为趋势,并且其优势是显而易见的。

5 应用举例

选择机载雷达的模拟回波信号在 L结构(LPRF和MPRF模式简称L结构)下进行处理,通过计算机仿真分析系统的可操作性以及可靠性。在L结构下,各个参数如表1所示。可以看出只是脉冲重复周期和信号形式的不同,因此只需要根据不同的信号选择不同的脉冲压缩系数即可。

表1 LPRF及MPRF参数

(1)混频:由于中频 60 MHz,采样 48 MHz,故混频NCO频率为12 MHz,如图3所示。

(2)DDC:由于滤波器的影响,经过抽取后的数据率应大于等于信号带宽的1.25倍,即抽取后的数据率应大于2.5 MHz,选取抽取率为 8,则抽取滤波器的阶数为160阶,抽取后数据速率为6 MHz。下变频后信号I(XS05输出)、Q(XS06输出)由DA送出可供观察,如图4所示。

(3)脉冲压缩:LPRF有 3种信号形式:7位巴克码,13位巴克码,线性调频。因此需要不同的匹配滤波器系数,此处信号处理根据不同的信号形式自动切换。图5是线性调频信号脉压后的仿真波形。

(4)动目标检测及恒虚警:MTD采用8点的FFT实现,恒虚警采用两边距离单元平均算法,保护单元为2,平均单元为8。如图6所示为经过FFT后8个通道取模仿真波形以及恒虚警门限仿真波形,此图中恒虚警系数为1。

雷达信号处理是雷达系统的一个极其重要的组成部分,现代雷达技术的发展越来越倚重于信号处理。本文基于FPGA的可编程系统,从而具有设计灵活、集成度高、功耗低、开发周期短以及开发成本低的优点,实现了一个通用的雷达信号处理机平台。实验表明,这种信号处理机实时处理能力强,结构可重构性强,对雷达信号处理算法的适应能力较强,并且工作稳定可靠。

[1]杜子妮.基于 DSP-FPGA的通用数字信号处理模块的设计[J].雷达与对抗,2006(4):19-21.

[2]李悦丽,周智敏,薛国义.一种基于 DSP和 FPGA的雷达信号处理机设计[J].现代雷达,2004,26(10):32-35.

[3]柳兵.机载 PD雷达信号处理系统的设计[D].西安:西安电子科技大学,2007(1).

[4]吴顺军,梅晓春.雷达信号处理和数据处理技术[M].北京:电子工业出版社,2008.

[5]杨剑,张月,陈曾平.数字化通用信号处理机设计[J].电路与系统学报,2009(4):25-28.

[6]孟庆海,张洲.VHDL基础及经典实例开发[M].西安:西安交通大学出版社,2008.

[7]梁丽.基于 FPGA的雷达信号处理系统设计[D].南京:南京理工大学.2006.6.

Design of radar signal processing module based on DSP and FPGA

YAN Da Wei,WU Jun,XIANG Jian Jun

(Engineering Institute,Air Force Engineering University,Xi′an 710038,China)

:According to the requirement of general usage and flexibility for the modern airborne radar DSP system,a radar digital signal processing architecture is designed based on DSP and FPGA.The design method is introduced briefly,the hardware constitutions and software design of the system are expatiated,the advantages of the radar DSP architecture are summarized.The test result is present with the realization of a pulse compression radar as an example in the end.

radar DSP system;FPGA;DSP;module现代雷达特别是机载雷达数字信号处理机的特点是输入数据多,工作模式复杂,信息处理量大。因此,在一个实时信号处理系统中,雷达信号处理系统要同时进行高速数据分配、处理和大量的数据交换[1]。而传统的雷达信号处理系统的设计思想是基于任务,设计者针对应用背景确定算法流程,确定相应的系统结构,再将结构划分为模块进行电路设计。这种方法存在一定的局限性。首先,硬件平台的确定会使算法的升级受到制约,由此带来运算量加大、数据存储量增加甚至控制流程变化等问题[1]。此外,雷达信号处理系统的任务往往不是单一的,目前很多原来由模拟电路完成的功能转由数字器件来处理。系统在不同工作阶段的处理任务不同,需要兼顾多种功能。这些问题都对通用性提出了进一步要求[2]。随着大规模集成电路技术、高速串行处理及各种先进算法的飞速发展,利用高速DSP和FPGA相结合的系统结构是解决上述问题的有效途径。

TN957.51、TN959.7

A

0258-7998(2010)09-0061-03

book=67,ebook=56

2010-03-15)

闫大伟,男,1986年生,硕士研究生,主要研究方向:智能信息处理。

吴军,男,1972年生,副教授,硕士,主要研究方向:智能信息处理。

向建军,男,1975年生,主要研究方向:雷达信号处理。