ProASIC3

2009-03-02

随着工艺的不断进步,FPGA在逻辑密度、性能和功能上有了极大的提高,同时器件的成本也大幅下降,使得电子工程师逐渐倾向于在越来越多的产品中采用可编程逻辑器件。在突破了低功耗、低成本以及先进工艺的瓶颈后,FPGA不断以其可编程和灵活性向更多领域渗透,而众多厂商的加入更使得FPGA市场群星璀璨,FPGA的应用市场越来越广泛、应用的价值也越来越大。

FPGA的发展令人瞩目,从原来的晶体管、集成电路,再发展到简单的PLD,例如GLA、GAL等,接着出现了CPLD和FPGA,整个过程漫长而又曲折。从1985第一颗FPGA的诞生到现在的20多年间,FPGA技术的发展让人难以想象,速度、资源、集成度都超越了人们的想象,以至于各行各业都开始关注和了解FPGA。目前从工艺上大致可以分为3类FPGA:Flash工艺、SRAM工艺、Flash+SRAM工艺,每种工艺都有其优缺点,适应一定的场合。

本文主要介绍Flash工艺FPGA的内部架构,这是一种全新的技术,有助于读者了解FPGA内部结构、资源和功能等,也为读者对比现有的SRAM技术的FPGA提供参考依据。

1.ProASIC3的特点

ProASIC3是Actel第三代Flash架构FPGA中的第一个器件,是当前应用最广泛的Flash FPGA,它主要面向消费、汽车及其它成本敏感的应用领域。由于它的特点非常突出,因此越来越多的工程师转向使用ProASIC3,它具有如下特点:

·基于Flash架构,无须昂贵的配置芯片,单芯片解决方案;

·1.5万到300万个系统门,分类齐全,供用户自主选择;

·最大504kbit的双端口RAM和Ikbit的用户FlashROM存储器;

·最大616个用户可用I/O;

·最高350MHz的性能;

·具有128位的Flash Lock和128位的AES加密,保护设计不被盗取;

·具有很好的系统成本。

正因为上述的特点,Actel完全可以替换现有的CPLD和部分SRAM的FPGA,而且使产品更具特点,例如安全性更高、可靠性更强、更小的体积和更低的成本等。关于ProASIC3更详细的优势介绍已经在《Actel基于Flash架构的FPGA讲座(1)》中描述,下面将介绍组成FPGA的部件有哪些?它们之间的关系又将是怎样的?

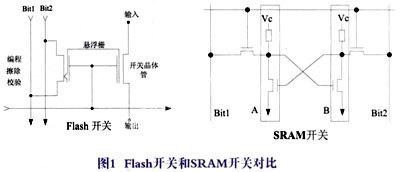

2.先进的Flash开关

FPGA与ASIC最大的不同点是具有可编程的特点,从而使得FPGA非常灵活,可以实现多种不同用途的ASIC。所以FPGA被看作是一种通用的ASIC,我们可以通过编写不同的代码来改变其功能,但是FPGA内部并不是所有的部件都可以让用户修改的,只有那些连线之间的开关可以通过程序来改变,最终的程序代码也是转换成对这些开关的控制。开关的性能决定了FPGA的性能,ProASIC3采用了Flash开关,因此带来的优点也是显而易见的。下面我们来对比2种不同的开关结构,如图1所示。

Flash开关采用一种称为悬浮栅的技术来保存开关的状态,将2个MOS管的栅极连接在一起,其中一个MOS管通过位选择信号Bitl和Bit2来控制悬浮栅上的电子,从而实现编程、擦除、校验等功能;另外一个MOS管用于互联其它的部件。当悬浮栅上被充电时该MOS管导通,当悬浮栅的电子被移除时该MOS管被关闭。Flash的开关只用了2个MOS管,因此功耗和面积更小,更多的空间用于布线,而且这种结构具有非易性的特点。

SRAM的开关使用4个MOS管来实现一个开关结构,而且2个上拉电阻往往也用MOS管来代替,所以一般需要6个MOS管,这样的结构功耗大,而且掉电后状态无法保存。

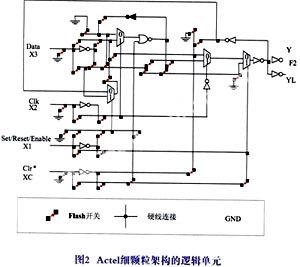

3.精细颗粒的逻辑单元

Actel所有Flash架构的FPGA都采用了精细颗粒的逻辑单元,这是FPGA最基本的物理逻辑单元,每个FPGA厂家都会不同,但也各具优势,有些厂家的逻辑单元为LE,而Actel的逻辑单元为Tile。Actel采用了精细颗粒的逻辑单元使得它的结构更加灵活,每个逻辑单元可以自由地转换成触发器或者查找表。触发器可以实现时序逻辑,查找表可以实现组合逻辑,如图2所示,其中逻辑单元内部除了一些门电路以外,还有许多可控的Flash开关,这些开关使得逻辑单元变得非常灵活,所以Actel的FPGA资源利用率可以在不影响性能的前提下接近100%。

而一般SRAM结构FPGA的逻辑单元,其内部结构都是固定的,无法灵活变动,内部由一个触发器和一个LUT组成,这就是所谓的粗颗粒结构的逻辑单元,其最小的单元都至少由一个触发器和一个LUT组成。当设计中只用到LUT时,另一半触发器的资源就浪费了。

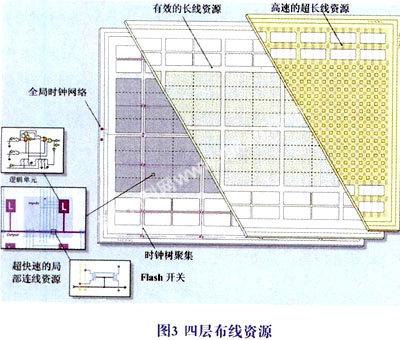

4.更优的布线资源

除了上述的2个资源外,FPGA很重要的一个组成部分就是布线资源,它直接影响设计的性能,足够多的全局网络可以让更多高扇出的信号以最短的延时、最小的抖动到达每个触发器,自然性能也将是最优的。ProASIC3具有7层金属层,其中4层用于布线,分别为:超快速的局部连线资源、有效的长线资源、高速的超长线资源和高性能全局时钟网络,类似于PCB的多层板,如图3所示。每种布线资源长短不一,根据实际情况供用户选择。

ProASIC3最多有18条全局网络:6条片上全局网络和12条象限全局网络。在一般的设计中这些全局网络已经足够用,全局网络可以走一些扇出特别大的信号,例如时钟、复位等信号,而这些信号的路径往往对一个系统性能起到了关键行性的作用。片上全局网络与每个逻辑单元相连,而象限全局网络与该象限内的逻辑单元相连,使得到达每个逻辑单元的时间最短,并且大致都相等。全局网络也可以分段利用,这样就会使得更多的信号上到全局网络,提高系统的性能。

5.ProASIC3的片内外设

开关、逻辑单元、布线资源可谓是FPGA的内核构成,现在FPGA的集成度越来越高,很多的外设都集成在FPGA内部,例如PLL、RAM、ROM等,ProASIC3也不例外。

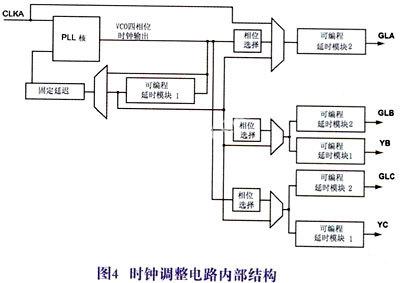

ProASIC3最多可以提供6个模拟的锁相环PLL,每个PLL位于CCC(时钟调整电路)中,其输入频率为1.5~350MHz,输出频率为0.75N350MHz,具有6个可编程的延时模块,3个相位选择和最多3个不同频率信号输出,如图4所示。

ProASIC3内部最多具有504kbit的SRAM,可以实现真正的双端口RAM(2个端口可以同时进行读写)和2个端口的RAM,同时这些RAM块带有FIFO控制器,可以实现先进先出队列的FIFO,RAM和FIFO速度可达350MHz。

ProASIC3内部具有1kbit的Flash ROM可供用户使用,类似于普通的ROM操作,通过上位机软件将数据固化在FPGA内部的FROM,FPGA在运行的过程中只能进行读操作,可以用于存放密钥、序列号、版本号等信息。

ProASIC3还具有超强的加密功能,内部不仅具有128位Flash Lock的加密,而且还有128位的AES加密。FlashLock主要对芯片进行加密,而AES是对编程文件进行加密,ProASIC3内部具有AES的解密引擎,用于对AES加密的文件进行解密。(待续)