面向多通道冗余系统的FPGA硬件脉冲同步方法研究

2024-08-31季浩刘凯孙献毓王忠尉杨国均姚佳烽

摘 要:提出一种基于现场可编程门阵列(FPGA)的硬件脉冲同步方法以保证冗余系统数据交互、任务调度的可靠性。以三通道冗余系统为例,每个通道都接收3个通道的脉冲信号输入,对3个通道的脉冲信号进行排序,确定主控通道的脉冲同步信号;捕获主控脉冲的信号边沿,计算与另外两个通道的同步偏差;设置不同粒度的调整区间,偏差大进行多周期调整,偏差小则进行单周期调整;建立基于FPGA的硬件脉冲同步仿真平台并进行测试分析。仿真结果表明:脉冲同步精度可达到20 ns,同步建立时间不超过470 ms,满足了多通道冗余系统的同步需求。

关键词:冗余;多通道;硬件同步;FPGA

中图分类号:V233.7文献标志码:A文章编号:1671-5276(2024)03-0010-05

Research on FPGA Hardware Pulse Synchronization Method for Multi-channel Redundant Systems

Abstract:A hardware pulse synchronization method based on field programmable gate array (FPGA) is proposed to ensure the reliability of data interaction and task scheduling of the redundant system. Taking the three-channel redundant system as an example, each channel receives pulse signal inputs from three channels, the pulse signals of the three channels are sorted to determine the pulse synchronization signal of the master channel. The signal edges of the master pulse are captured to compute the synchronization deviation from the other two channels. The adjustment intervals with different granularities are set with large deviations for multi-cycle adjustment and small deviations for single-cycle adjustment.The FPGA-based hardware pulse synchronization simulation platform is established and simulated. The simulation results show that the pulse synchronization accuracy can reach 20 ns, and the synchronization establishment time is no more than 470 ms, which meets the synchronization requirements of multi-channel redundant system.

Keywords:redundancy; multi-channel; hardware synchronization; FPGA

0 引言

冗余是容错控制的一种方法。容错控制的主要目的是当系统发生故障时,仍能保持控制目标的能力[1]。容错控制已经广泛应用于航空航天等要求高可靠性领域[2]。容错控制的关键因素之一在于冗余[3-4]。根据冗余信息的不同,冗余可分为硬件冗余和解析冗余[5]。硬件冗余将关键部件和易故障的部件进行备份,有些可靠性需求高的系统会将整个控制系统都进行备份[6]。本文基于硬件冗余进行研究。硬件冗余要求硬件设备有多个备份,多个备份即多个通道,由于时钟频率等误差导致通道间的行为也会有所不同。为了保证冗余的可靠性,各通道进行切换时需要保证一定精度的时间同步,这就对通道间的同步提出了要求。同步在容错控制中起到重要作用[7]。

通道间同步技术是各通道在同一时间进行相同任务调度的基础。同步按照实现平台的不同又可以分为软件同步和硬件同步。LIU等[8]提出基于公共时钟产生同步周期信号,进行通道数据交换比较、时间裕度计算完成系统同步和通信同步。ZHOU等[9]通过Petri网络描述了三模冗余系统任务同步的模型,直观地表达了任务同步的机制及过程。WANG等[10]设计了一种应用于四余度的“双握手”软件同步方法。YANG等[11]提出了用于时钟同步的过程弹性容错DLL设计,采用动态定时校正时钟误差,使三模冗余系统的时钟相位误差大大降低。

针对航电系统高同步精度和更短的同步时间需求,本文提出一种可应用于多通道的基于现场可编程门阵列(field programmable gate array,FPGA)的硬件脉冲同步方法,以保证系统可靠性。

1 影响因素分析

本文基于多通道冗余分析同步的影响因素。分析由于FPGA启动时间、通道间时钟不同步、布线时延问题而产生的通道间不同步。

1.1 上电启动不同步

为了避免共因失效,冗余系统虽然使用相同设计,但是也会采用不同硬件,器件的差异导致了上电的不同步[12]。航电系统常用28V直流电源,经过滤波、过压保护等电路后,经二次电源转换为后级电路提供电源。由于转换器件的差异,表现为上电上升时间的不同,整个控制系统的运行时间会存在一个初始的偏差。

1.2 时钟不同步

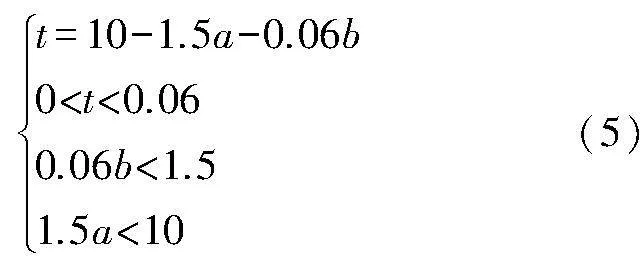

不同通道间采用相同频率的不同时钟源,由于时钟源器件的不同以及本身带有的误差,其误差经过系统长时间的运行而累积成可以对系统时钟造成影响的偏差,从而导致依赖于时钟的系统任务的不同步,如图1所示。

1.3 布线时延

电信号的传输速度取决于介质的介电常数,信号在PCB板中以有限的速度传输,从发送传输到接收端,传输时间的延迟受到速度与走线长度的影响。

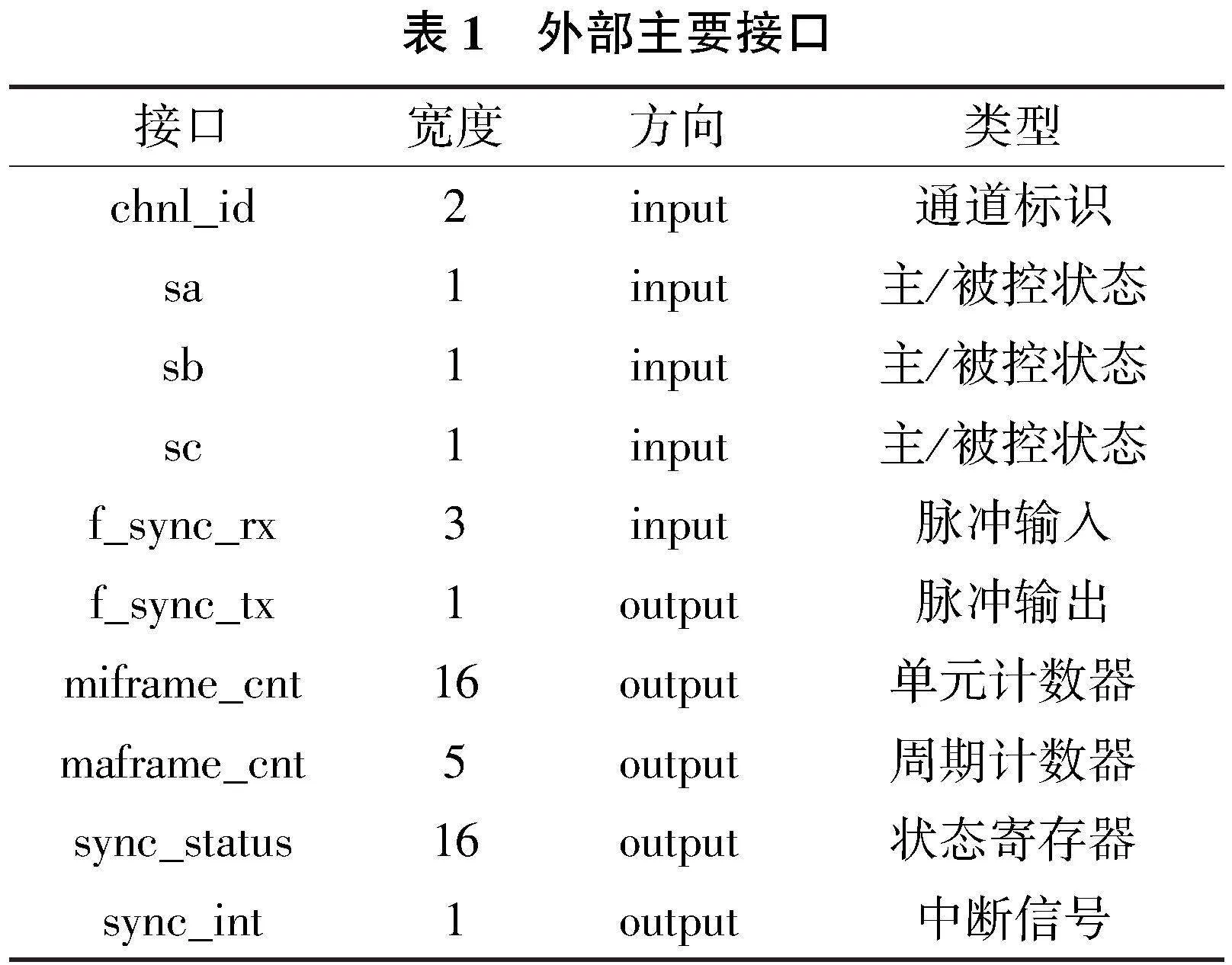

信号的传输速度v可由式(1)计算:

式中:ε0为自由空间的介电常数,其值为8.89×10-12F/m;εr为材料的相对介电常数;μ0为自由空间的导磁率,值为4π×10-7H/m;μr为材料的相对导磁率(几乎所有的互连材料相对导磁率都为1)。空气的相对介电常数和相对导磁率都为1,光在空气中的速度约为0.304 8 m/ns,则

根据经验法则,大多数聚合物的介电常数约为4,估算电路板中信号传输速度约为0.152 4m/ns,取其倒数作为传输时延的度量,即每米连线的时延为6.56ns。在信号远距离传输时需要考虑布线时延,将时间补偿加入到设计中。

2 硬件同步方案设计及实现

本文同步方案基于三通道进行设计,也可用于多通道系统。本方案A、B、C三通道冗余设计,功能相同,由FPGA采用硬件的方式实现通道间任务的同步。A通道同步信号为主控时,B通道、C通道同步信号跟随A通道进行同步校正;当A通道出现故障时,同步信号进行切换,以B通道为主控,C通道跟随B通道的同步信号。FPGA产生以同步周期为周期的中断信号给外部控制系统,实现三通道的同步功能,中断信号的同步通过调整脉冲信号对齐来完成。

2.1 整体架构

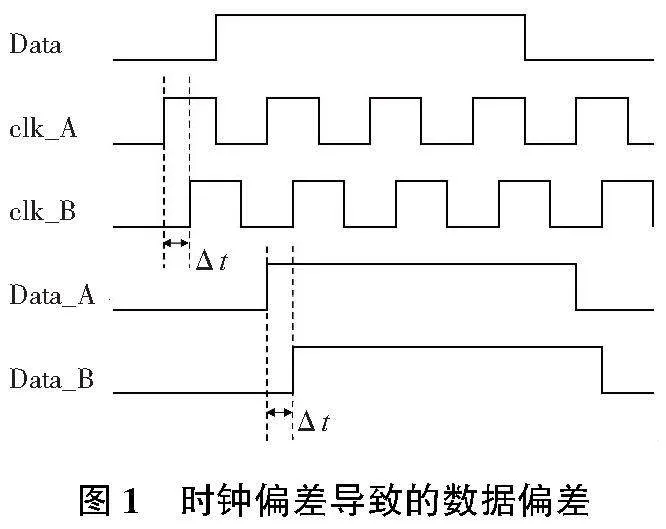

本方案的硬件同步电路及同步方法由FPGA实现,架构如图2所示。通道内FPGA包含排序电路、同步信号发生器、输入处理、分频器、计数器、状态寄存器、中断信号发生器,主要外部接口如表1所示。接口有3个同步脉冲输入,包含了另外2个通道的同步脉冲以及本通道的脉冲信号返回输入,返回输入是为了能用更简洁的逻辑实现同步脉冲输入的排序。

2.2 同步方案实现

设定同步脉冲基准周期50ms,采用周期调节方式,本通道同步脉冲落后于主控脉冲时,增加本通道同步脉冲的周期(每周期的增加幅度取决于脉冲偏差),超前时减小周期。主控脉冲信号输入本通道,与本通道输出脉冲有偏差,如图3所示。相位相差较大时采用多周期调节,相位相差较小时,采用单周期调节。调整范围及周期取决于同步脉冲周期等,根据实际需求设定其值。

1)同步脉冲排序及主控脉冲获取

当B通道作为主控时,A通道接收B通道的同步脉冲输出并跟随,在3个同步脉冲输入f_sync_rx[0]、f_sync_rx[1]、f_sync_rx[2]中需要判断出哪个信号来自于B通道。三输入脉冲的连接顺序如图2中排序电路所示,本通道输出脉冲返回硬线连接顺序为1,即连接到f_sync_rx[0]对应的引脚,按照1~N的数字顺序循环连接,如本通道为B通道时,f_sync_rx[0]连接本通道同步脉冲输出返回,f_sync_rx[1] 连接C通道同步脉冲,按照循环顺序连接,则f_sync_rx[2]连接A通道同步脉冲。然后将f_sync_rx[2∶0]根据通道标识chnl_id按照实际的通道顺序A、B、C进行重排序,缓冲一级,得到顺序的同步脉冲输入。

经过排序后,还需要根据主/被控状态信号判断本通道的控制状态以及主控通道号,根据本通道ID确定主控同步信号的序号。

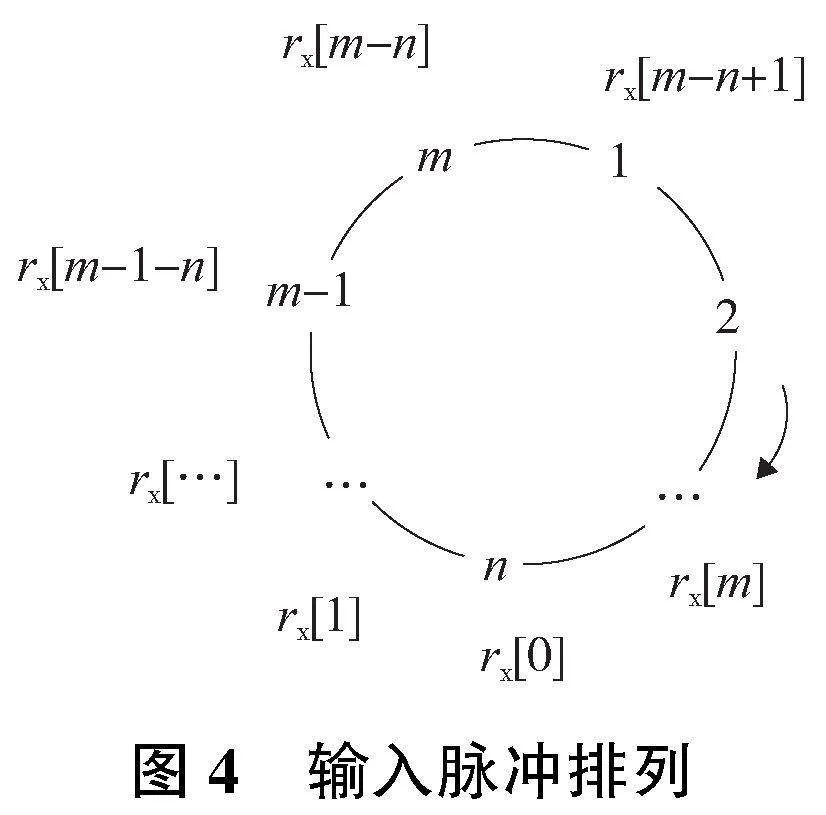

进行通道扩展时,每通道输入脉冲数量与通道数一致,输入顺序与上述三通道原理一致,本通道输入脉冲硬线连接rx[0],正序排列,设共m个通道,本通道序号n,则本通道输入脉冲连接rx[i]的顺序如图4所示。

2)方案实现

整个同步过程包括输入处理、计数、状态判断、同步脉冲输出等,具体实现如下。

a)sa、sb、sc确定主控/被控设备。

b)sa、sb、sc、chnl_id组合逻辑判断同步使能信号,当没有主控设备时,同步不使能。

c)同步脉冲信号与本设备脉冲信号周期、宽度相同。同步脉冲信号在接收到本通道时需要进行同步打拍、滤波、边沿采集才能捕获有效边沿,本通道同步脉冲输出时要把上述捕获时间计算在内,这样才可以保证捕获的有效边沿与发送通道起始相位一致,也可以避免毛刺信号和跨时钟域带来的亚稳态。

d)脉冲同步实现。当主/被设备同步脉冲上升沿时差满足调整精度时,判定主/被设备同步。否则,被控设备应判断与主设备之间的相位关系并通过渐进式调节实现与主设备的同步。两通道脉冲偏差应保持在一定范围内,若偏差过大,则认为主/被控设备出现故障,不同步。

e)相位偏差计算。设A通道为主控通道,B通道为随动通道。A、B通道同步脉冲信号的偏差为

式中:l0为同步脉冲初始偏差;dB、dA为B、A通道的脉冲周期;dB每个周期会进行调整,调整方式如下:

式中:dB[0]为B通道同步脉冲初始周期;sign(·)为符号函数;lstep为每周期调节步长。

接收主控脉冲时,由于传输路径和输入处理,还需要将同步打拍、滤波等补偿的延迟时间计算在内,且布线较长时,也要计算将布线时延。

f)调整策略。设置脉冲周期基准为20ms,每个脉冲周期含有25个调整周期,则调整周期的基准为0.8ms。调整单元是调整周期的基本组成单元,调整单元由时钟分频得到,分频后时钟频率50MHz,则每个调整周期的调整精度为20ns。在本通道脉冲初始周期开始2个计数器分别计数,单元计数器以50MHz为单位计数,周期计数器以调整周期计数,在检测到同步源边沿时2个计数器清零。根据检测的边沿所在的调整区间,将调整策略划分为多周期调整、单周期调整和单元调整,多周期调整策略增加或减小每个周期时间,单周期策略增加或减小1个周期时间。单元调整在检测边沿处于最后一个调整周期时发挥作用,当监测到边沿慢于本通道输出时,立即将计数器清零,在下一个周期完成同步;当监测到边沿快于本通道输出时,同样立即将计数器清零,这时输出脉冲宽度变小,在本周期完成同步。

3 验证及分析

3.1 仿真测试

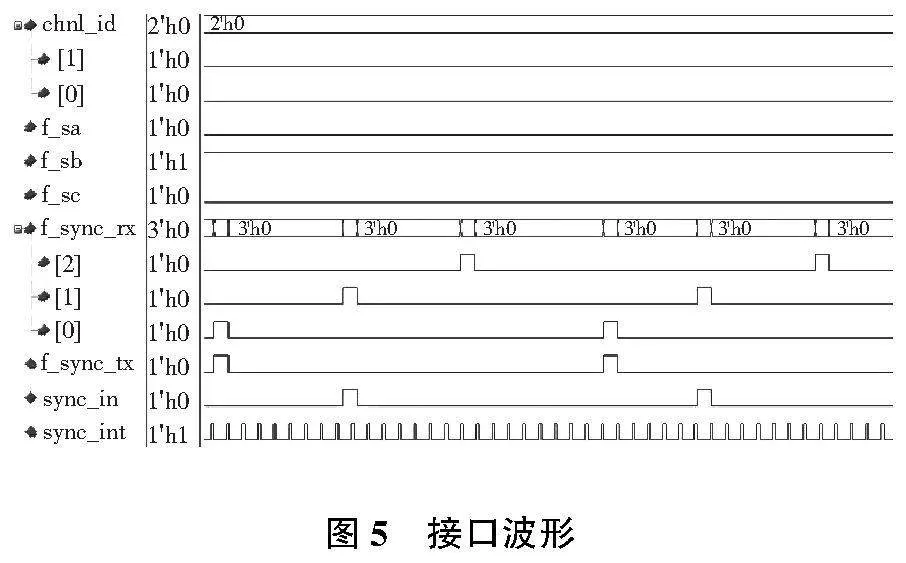

建立仿真测试平台,仿真环境Questasim10.5e。另外两个通道同步脉冲的产生采用与本通道相同的方法,频率一致,仿真时使用不同的起始复位时间以模拟通道间不同步。由图5可知,测试设定本通道ID为00,即A通道,主控信号高电平有效,即B通道为主控通道。f_sync_rx为进入本通道的B通道同步脉冲及经过组合逻辑和排序选择并缓存后的主控同步脉冲sync_in。

图6(a)为两通道的同步脉冲位于多周期调整范围,sync_in为缓冲后的主控通道脉冲,将计数器数值以模拟量显示,单元计数器miframe_cnt在每个调整周期都被增加了。图6(b)为经过多周期调整后,进入单周期调整,单元计数器miframe_cnt只在最后一个周期被增加。图6(c)进入单元调整,脉冲偏差小于单周期调整增加的时间。图6(d)为单元调整放大的主被控脉冲,调整后完成同步(脉冲与计数器清零边沿的偏差是同步打拍、滤波等补偿的延迟时间)。图7中sync_set_up是以调整周期为单位计数的同步建立时间,从0计数,计数399时建立同步,同步时间为320ms,同步误差为一个分频时钟周期,理论同步精度为所使用的分频时钟周期。

3.2 同步建立时间分析

被控脉冲不同步时只有超前或滞后于主控脉冲两种情况。这两种情况对应调整方案为脉冲周期增加或减少,增加或减少时最大同步建立时间相同。本节分析基于被控脉冲超前时,计算同步建立时间。

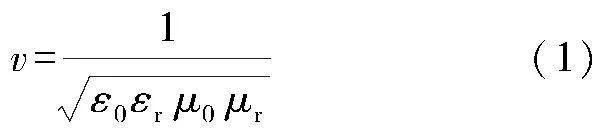

脉冲同步周期为20ms,则超前最大时间为同步周期的一半,10ms。本方案采用的多周期调整增加1.5ms,单周期增加0.06ms,单元调整范围为0~0.06ms,单元调整只需1次,则

式中:a为多周期调整次数; b为单周期调整次数,且都为整数;t为单元调整时间,同步建立时间Tsetup为

Tsetup=21.5a+20.06b+(20+t)(6)

使建立时间最大的a、b取值为6、16,最大同步建立时间Tsetup=470ms。

4 结语

1)针对冗余系统的同步需求,提出一种基于FPGA的硬件同步方法。经过排序后获得主控脉冲,同步过程划分为多周期调整、单周期调整、单元调整,以主控脉冲为基准调整同步偏差。

2)仿真结果表明,同步精度达到20ns,最大同步时间不超过470ms,保证了多通道冗余系统的同步需求。

参考文献:

[1] CHEMASHKIN F Y,ZHILENKOV A. Fault tolerance control in cyber-physical systems[C]. [S.I.]:IEEE,2019.

[2] 高桂军,王友仁,姚睿. 系统异构冗余容错设计研究[J]. 传感器与微系统,2007,26(10):25-28.

[3] 毛海杰,李炜,冯小林. 非线性系统主动容错控制综述[J]. 传感器与微系统,2014,33(4):6-9,13.

[4] 简荣坤,李冰冰,韩诚. 智能传感器故障诊断系统数据预处理方法[J]. 传感器与微系统,2016,35(9):27-29,32.

[5] 马立伟,王俊雷,林尚飞. 基于FMECA分析的无人收放控制系统冗余策略研究[J]. 机电工程技术,2022,51(6):92-95.

[6] HAZRA N K,NANDA A K. Component redundancy versus system redundancy in different stochastic orderings[J]. IEEE Transactions on Reliability,2014,63(2):567-582.

[7] LIU X Z,WU C. Fault-tolerant synchronization for nonlinear switching systems with time-varying delay[J]. Nonlinear Analysis:Hybrid Systems,2017,23:91-110.

[8] LIU B,YANG M F,WANG Y,et al. A lightweight data-voting strategy for triple-modular redundant control computers[J]. Science China Technological Sciences,2022,65(2):419-431.

[9] ZHOU S,XIONG G P. Modeling and analysis of task synchronization process based on Petri Net[C]//World Automation Congress. Puerto Vallarta,Mexico:IEEE,2012:267-271.

[10] WANG Y,JIA Z Q,ZHANG M. Research on the computer synchronization of the fault-tolerant system[C]//2020 3rd International Conference on Intelligent Robotic and Control Engineering (IRCE). Oxford,UK:IEEE,2020:18-22.

[11] YANG J Y,HUANG S Y. Process-resilient fault-tolerant delay-locked loop using TMR with dynamic timing correction[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2022,41(5):1563-1572.

[12] 宋征宇. 运载火箭冗余设计中的同步控制技术[J]. 载人航天,2013,19(2):11-16,37.