基于FPGA的SMS4高速数据处理算法设计

2024-08-03赵勇

摘要:随着集成电路的迅猛发展,为使数据通信安全性满足大数据时代的需要,文章详细研究SMS4算法,提出一种用双端口随机存取存储器(Random Access Memory,RAM)代替S盒的多路算法并行处理大数据的结构,并基于现场可编程门阵列(Field Programmable Gate Array,FPGA)实现这一算法。经仿真验证,所设计的结构都能正确处理大数据,其处理速度远超单个算法电路的处理速度。该算法与其他设计结构相比,其处理速度也占据相当优势。

关键词:FPGA;SMS4;加解密;轮密钥;高速数据处理

中图分类号:TP309文献标志码:A

0 引言

以“大量”“多样”“高速”为特征的大数据时代的到来使得通信中的数据保密安全问题成为信息安全领域中人们关注的焦点。确保重要敏感信息不被窃取窥探的常用方法是数据加密[1]。SMS4密码算法是国家密码管理局公布的第一个用于无线局域网产品的商用分组对称密码算法[2],是数字时代安全建设公众信息的基石。数字加密系统或设备通常具有数据处理速度快的需求,依据该特点,本文以速度优先为首要前提,提出一种基于FPGA的SMS4高速数据处理算法设计。

1 SMS4密码算法介绍

SMS4算法从性质上划分,属于分组密码算法[3];从结构上归类,属于典型的Feistel网络结构。其使用的分组、密钥长度均为16 Bit,且采用的加解密、轮密钥扩展算法也都是非线性迭代结构[4]。

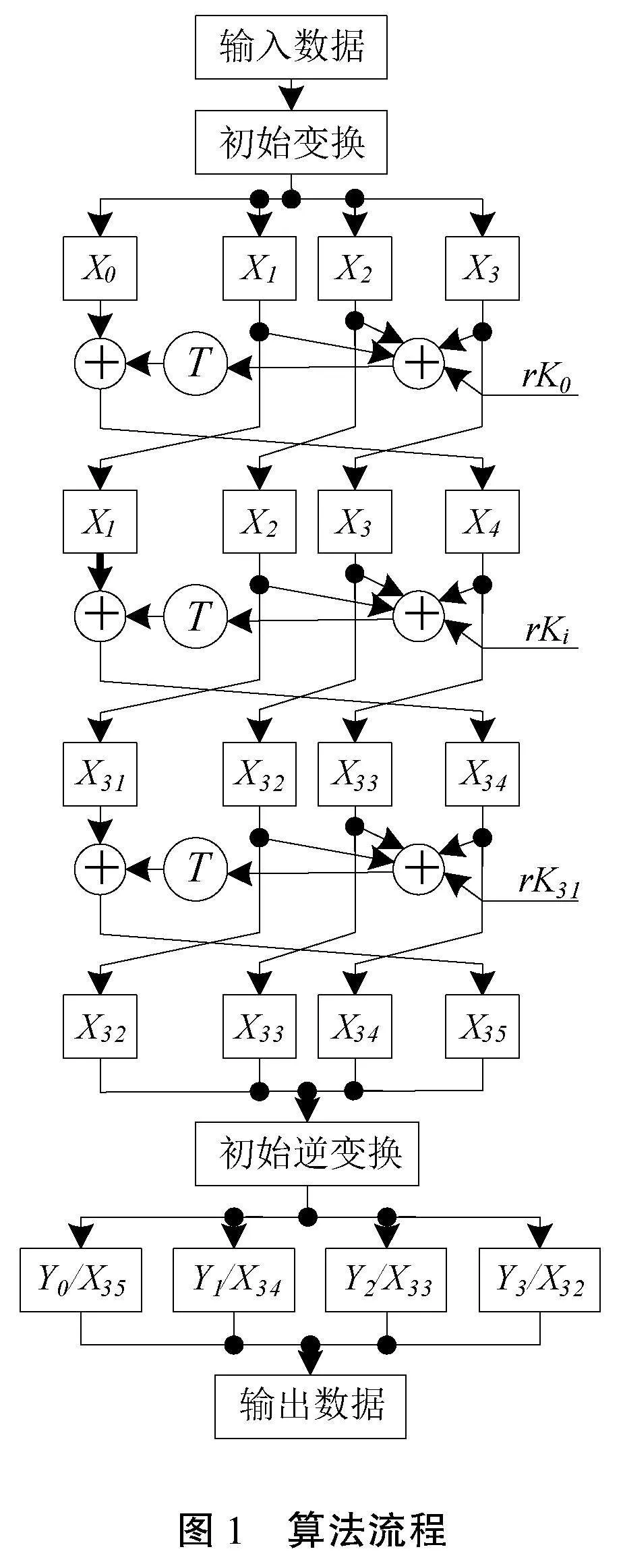

基于S盒(记为Sbox(.))的SMS4算法本质上属于分组对称密码算法[5],其将1组比特数据进行加解密运算。原始输入分组内部记为X,轮密钥记为rki(i=0,1,2,…,31),结果输出分组内部记为Y,用字母Z的下标表示进制类型,用字母Z的上标表示比特长度时,则X、Y、rki都是二进制32比特数,记做X、Y、rki∈Z322 [6]。算法中迭代生成的Xi+4是关于Xi、Xi+1、Xi+2、Xi+3、rki的轮函数(i=0,1,…,31),即Xi+1、Xi+2、Xi+3、rki的可逆变换结果再与Xi异或后的最终输出。将第32轮迭代运算结果逆序后得到输出结果为(Y0,Y1,Y2,Y3)=(X35,X34,X33,X32)。可逆变换(记做Td)既含有线性变换(记做Ld)又含有非线性变换(记做τ),归属于合成置换,表示为Td(.)=Ld(τ(.))。固定8 Bit输入8 Bit输出称为Sbox变换,而4个并行的Sbox构成非线性变换τ。当非线性变换输入用(a4,a3,a2,a1)表示,异或运算用⊕表示,循环左移i位用<<<i表示时,非线性变换输出H=(Sbox(a4), Sbox(a3), Sbox(a2), Sbox(a1)),则线性变换Ld=(H<<<24)⊕(H<<<18)⊕(H<<<10)⊕(H<<<2)⊕H[7]。当操作轮密钥顺序相反时,加解密运算互为变化,即加密时操作轮密钥顺序为rk0,rk1,…,rk31,则解密时操作轮密钥顺序必为rk31,rk30,…,rk0。算法流程如图1所示。

经过32次非线性迭代运算后生成32个轮密钥的轮密钥扩展算法与加解密算法的基本结构相同[8]。当原始密钥分组内部记为M,轮密钥记为rki(i=0,1,2,…,31)时,则M、rki都是二进制32比特数,记做M、rki∈Z322。初始密钥(K0,K1,K2,K3)为原始密钥(M0,M1,M2,M3)与十六进制系统参数(A3B1BAC6,56AA3350,677D9197,B27022DC)异或的结果,迭代而成的Ki+4(i=0,1,…,31)是Ki+1、Ki+2、Ki+3、cki的可逆变换结果再与Ki异或后的最终输出。其中ck称为固定参数,其选取方法为:设cki, j为cki的第j字节(i=0,1,…,31;j=0,1,2,3),即cki=(cki,0,cki,1,cki,2,cki,3)∈Z322,cki, j=(4i+j)×7(mod256) [9]。可逆变换(记做Tk)既含有线性变换(记做Lk)又含有非线性变换(记做τ),表示为Tk(.)=Lk(τ(.))。当非线性变换输出用P表示时,则线性变换Lk=(P<<<23)⊕(P<<<13)⊕P。

2 SMS4 算法的高速实现

SMS4属于分组对称密码算法,每次仅对单数据组进行加/解密,前后数据在加解密时无相关性[10]。因此,通过并行处理结构可以增加系统输出性能。该设计就是用16路单个SMS4算法电路并行工作实现的。

2.1 实现结构

16路单个SMS4算法电路并行工作的结构如图2所示。16路算法电路并行组成高速数据处理模块,轮密钥的提前生成、存储、分配等功能由轮密钥生成及算法控制模块实现。单个算法电路和轮密钥生成电路内部都是用2个8 Bit输入8 Bit输出的双端口RAM功能替换4个并行S盒。轮密钥生成及算法控制模块内含1个计算轮数的计数器,同时存储经32轮非线性迭代后提前生成的轮密钥。算法控制电路结合加解密模式和轮数取出提前存储的相应轮密钥,并把它们和轮数一起传递给高速数据处理模块。高速数据处理模块得到轮数及相应轮密钥信息后,再把它们和相应输入数据经过异或、合成置换、异或3步运算,上述步骤经过32次循环后,再将输出数据逆序处理,最终输出结果数据。

高速数据处理模块每输入16组待运算数据经过32个时钟周期后便产生一个算法完成标志信号(done),done信号持续一个时钟周期。因此,每33个时钟周期高速数据处理模块就会对外输出16组运算后的数据,此时新的16组输入数据又开始进行加解密运算,接着便循环以上过程。

2.2 仿真及算法设计结果比较

在ALTERA公司EP4CGX50CF23C6芯片实验板下,当输入明文(密文)32个时钟周期后,第34个时钟周期输出16组结果数据,此时用FPGA自带调试工具采集的验证结果不仅与仿真结果相同而且与国家密码局公布的数据也相同。

用1组固定密钥对1组固定明文反复加密106次,每次结果都正确,而且耗时较短,实践证明该模块高效地完成了SMS4的高速加密解密。经Altera系列EP4CGX50CF23C6芯片板级验证,逻辑处理时钟最高频率可达113.92 MHz,峰值处理速率7.07 GBit/s,远超常规设计峰值处理速率(455.7 MBit/s)[10]。

表1为已有算法设计与本文算法设计的结果对比。通过比较分析可知:在相同时钟频率下本设计的处理速度近似为半流水(8轮)的2倍,同时相比传统流水线也节省了大量的资源。

3 结语

在大数据时代,为适应海量数据安全性,研究SMS4高速数据处理算法设计具有重要意义。依据算法原理,本文不仅设计出各运算单元的高效合理方案,而且针对算法具体使用场景,还提出了一种基于FPGA的多路并行处理结构,并在仿真验证中验证了所提算法的有效性。

参考文献

[1]张利华,吴松,蒋腾飞,等.基于FPGA的SMS4算法实现及在线验证[J].华东交通大学学报,2018(5):111-116.

[2]李玮,汪梦林,谷大武,等.SMS4密码算法的唯密文故障分析[J].计算机学报,2022(8):1814-1826.

[3]蔡玉莹,曲英杰.基于单轮循环结构的SMS4加密芯片的研究与设计[J].电子设计工程,2016(22):39-42.

[4]郑朝霞,资义纯,吴旭峰,等.SMS4算法串行化设计及其轻量级电路实现[J].华中科技大学学报(自然科学版),2016(2):61-64.

[5]王艳红.硬件实现SMS4密码算法的研究[J].自动化与仪器仪表,2015(6):133-134.

[6]朱勇,崔强强.基于SMS4的加密通信可编程片上系统设计实现[J].电子科技,2014(4):138-142.

[7]江依妹,曲英杰.SMS4密码的集成电路实现方法[J].青岛科技大学学报(自然科学版),2013(6):622-627.

[8]李瑞林,熊海,李超.基于循环移位和异或运算的对合线性变换研究[J].国防科技大学学报,2012(2):46-50.

[9]刘佳.对称密码算法S盒安全性分析[J].南京信息工程大学学报(自然科学版),2013(4):352-357.

[10]程海,丁群,杜辉,等.基于FPGA实现的SMS4算法研究[J].仪器仪表学报,2011(12):2845-2850.

High-speed data processing design of SMS4 algorithm based on FPGA

Abstract: With the rapid development of integrated circuits, in order to meet the security needs of data communication at the era of big data, after detailed study of the SMS4 algorithm, a structure of multi-channel algorithm parallel processing large data is proposed using dual-port RAM instead of S-box, and this algorithm is realized based on FPGA. Through simulation and verification, this structure can correctly handle large data, and its processing speed is more quickly than the processing speed of a single arithmetic circuits. Compared with other structures of the algorithm, its processing speed also occupies considerable advantage.

Key words: FPGA; SMS4; encryption; rotate cipher key; high-speed data processing