《微电子器件》课程的深度学习建设

2024-05-25赵红东孙梅韩力英

赵红东,孙梅,韩力英

河北工业大学 电子信息工程学院,天津,300401

0 引言

2018年教育部提出“淘汰水课”“打造金课”,坚持学生中心、产出导向、持续改进的理念,建设具有高阶性、创新性、挑战度的一流本科课程,以此示范带动更多高校和教师参与教学改革。因此,本科课程建设一流化是未来高等教育发展改革需要不断探索、不断推进的。过去两年,全国各高校都在积极申报各级一流课程,在这种时代背景下,电子科学与技术《微电子器件》专业课程组积极探索并向着一流课程建设,通过多元协同机制,科研与教学深度融合,多学科、多门课程交叉融合,建设两性一度的一流课程,使学生不仅在课程知识的浅层方面学习,更注重学生的能力培养等深度学习层面。

1 《微电子器件》课程的教学目标

半导体器件和集成电路是电子科学与技术的发展方向,其中集成半导体二极管、双极性晶体管(BJT)和场效应晶体管(FET)已经成为微电子器件的核心,是大规模集成电路、高功率和高频率电路的关键单元,因此,《微电子器件》是一门关键课程。该课程的教学目标分为知识、能力和素质目标。其知识目标是能够综合运用所掌握的知识、方法和技术,判断PN结、BJT、MS和场效应晶体管基本原理的正确性;建立分析半导体PN结、BJT、MS及场效应晶体管的物理模型以及数学描述,并正确证明其原理;能够运用晶体管中的原理,定量计算晶体管中参量,并分析晶体管参量中的关键因素;熟悉制造半导体器件过程中对应的器件结构,能够绘制晶体管结构和原理图。能力目标是能够运用数学、自然科学及工程基础知识,通过对具体问题的分析,增强创新意识、提升创新能力,提升解决复杂工程问题的能力。素质目标是通过该课程的学习,提高严谨务实的科学态度和科学素养。

2 深度学习的教学方法

该课程的教学内容比较抽象,微观理论知识学生很难掌握,将学生纳入科研团队,进行深度学习。课程组组建了微电子器件科研团队,不仅在课堂上进行理论教学,而且组织学生分组进入科研实验室,在科研学长的指导下,完成器件结构的建模、特性的仿真,使学生全面参与挑战性的内容,达到对课程的深度学习,挖掘学生的创新思维,初步了解科研的最新成果,使科研反哺教学,教学为科研服务,真正做到科研与教学的融合。例如,以一种新型GaN/AlN异质结隧穿场效应晶体管(TFET)的直流和射频性能研究来反哺教学。

3 深度学习举例

下面以一种新型GaN/AlN异质结TFET的直流和射频性能研究为例,引入学生深度学习的过程。

3.1 理论讲解

课堂上讲解理论,使学生了解TFET已成为实现高效率电子器件的候选器件。电子和空穴因量子隧穿而可以穿过能带势垒,而传统MOSFET(Metal Oxide Semiconductor Field Effect Transistor)的载流子导通机制是热扩散[1-2]。这种导通机制使得TFET可以在室温条件下实现低于60mV/dec的亚阈值摆幅(SS,subthreshold swing)[3-5]。然而,在TFET中实现高输出电流是研究人员面临的一个重大挑战[6]。TFET中载流子的带带隧穿主要存在两种阻碍:带隙之间的隧穿势垒高度、隧穿势垒的厚度[7]。由于窄带隙材料具有更低的隧穿势垒,因此,这种材料构成的隧穿晶体管通常能够获得更高的输出电流。然而,当器件为反向偏置状态时,过窄的能带会导致双极电流产生,这意味着更高的关断电流,并且破坏电路的操作逻辑[8-9]。具有优异开关性能的III族氮化物(如GaN和AlN)已成为电力传输应用的主要选择[10-13]。与Si相比,III族氮化物由于具有可调的能带和直接隙结构而得到广泛的关注。GaN/InN异质结TFET被认为是提升ION的一种方法[12]。AlN是一种宽带隙材料,AlN基TFET的双极电流很小。对于宽禁带半导体材料来说,它们的隧穿势垒高度很高,通常在这种材料的器件中发生隧穿的概率很小。一层薄的AlN夹在P型和N型GaN之间时,会在异质结表面引入极化电荷,这种结构称之为PITJ(Polarization Induced Tunneling Junction)[7,14,15]。同时,极化效应弥补了p型GaN材料杂质电离能过大的缺陷[16-17]。GaN掺杂的受主杂质Mg具有174meV的电离能,使得GaN器件难以实现重掺杂PN结,这不利于隧穿电流的产生。极化电荷的存在使得结边界能带弯曲,这种弯曲缩短了隧穿势垒的宽度,这会提升隧穿电流的大小[7]。

3.2 实验学习

在实验室中,通过科研让学生亲自模拟仿真一种带有AlN极化夹层的GaN/AlN异质结隧穿晶体管的结构和性质,来达到学生深度学习《微电子器件》课程的目的。

3.2.1 模型校准

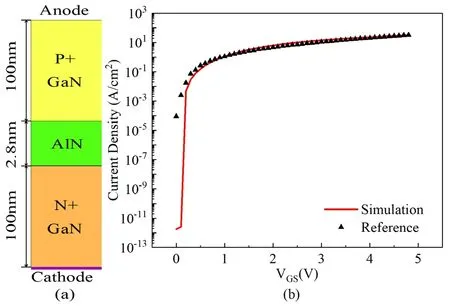

Atlas半导体器件模拟是一种常用的模拟半导体器件的电学性能和制造流程的一种工具。学生使用Atlas仿真软件,建立模型。GaN基隧道二极管的结构与校准结果分别如图1(a)[15]和图1(b)所示。对该器件进行校准时,重点关注极化效应对隧穿电流的影响,因此,当二极管尚未导通时,模型与实验数据存在较大偏离。

图1 隧穿二极管

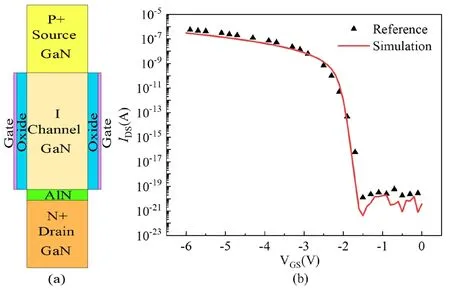

GaN/AlN异质结TFET的结构与校准结果分别如图2(a)[7,18]和图2(b)所示。

图2 GaN/AlN TFET

3.2.2 实验结果

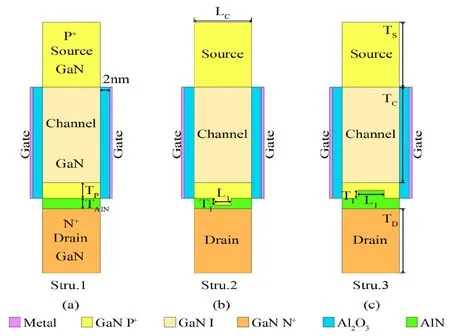

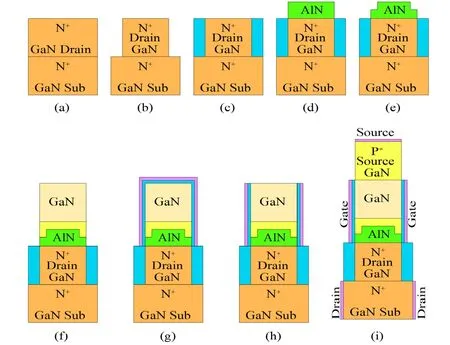

指导学生使用Atlas仿真软件对半导体器件进行电学参数的仿真。器件的具体结构如图所示,图3(a)为传统的对照结构,图3(b)为AlN基夹层凹陷型TFET,图3(c)为AlN基夹层凸起型TFET。

图3 器件结构图

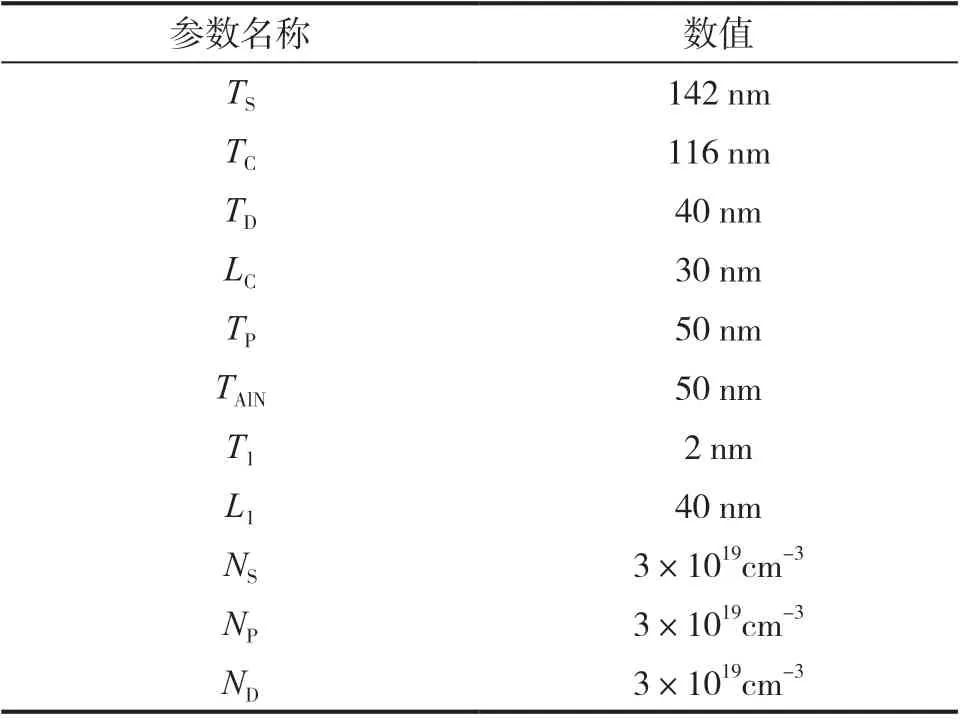

表1所示为器件结构的具体参数值。TS、TC和TD分别是源区、沟道和漏区的厚度,TC是器件的长度,TP是GaN口袋层的厚度,TAlN是AlN极化层的厚度,T1和L1分别是扩展AlN层的厚度和长度,氧化物的厚度固定在2nm。

表1 器件参数和对应数值

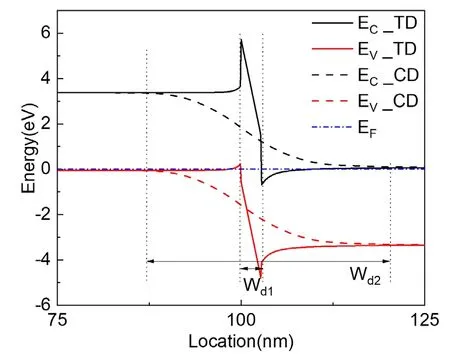

极化效应对器件的能带的影响如图4所示。实线所示为带有AlN夹层的隧穿二极管导带与价带能带图(EC_TD以及EV_TD),虚线所示为没有AlN夹层的普通GaN二极管能带图(EC_CD以及EV_CD),能量为0处的虚线是费米能级的位置。隧穿二极管的隧穿势垒宽度显著小于普通二极管的隧穿势垒宽度,这有助于提升载流子的隧穿概率。

图4 GaN/AlN 隧穿二极管的能带示意图

器件的简要工艺流程如图5所示。漏极区利用分子束外延(MBE,Molecular Beam Epitaxy)在GaN衬底上生长[图5(a)],然后刻蚀漏极区[图5(b)],SiO2沉积在漏区两侧[图5(c)]。AlN层同样由MBE生成[图5(d)],氧化层作为硬掩膜沉积在AlN层上,之后AlN层被部分刻蚀[图5(e)],重p型GaN和本征GaN先后在此基础上由MBE生长[图5(f)]。栅极和栅极氧化物通过沉积法生成[图5(g)]这两层材料之后会被部分蚀刻[图5(h)]。源极层由MBE生长,三个电极由金属沉积生长[图5(i)]。

图5 GaN TFET 制造流程

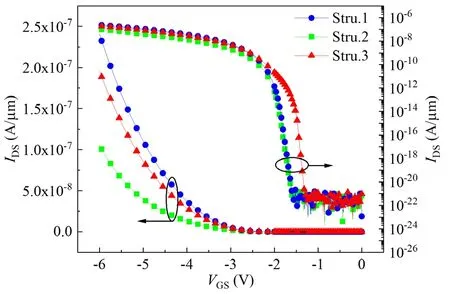

这三种结构的转移特性曲线如图6所示。坐标右侧刻度为半对数坐标,左侧为线性坐标。由图6可以看出,结构3的转移特性曲线具有更低的亚阈值电压、更低的亚阈值摆幅以及与结构2相差不大的输出电流。因此,结构3所示的TFET具有更好的电学性能。

图6 三种结构的转移特性曲线

3.2.3 器件深度学习结果

学生通过分组进入实验室,使用软件模拟器件结构及特性,进一步了解了隧道击穿的原理,理解了不同结构的TFET器件的转移特性,初步建立了科研意识。

4 结论

深度学习能够使学生在知识学习中形成核心素养,使学生在课程内容学习中成长和发展。课程基础知识学习是浅层学习,是不能完成核心素养的培养的,因此,深度学习是未来教育的首要任务。本文采用教学与科研相融合的方式,从实验的角度,引导学生建立器件模型,进行仿真,深度学习器件的特性,以学生深度学习为主导建设一流课程,完成教学的最终目标,实现学生的全面发展。