一种基于FPGA的频谱实时检测系统

2024-05-25张跃为于宗光陆皆晟

张跃为,于宗光,陆皆晟

1.江南大学物联网工程学院,江苏无锡,214122;2.中科芯集成电路有限公司,江苏无锡,214035

0 引言

频谱实时检测在频谱管理的实施中扮演着至关重要的角色,尤其在电磁频谱管理、非法信号突变排查中显得尤为关键[1]。该设计致力于研究一种基于快速傅里叶变换(FFT)的实时频谱检测系统,该系统能够在连续的分析时间段内获得信号的频率和幅度信息。相对于传统系统,该系统对于检测时段内的突发瞬态信号具有出色的实时检测效果。此外,该系统还可用于对其他信号源识别系统设计的缺陷进行诊断和性能测试,呈现其独特的优势[2]。

1 总体设计方案

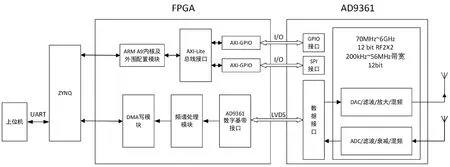

该设计获取频谱的方式为快速傅里叶变换。在这种方式下,待测信号经由AD9361数模转换后在FPGA上完成数据缓存,缓存的数据流进入频谱处理模块进行计算,计算完成后将数据通过DMA写模块写入UART打印到上位机显示频谱。此方案能够完美利用FPGA上丰富的硬件逻辑资源去编写相应的模块工作时序完成系统的连接和信号传输,这样不仅能够确保整个系统的实时性,同时也可以减少整个系统对滤波电路等其他外部电路的依赖性,从而进一步降低整个系统设计的成本,整个系统的总体设计方案硬件结构如图1所示。

图1 总体设计方案硬件结构框图

2 频谱处理模块的设计

2.1 频谱分析算法原理

由于通过AD9361接收到的无线信号经过ADC模数转换后,数据会从连续信号变成离散的信号,因此,对离散输入信号需要进行DFT(离散傅里叶变换),表达式为:

对于DFT运算来说,对于任意k都需要N-1次的加法操作以及N(N-1)次乘法操作。当进行加法和乘法操作时,FPGA不仅会调用大量的内部资源乘法器以及加法器进行处理,而且因为乘法运算复杂度为,加法运算复杂度为,所以,运算速度也相对较缓慢,无法满足实时性的需求,因此,DFT对于FPGA而言不宜作算法首选[3]。

首先输入序列可以分为两部分,一部分只含有原序列中奇数位的序列,另一部分只含有原序列中偶数位的序列,这两部分分别为和,此时=0,1,2,,公式(1)可进行化简:

最后得到:

图2 奇偶两项拆分累加图

也即:

通过公式(6)可知,输入序列为N的DFT运算结果可以拆分成序列为N/2的奇偶两式计算得到,被拆分后的奇偶两式的旋转因子依旧满足周期性、对称性和缩放性等特性,因此,可以对其进一步推算,从而将乘法运算复杂度和加法运算复杂度压缩为和,从而大大减小了计算量,极大地提升了FPGA的运算资源的利用率,缩短了运算的时间周期,从而提升了频谱运算的实时性[4]。

2.2 频谱处理模块设计

根据国际标准IEEE 1057规定的数字化和频谱计算的要求[5],频谱处理模块采用以下方案进行设计,如图3所示。

图3 频谱处理模块数据流

由图3可知,首先通过AD9361采集射频接收信号,并通过数字基带接口对数据进行差分转换与采集,采集的数据进入FFT快速傅里叶变换处理,处理完后的频谱实部与虚部的数据序列通过平方求和等计算完成功率谱计算,计算后的数据进入DMA中进行缓存,DMA模块输入一个结束地址,当数据量到达此地址时,拉高一个标志一定时间,并把这个标志接入ZYNQ的中断接口,PS端接收到中断之后执行中断函数,并且把FFT数据通过DMA中的异步FIFO完成跨时钟域高速数据传输,将数据通过UART打印到上位机中进行实时监测显示。

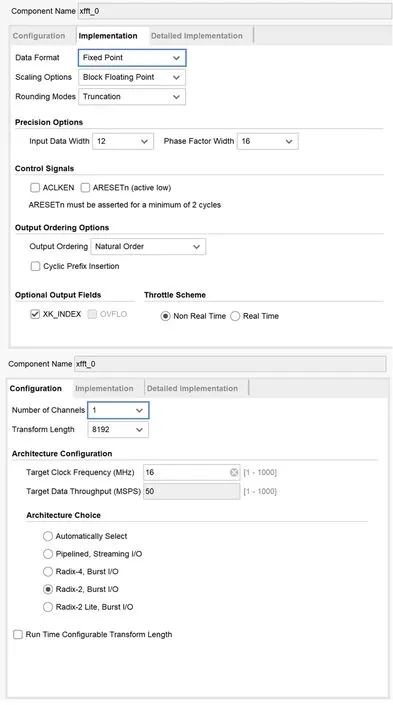

该设计主要分析的频谱范围为0~8MHz,根据奈奎斯特采样定律可知,单通道时的采样率最少需要设置为16MHz,由此,对其进行IP核配置,如图4为FFT IP核配置图。

图4 FFT IP 核配置图

由图4可知,该设计对IP核的配置为采样率16MHz,频谱序列为8192个数据,采用基-2时域抽取算法架构,在数据形式设置中,采用定点数并使用块浮点的方式完成数据的缩放截位,该方式不仅可以减小计算复杂度、有效减小存储的空间,还可以提高计算的速度满足实时性的需求[6]。

在整个频谱处理过程中,通过各种计数器以及标志位的触发可以完成相关的硬件逻辑模块的工作时序编写,如图5是FFT IP核与接收数据端以及触发模块的信号连接图。

图5 FFT IP 核与接收数据端以及触发模块的信号连接图

由图5可知,Cap Data模块连接到了FFT IP核的数据和控制信号输入端,根据ZYNQ中发出的GPIO脉冲信号可以截取从AD9361基带接口中采集的8192个采样点。最后,根据输出的实部与虚部求得功率谱,也就是实部平方加虚部平方运算,硬件模块信号连接如图6所示。

图6 功率谱运算硬件模块信号连接图

3 实验结果与分析

该设计的验证系统主要是通过ILA(在线逻辑分析仪)时序检测、上位机软件验证频谱以及MATLAB仿真对比进行验证。分析的对象主要为AD9361数字基带接口收发数据、FFT IP核输出值以及UART数据上传上位机打印频谱。为了证明该设计中的射频发射与接收端功能是否正确,对AD9361数字基带接口进行了DDS正弦波自发自收测试,图7为经AD9361数字基带接口发射并接收回来的ILA信号波形观测图。

图7 AD9361 数字基带接口收发数据波形图

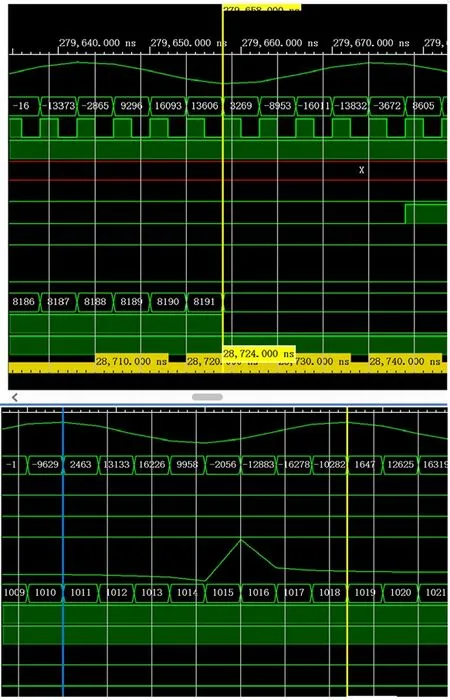

验证完射频收发的功能后,需要进一步验证FFT IP核模块的输出以及功率谱计算模块输出是否正确,这里设置射频发送端中心频率为100MHz,射频接收端频率为98MHz,频谱点数为8192个,且采样频率为16MHz,因此,当接收到8192点数据后产生一次数据抓取传输,此时可以查看ILA,若设置成功,则ILA中的FFT输出的频点会在1024附近处有一个频点响应,如图8所示。

图8 FFT 频点输出数据时序图

由图8可以看出,频率的估计值和实际波形中的频点由于频偏为1015,很接近1024,符合要求。由于该设计的采样频率为16MHz,且FFT计算长度为8192,数据位宽为16位,FIFO的写入时钟为32MHz,并且DMA传输采用AXI协议的256字节突发模式,这将大大提高数据的传输速率,因此,每从DMA中输出一次完整的8192个频点的16位频谱数据所需的时间为25.6ms,而在MATLAB仿真中所需的平均运算时间约为160ms,MATLAB仿真图如图9所示。为了验证上传给上位机8192点的频谱数据是否正确,设置了接收的数据格式,先接收4字节命令头,接着接收占4字节的FFT的长度FFT length,然后接收4字节FFT数据倍数因子;接收到前面12个字节后,上位机开始接收FFT数据,每个数据占用2字节,并且高字节在前,FFT数据数量和FFT length对应,如图10所示可看到上位机接收到的对应数据。

图9 MATLAB 频谱运算时间检测仿真图

图10 上位机接收串口频谱输出数据图

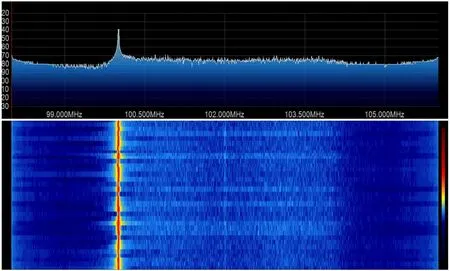

最后,将获得的数据包通过频谱显示软件,成功生成频谱实时监测,如图11所示。

图11 上位机频谱瀑布监测图

4 结论

针对各种不同的工业通信领域对信号频谱监测的需求,本文设计了一种基于FPGA的频谱实时监测系统,对FFT等关键技术进行了分析,利用FPGA中的可配置的FFT IP核提高了整个系统的运算效率,并通过ILA时序检测、上位机软件验证频谱,以验证该设计对大数据量的FFT频谱检测功能的正确性与稳定性,最后与MATLAB产生的实时计算时间做比较,表明该设计满足了较高的实时性,对后续频谱监测系统的研究具有实际的应用参考价值。