基于Proteus的计算机组成原理实验设计

2024-04-28曾昭平刘艺

曾昭平 刘艺

基金项目:上海立信会计金融学院金课建设项目(A0-11-180423-001002003034)

第一作者简介:曾昭平(1976-),男,博士,讲师。研究方向为计算机体系结构,人工智能。

*通信作者:刘艺(1979-),女,硕士,研究员。研究方向为高等教育管理。

DOI:10.19981/j.CN23-1581/G3.2024.12.026

摘 要:计算机组成原理实验需要大量的硬件和电路知识,购买实际的硬件和设备需要大量成本,且实验结果容易受各种因素影响。基于Proteus仿真软件,对计算机组成原理的总线、存储器、输入输出系统等各大组件进行仿真实验设计,不仅使用灵活方便,成本较低,而且实验结果能准确展示各大组件的工作原理,有助于了解各大组件的知识点。

关键词:计算机组成原理实验;Proteus;仿真软件;总线;存储器;输入输出系统

中图分类号:TP319 文献标志码:A 文章编号:2095-2945(2024)12-0116-04

Abstract: The computer composition principle experiment requires a lot of hardware and circuit knowledge, the purchase of actual hardware and equipment requires a lot of cost, and the experimental results are easily affected by various factors. Based on the Proteus simulation software, the simulation experiments are carried out on the bus, memory, input and output system and other major components of the computer composition principle. Not only the use is flexible and convenient, the cost is low, but also the experimental results can accurately show the working principle of the major components, which is helpful to understand the knowledge points of the major components.

Keywords: computer composition principle experiment; Proteus; simulation software; bus; memory; input and output system

计算机组成原理[1]是计算机科学与技术专业的主要课程之一,其内容偏向计算机硬件,具有很强的专业性。

学习计算机组成原理[2]不仅要依托书本的理论知识,还要进行实际的计算机硬件实验,才能帮助理解计算机各大部件的工作原理。

计算机组成实验[3]需要连接好各大硬件,输入数据,观察数据如何正确地在计算机中传输、存储、输入输出及处理等。如果使用实际的硬件实现这些实验,不仅需要繁琐的连线,配置各种仪表仪器进行测量和调试,还要考虑电路电气等因素的干扰,实验结果容易出现很大的不确定性,对掌握计算机组成原理造成影响。另外计算机硬件的升级换代非常快,对硬件的维修、保养、更新也会造成较大经济负担。所以有必要研究其他方法可以方便、快捷、准确地实现计算机组成原理实验。

1 研究内容

目前采用计算机仿真软件[4]是实现计算机组成原理实验快速有效的方法之一。计算机仿真软件无须另外购置硬件,在常见的普通计算机上即可运行。计算机仿真软件通过图形化界面形象地模仿计算机工作原理,展示计算机运行结果,即可准确实现计算机组成原理实验的各项功能,又可很好地控制成本。

Proteus[5]是英国Lab Center Electronics公司出版的计算机仿真软件。其不仅具有普通EDA工具软件的仿真功能,还能仿真单片机及外围器件。目前基于Proteus实现计算机组成原理实验的设计较少,本文通过使用Proteus计算机仿真软件,研究如何能够较好地设计计算机组成原理的各大组成部件的相关实验,展现计算机总线如何具备同一时刻只能有一个部件发送信息,其他部件同时接收到相同的信息的特点;计算机存储部件如何根据输入的存储单元的地址,访问存储单元的数据;计算机输入输出系统如何采用程序中断方式提高数据输入输出的工作效率等内容。

2 计算机总线实验设计

计算机总线[6]是计算机中各大组成部件的共享信息传输线,在计算机组成各大部件中负责数据的传输,其特点是同一时刻只能有一个部件发送信息,而其他部件能够同时接收到相同的信息。计算机总线的原理图如图1所示。

图1 计算机总线原理图

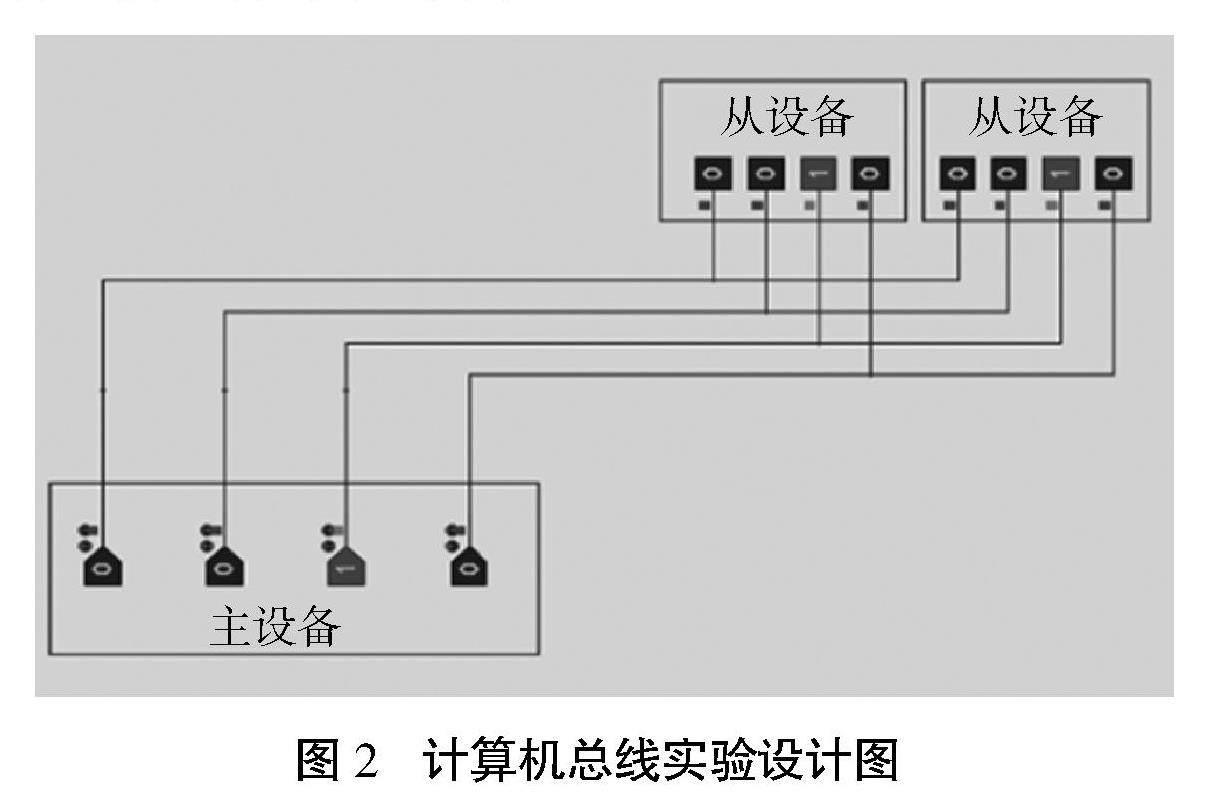

计算机内部的总线本质是多根数据线并行传输数据,所以根据计算机总线的工作原理和特点,对计算机总线实验的设计如图2所示。

图2计算机总线实验设计图

在图2中,总线中线的根数代表了这条总线的宽度,表示这条总线一个时钟能够传输多少比特的二进制数据。在图2中,这条总线采用4根線,表示这条总线的宽度为4,即一次传输4比特二进制数据,通过实验,可以帮助形象地理解总线宽度的概念。

计算机总线连接了主设备和从设备,在图2中,主设备是发送部件,负责控制总线发送数据;从设备为接收部件,通过总线从主设备上接收数据。主设备的发送部件采用4个LogicState元件,LogicState元件通过鼠标可以方便切换0或1的状态。4个LogicState元件表示此主设备的发送部件一次可发送4比特二进制数据。每个从设备的接收部件采用4个LogicProbe元件,LogicProbe元件可以显示所连接线上的二进制信号0或1。用4个LogicProbe元件表示从设备的接收部件一次可接收4比特二进制数据。主设备和从设备都可以就近连到最近的总线上,而不必考虑其他设备的位置,这样采用计算机总线使计算机内部各大部件的连接线布线合理,从而展示了目前计算机采用的总线连接相对早期计算机采用的分散连接不仅连线更简单,而且扩展性更灵活。

通过鼠标可以方便地更改仿真软件中主设备发送部件中LogicState元件的状态,发送不同的二进制数据。同时可以观察到每个从设备接收部件的LogicProbe元件接收到的二进制数据完全相同,这样验证了计算机总线的特点是同一时刻只能有一个部件往总线上发送信息,而其他部件可以同时从总线上接收到相同的信息。

计算机总线实验的设计不仅形象地展现了计算机总线宽度的概念,而且展现了计算机内部总线布局的合理性,以及总线在同一时刻只能有一个部件发送信息,而其他部件同时接收到相同信息的特点。

3 计算机存储器实验设计

计算机存储器[7]的基本工作原理是根据存储单元的地址访问存储单元里的数据,即输入所要访问的存储单元的地址,就可以访问存储单元里的数据。计算机存储器的原理图如图3所示。计算机存储器由三大部分组成。首先是译码器,存储单元的地址通过地址总线输入译码器;然后译码器根据存储单元的地址,设置存储矩阵里面对应存储单元的选择线有效,从而打开对应的存储单元;最后通过读写控制总线上的读或写信号,数据通过数据总线从选中的存储单元里面读出或写入选中的存储单元。

图3 计算机存储器原理图

计算机存储器内部通过晶体管开关负责数据的进出,对计算机存储器实验的设计如图4所示。

图4计算机存储器实验设计图

在图4中,计算机存储器的译码器模块采用Proteus内置的74138模块,74138模块可以根据输入地址来设置对应的输出选择线有效。在74138模块左边地址线输入地址(如图4中74138模块左边的001)后,在74138模块右边对应的选择线(如图4中 74138模块右侧从上往下第二根线)会设置为0有效,表示选中了对应的一个存储单元。地址总线连接了LogicState元件作为地址的输入,LogicState元件通过鼠标可以方便切换0或1的状态,这样可以方便地修改输入的地址,从而可以清晰且动态地了解译码器的功能。

计算机存储器的存储矩阵模块用来存储具体的二进制数据,M×N大小的存储矩阵表示有M个存储单元,每个存储单元大小为N比特。在实验设计中,采用了M×N个LogicState元件表示存储矩阵,LogicState元件通过鼠标可以方便切换0或1的状态。每个LogicState元件表示一个存储基元,存储基元是存储器的最小存储单位,每个存储基元存储了1比特数据0或1。每个存储基元旁边放置一个电子开关,电子开关由译码器的选择线控制导通或断开。这样给译码器74138模块左边输入一个地址后(例如图4中001),译码器74138模块右边对应的一根选择线就会设置为有效,从而导通对应的一个存储单元的开关(例如图4中从上往下第二行的2个开关)。这样存储单元的数据就可以顺着导通的开关进出存储矩阵,从而实现按存储单元的地址訪问存储单元的数据(例如图4中第二行的存储单元所存储的数据0和1)。图4中为了避免实验设计过于复杂,所以演示了4×2大小的存储矩阵的具体结构,这样既不会设计过于繁琐,也能够展示计算机存储器按地址访问数据的工作机制。

计算机存储器的读写控制模块采用电子开关实现,为避免设计过于复杂,只演示计算机存储器的读出数据功能。读写控制总线连接了LogicState元件作为读信号的输入,LogicState元件通过鼠标可以方便切换0或1的状态,这样可以方便地展示读信号控制电子开关的导通或断开。当输入的读信号有效时,存储矩阵中读出的数据(例如图4中第二行存储单元里的数据0和1)通过电子开关读出到存储器外部的数据总线。存储器外部的数据总线采用LogicProbe元件,LogicProbe元件可以显示所连接线上的二进制信号0或1,从而可以验证读出的数据正确与否。

通过计算机存储器外部的地址总线输入所要访问的存储单元的地址,然后通过计算机存储器外部的读写控制总线设置读信号有效,则对应存储单元的二进制数据可以通过计算机存储器外部的数据总线读出。计算机存储器实验的设计不仅展示了计算机存储器内部三大组成部分的具体结构,而且演示了计算机存储器按照输入存储单元的地址,访问对应存储单元数据的工作原理。

4 计算机输入输出系统中断方式实验设计

早期计算机中,计算机输入输出系统[8]的设计是程序查询方式,这种控制方式下,CPU首先会执行查询程序不间断地查询外部输入输出设备的状态,来确定外部设备是否已经准备好了数据。当查询到外部设备已经准备好了数据,则CPU再执行传输程序,与外部设备之间进行数据传输。这种控制方式会占用CPU过多时间用于外部设备状态的查询,目前计算机已经很少使用。目前计算机输入输出系统的主要工作方式是中断方式[9],这种控制方式下,CPU不用执行查询程序去查询外部输入输出设备的数据是否已经准备好,而是执行自己的其他主程序。外部设备则可以异步地按照自己的速度准备好数据。外部设备将数据准备好之后,外部设备再向CPU发送一个中断信号,CPU接收到中断之后会自动中断当前正在执行的其他主程序,并自动跳转执行中断服务程序,在中断服务程序中与外部设备之间进行数据传输。这种方式在外部设备数据准备阶段无须占用CPU的时间,只需要在数据传输阶段才占用CPU的少量时间用于执行数据的传输,所以可以大大提高CPU的工作效率。计算机输入输出系统的中断机制的工作过程也是计算机组成原理中较难掌握的重点知识点之一,相关的实验设计也更加复杂。计算机输入输出系统的中断机制的原理图如图5所示。

图5 计算机输入输出系统中断方式原理图

计算机输入输出系统的中断机制是外部设备准备好数据后,向CPU发送一个中断信号,CPU接到中断信号之后,执行中断服务程序进行数据的传输。计算机输入输出系统的中断方式的实验设计如图6所示。

如图6所示,实验设计采用了Proteus内置的51单片机模块。51单片机模块包含了计算机输入输出系统中的输入输出接口P1和P2。输入输出接口P1连接LogicState元件,LogicState元件通过鼠标可以方便切换0或1的状态,用于模拟外部设备输入数据。输入输出接口P2连接LogicProbe元件,LogicProbe元件可以显示所连接线上的二进制信号0或1,用于模拟向外部设备输出数据。通过这样的设计,有助于了解输入输出接口和输入输出设备等概念。

图6 计算机输入输出系统中断方式实验设计图

51单片机模块还包含了中断接口INT0。中断接口INT0连接到LogicState元件,通过鼠标可以方便地更改LogicState元件的信号,用于模拟向中断接口INT0发送中断信号,这样可以直观地了解中断接口、中断信号线、中断信号等概念。

当51单片机的中断接口INT0的中断线有中断信号产生时(即产生0到1的信号跳变),则51单片机的CPU接收到中断信号,CPU会自动中断当前正在执行的主程序,而跳转到51单片机的内存地址3执行其中的中断处理程序。而在中断处理程序中,CPU就可以通过读写指令读写输入输出接口,进而读写外部设备的数据。中断处理程序的代码如下所示,通过仿真软件预先放置在内存地址3开始的存储空间中。

中断服务程序。

a) ORG 0003H // 中断服务程序位于内存地址3

b) mov a,p1 // 外设接口P1的数据读入到内存a

c) mov p2,a // 内存a的数据写出到外设接口P2

d) reti // 中断服务程序返回到主程序

其中代码a)表示中断服务程序位于内存地址3开始的内存单元中;代码b)表示通过输入输出接口P1读取外部设备1的数据到内存单元a;代码c)表示通过输入输出接口P2将内存单元a的数据再写出到外部设备2;代码d)表示CPU完成与外部设备之间的数据传输之后,返回到主程序的断点处继续执行主程序。这样通过更改中断接口INT0的LogicState元件的信号,向中断接口INT0发送中断信号,51单片机的CPU将会自动跳转到内存地址3执行其中的中断处理程序,将数据从输入设备1读入,再写出到输出设备2,展示了计算机输入输出系统中断机制的一个完整工作过程。

计算机输入输出系统的中断机制实验设计不仅展示了输入输出系统中的输入输出设备、输入输出接口、中断接口和中断处理程序,还完整地演示了计算机输入输出系统的中断机制的工作过程。

5 结束语

本文研究了基于Proteus仿真软件进行计算机组成原理各大模块的实验设计。其中通过总线的布线布局展现了计算机总线的概念和特点,通过译码器74138模块展示了计算机存储部件按地址访问数据的工作机制,通过51单片机模块展示了计算机输入输出系统的中断机制的工作原理。

在上述的实验设计基础上,还有更多的改进方向,例如使用有向电子开关来展示计算机存储器读出和写入过程的异同之处,采用逻辑门来实现计算机运算器的工作原理,采用组合邏辑设计方法来演示计算机控制器根据程序指令发送控制信号的工作过程等,以上这些实验设计可在将来的工作中进一步进行研究和完善。

参考文献:

[1] 唐朔飞.计算机组成原理[M].3版.北京:高等教育出版社,2020.

[2] 张磊,何杰,齐悦,等.工程认证背景下计算机组成原理课程设计改革[J].实验技术与管理,2021,38(4):179-185.

[3] 孙卫真,刘雪松,朱威浦,等.基于RISC-V的计算机系统综合实验设计[J].计算机工程与设计,2021,42(4):1159-1165.

[4] 李黎,杨爽,苏玉萍.虚实结合的计算机组成原理实验教学体系构建[J].计算机教育,2023(6):184-188.

[5] 陈庆明,廖鸿飞,梁奇峰,等.基于Proteus的Boost电路控制仿真分析[J].电子技术,2023,52(6):19-23.

[6] 万岳.一种基于虚拟仪器的军用计算机总线仿真技术[J].计算机与数字工程,2021,49(11):2402-2406.

[7] 吕岩.一种低成本高可靠的星载计算机存储器容错方法[J].空间控制技术与应用,2020,46(3):66-71.

[8] 许耀华,朱成龙,王翊,等.基于神经网络的高并行大规模MIMO信号检测算法[J].系统工程与电子技术,2022,44(12):3843-3849.

[9] 尚任.《单片机原理及应用》智慧课堂的实践探索——以“AT89S51单片机的中断系统”讲解为例[J].吉林化工学院学报,2022,39(6):71-76.