基于PCIe DMA 缓冲池的流量控制协议

2024-04-16黄双双郝一太罗伟杰

黄双双,郝一太,罗伟杰

(中国航空工业集团公司西安航空计算技术研究所,陕西 西安 710068)

1 研究背景

1.1 相关技术

随着航空电子的发展,高速串行总线凭借高吞吐量和低时延优势,广泛应用于嵌入式计算机通信,如PCIe、以太网及RapidIO 等[1-4]。PCIe 具备高速传输速率,技术门槛和设计成本较低,已成为一种主要的嵌入式设备通信方案。

PCIe 总线技术是由英特尔提出的第3 代高性能输入/输出(Input/Output,I/O)总线技术,一般包含根组件(Root Complex,RC)、交换器(Switch)及终端设备(EndPoint)等。RC 在总线架构中唯一,用于处理器、内存子系统与I/O 设备之间的连接。PCIe 总线使用桥扩展通信网络,使PCIe 主设备能够与多个从设备同时通信。PCIe 总线通信方式分为可编程输入输出(Programmable I/O,PIO)和直接存储器存取(Direct Memory Access,DMA)[5]。针对大规模PCIe 数据传输,与PIO 相比,DMA 能够降低对中央处理器(Central Processing Unit,CPU)资源的占用率,因此被大部分PCIe 通信策略所采用。

1.2 问题描述

在航空领域中,飞行数据记录必不可少。机载计算机具备飞行数据记录功能模块,在工作状态下通常会接收模块外的PCIe 数据,并将接收数据存储到电子盘中,最终在地面状态卸载数据。PCIe 数据的接收和存储使用PCIe DMA 方式,能够快速传输数据。PCIe 数据的存储并不是直接将数据写入电子盘,而是借助文件系统将外部总线数据组织成结构规整且便于分析查看的结构进行存储。这会导致存盘速率低于接收速率,在存盘还未结束的情况下,PCIe 映射空间的数据就被覆盖,造成飞行数据存储混乱。嵌入式领域经常出现此类设备接收速率高于处理发送的速率,造成数据丢失问题。文章提出一种基于PCIe DMA 缓冲池的流量控制协议,以解决数据丢失问题。

2 方案设计

文章设计了一种基于PCIe DMA 缓冲池的流量控制协议,以控制模块间的通信流量,如图1 所示。首先,利用多级缓冲技术,在节点中配置环形缓冲池,将数据转发过程拆分为数据缓冲与发送2 个过程[6]。其次,利用节点空闲存储空间形成环形链式缓冲池,可回收利用总线空间。最后,利用同步互斥技术,为高速数据转发争取时间,保证多节点PCIe 总线数据转发存储的实时性和完整性[7]。

图1 缓冲池使用步骤

在嵌入式场景中,部署基于PCIe DMA 缓冲池的流量控制协议时,开发人员需要在中央处理器(Central Processing Unit,CPU)的设备空间中申请缓冲池,限制PCIe 节点的通信空间。然后,在缓冲池中建立若干个缓冲区,将首位相连形成环形缓冲区,简化通信的使用与回收操作。在节点通信过程中,利用同步互斥技术使环形缓冲区完成双阶段的PCIe 数据转发,主要涉及缓冲区的分配和释放。缓冲区的分配用于将总线数据缓冲到指定缓冲区。缓冲区的释放用于及时回收可利用的缓冲区。

2.1 缓冲池申请

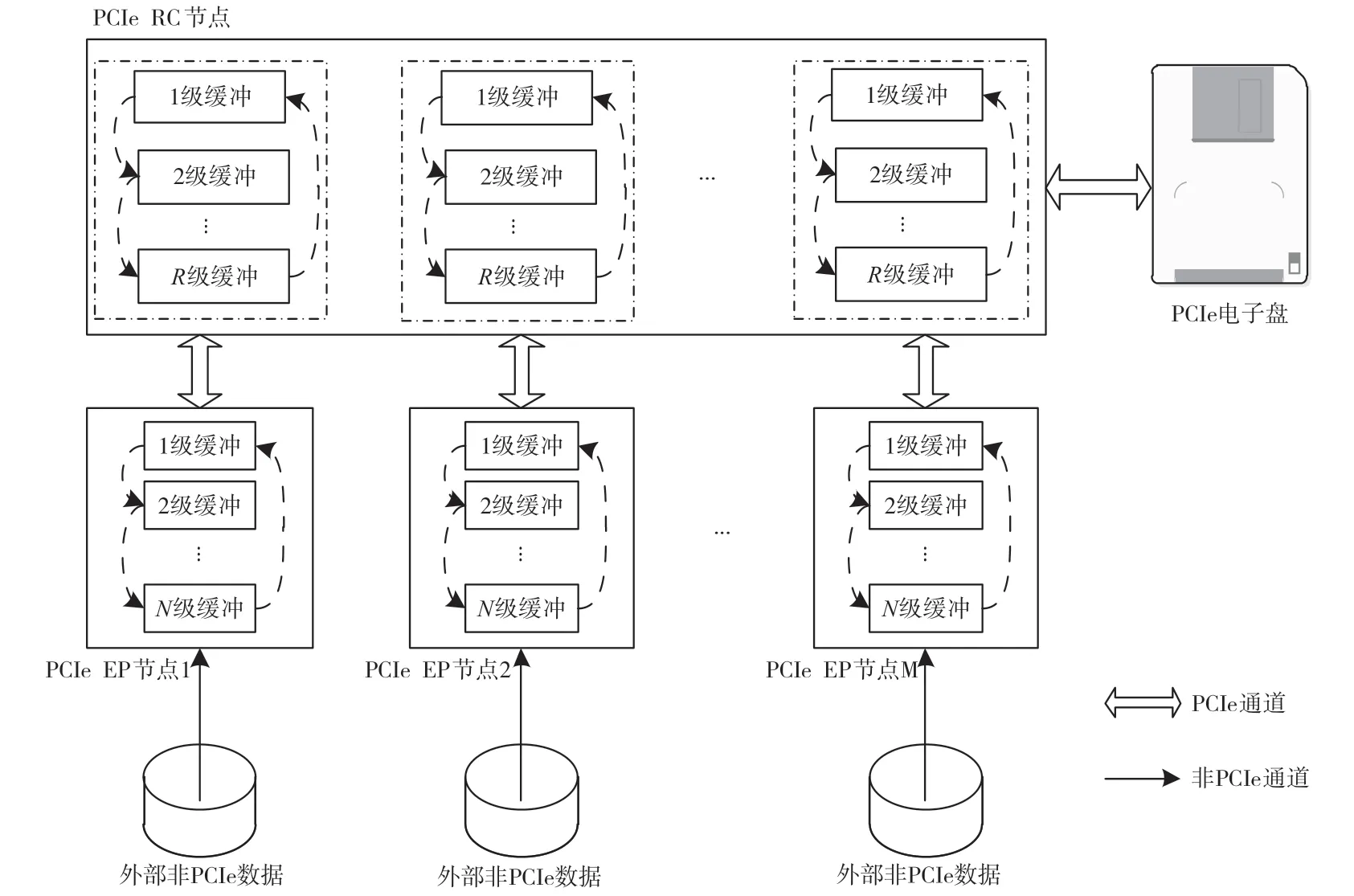

PCIe EP 节点中的缓冲池用于存储外部非PCIe 数据,RC 节点的缓冲池用于存储PCIe 总线数据。基于PCIe DMA 缓冲池的流量控制协议架构如图2 所示。

图2 基于PCIe DMA 缓冲池的流量控制协议架构

外部非PCIe 节点与PCIe EP 节点、PCIe EP 节点与PCIe RC 节点、PCIe RC 节点与电子盘之间均有通信关系。3 个节点通信时,PCIe EP 节点接收使用外部非PCIe 协议,发送使用PCIe 协议。PCIe RC 节点接收和发送使用PCIe 协议,但在发送时,PCIe 协议之上有文件系统,造成PCIe EP 节点和PCIe RC 节点接收和发送速率不匹配。因此,基于PCIe DMA缓冲池的流量控制协议需要在PCIe EP 节点和PCIe RC 节点中使用缓冲策略,平衡PCIe EP 节点和PCIe RC 节点的收发速率,以达到数据完整且传输正确的目的。

在PCIe 主从设备初始化时,基于PCIe DMA 缓冲池的流量控制协议分别在PCIe 设备空间申请缓冲池。为保证数据的连续性,每个PCIe 从设备对应一个缓冲池,缓冲池初始状态为空。要求明确PCIe 主设备节点(RC)和从设备节点(EP),并配置不同大小的缓冲池。根据图2,主设备为Drc,从设备为Diep(0≤i≤M),分别在Drc和Diep中设置环形缓冲区,用于缓存接收的PCIe 总线数据和非PCIe 总线数据。针对接收非PCIe 数据的Diep,在存储空间中开辟R个大小为Sep的缓冲区;针对接收PCIe 数据的Drc,在其存储空间内开辟N个大小为Src的缓冲区,Drc缓冲池个数为M。

2.2 环形缓冲区创建

PCIe 设备完成缓冲池的申请后,根据当前设备硬件条件与产品需求在缓冲池中创建环形缓冲区,便于总线数据缓存与空间回收。缓冲区的大小限制为Src≥Sep。根据CPU 总线数据转发的性能需求设定缓冲区的级数。环形缓冲区的大小不能超过缓冲池。环形缓冲区通过指针将若干缓冲区首尾相连,形成环形结构。缓冲区使用区满属性标识当前缓冲区是否被占用。使用环形缓冲区的根本原理是用CPU 物理空间换取处理时间,即使缓冲区大小和级数增多,也不会造成CPU暂缓处理任务数据丢失。由于经济成本限制,设计人员需要考虑性能和成本之间的平衡,使用软件手段优化当前硬件条件下的系统性能。

2.3 双阶段PCIe 流量控制

双阶段PCIe 流量控制是将PCIe 通信分为缓存和发送,主要涉及非PCIe 节点、PCIe 从设备节点及PCIe 主设备节点。PCIe 从设备节点作为中间节点,将非PCIe 节点中的数据转发至PCIe 主设备节点。在由这3 种设备组成的网络结构中,当非PCIe 节点需要将数据传送给PCIe 从设备时,采用中断方式触发DMA 机制,传输数据至PCIe 从设备映射空间。在中断处理过程中,PCIe 从设备申请缓冲区,环形缓冲区头指针指向被分配的缓冲区,将该缓冲区分配给传入的非PCIe 数据,并将该缓冲区的属性标识为区满,环形缓冲区头指针后移至与当前缓冲区相连的下一缓冲区。PCIe 从设备节点通过扫描缓冲池中的缓冲区区满属性,启用DMA 方式发送PCIe 数据,发送完成后清除区满属性,并将PCIe 主设备节点的映射缓冲区标识为区满。PCIe 主设备节点通过扫描缓冲池中的缓冲区区满属性,启用DMA 方式将总线数据发送并存储至电子盘,存储完成后清除区满属性。双阶段的流量控制策略是将接收数据、处理数据和发送数据3 类任务进行架构级和任务级隔离,便于开发人员对代码解耦,使架构清晰,简化开发流程。

2.4 缓冲区回收

在PCIe 通信网络转发数据过程中:当PCIe 从设备将总线数据传输至主设备时,释放PCIe 从设备中的当前缓冲区,清除区满标志;当PCIe 主设备将总线数据转发存储至电子盘时,释放PCIe 主设备中的当前缓冲区,清除区满标志。区满标识当前缓冲区不可被申请,但当前缓冲区的数据可被发送。清除区满标识后,当前缓冲区可被申请用于缓存,但当前缓冲区中数据为空或者已被转发,禁止发送操作。缓冲区回收旨在及时清空闲置缓冲区,保证环形缓冲区始终有可用缓冲区来缓存当前的接收数据,实现对有限存储空间的重复利用。

3 结 论

针对多个节点设备通信时入向流量和出向流量速率不匹配造成的飞行数据缺失问题,基于PCIe DMA 缓冲池的流量控制协议,利用多级缓冲和同步互斥技术控制通信流量,在确保数据完整性的同时,提高通信效率,优化当前硬件配置下的产品效能。此外,基于PCIe DMA 缓冲池的流量控制协议具备跨平台、伸缩性强等特点,稍作适应性修改即可应用于其他总线通信的流量控制,以降低开发成本,提高产品的经济效益。