低功耗时钟门控电路设计研究

2024-04-07王子鑫

王子鑫

(格兰菲智能科技有限公司,上海 201203)

0 引 言

随着电子技术的飞速发展,电子设备的能效要求日益提高,尤其是在便携式和嵌入式系统领域。功耗管理电路在管理和供应电子系统所需电能中至关重要[1]。在低功耗系统或需要优化能源利用的情景下,时钟门控可用于控制电路中时钟的开关。这一技术可在需要时启动时钟以执行任务,并在任务完成后关闭时钟,实现能量节约[2]。例如,智能手机可使用时钟门控触发特定功能的运行。用户需要时,时钟门控可为相关电路提供时钟,以实现对应功能。一旦用户退出或不再需要该功能,时钟门控则关闭对应时钟,节省电量。然而,时钟门控电路会造成一定的能量损耗。虽然目前的技术在一定限度上降低了时钟门控电路的功耗,但仍存在明显的优化空间。基于此,研究并设计低功耗时钟门控电路,降低电路能耗。

1 时钟门控技术

时钟门控技术在数字电路设计中广泛应用,旨在降低电路的功耗,特别是在处理器和微控制器等复杂集成电路中[3]。时钟门控技术通过控制时钟信号的开启和关闭,可以有效减少在非活动状态时的能量消耗。它通过在时钟路径上插入控制逻辑,仅在必要时才激活特定部分的时钟信号,从而减少不必要的功耗。这种方法不仅对提高便携式设备的电池续航能力至关重要,而且在大型系统中有助于降低能源成本和散热需求。随着电子产品不断向着更紧凑的尺寸、更强大的性能以及更低的能耗发展,时钟门控技术已成为该领域的核心技术。深入优化和创新时钟门控技术,对推动整个电子行业的持续发展和进步具有至关重要的作用[4]。

2 设计思路

2.1 低功耗驱动模块设计

在很多应用场景下,将电路中信号的翻转作为唤醒时钟的触发条件[5]。在时钟门控电源电路中,驱动模块的核心功能通常由“异或”门执行的“异或”运算来实现。在此过程中,一方面评估N个受门控制的触发器的输入信号和输出信号是否有所变动。一旦检测到信号变化,“异或”门便产生一个高电平的输出。另一方面,这一输出信号被送入一个拥有N个输入的“或”门,进行逻辑“或”操作。完成此环节后,合成的结果与时钟信号一同进行“与”逻辑处理,进而生成门控时钟。该门控时钟使触发器在有效数据到来时能正确传输。

研究发现,“或”门和“与”门的逻辑组合能有效替代传统“异或”门的逻辑功能。和“与或”门相比,传统“异或”门在物理空间上的占用几乎翻倍。更为关键的是,“与”门和“或”门在逻辑处理上的简洁性和能源效率方面表现出色,能够显著减少对整体电路功耗的影响。因此,针对时钟门控电路中“异或”门所带来的高能耗、过大的空间需求以及运算复杂性的问题,文章提出使用“与”门和“或”门相组合的方式来取代传统的“异或”门[6]。这种改进维持了电路逻辑的精确性,同时显著降低了功耗和面积需求,为设计低功耗电路提供了一种高效的方法。一方面,根据信号有效电平将触发器分组,引导每组中N个触发器的有效电平信号进入一个N输入的门级单元,使人们能够通过精准的门逻辑运算收集众多信号的有效电平,并将其作为随后的门控使能信号。另一方面,“门”运算处理过的输出信号被输送至一个具有双输入的“与”门,确保仅当真正需要时,时钟信号才得以通过。经过使能信号筛选后的门控时钟作用于触发器的时钟端,从而高效完成触发器的门控功能[7]。基于该设计思路,设计了2 种驱动电路,如图1 所示。

图1 设计的驱动电路

在实际应用中,不同类别的触发器组仅传输对应的有效电平信号,因此只需要判断输入端是否为有效电平即可唤醒对应触发器的时钟信号。采用第2 种驱动电路不仅能完成所需功能,而且仅需引入一个N输入的“与或”门,面积损耗低于第1 种驱动电路。在低功耗驱动模块的设计改进过程中,采用以仿真波形为基础的筛选方法。一方面,通过分析触发器输入信号的波形特征,实现触发器的有效分组。依据波形的相似性将触发器划分为不同的组,识别各组触发器共有的关键特征。例如,那些在仿真中以高电平为有效信号且大部分时间维持在低电平状态的N个触发器被归为一组,而那些低电平有效信号且大多数时间保持在高电平状态的N个触发器构成另一组。另一方面,针对第一类触发器组,该设计采用N输入“或”门,第二类触发器组则为N输入“与非”门。这一策略的关键在于通过对寄存器组的划分,可以有效使用N输入“或”门和“与非”门来替代原先每个触发器所需连接的“异或”门。这种新颖的时钟控制模块设计是为了无冗余地检测受门控制的触发器输入信号的有效变换,从而高效、精确地执行时钟门控功能。

2.2 数据保持模块设计

在深入分析改良后的驱动模块性能时,发现N输入门级单元执行完运算后直接输出结果的处理方式可能导致电路出现“毛刺”,即电平在短时间内的不稳定波动[8-10]。这不仅影响电路稳定性,而且可能导致时序错误。为解决这一问题,文章设计了一种避免门控时钟信号“毛刺”的电路模块,设计思路如下。首先,应用低电平锁存器,在时钟信号为低电平时将使能端导通到Q 端,并在时钟变为高电平后锁住Q 端的值作为时钟的筛选信号;其次,选择锁存器作为保持模块的核心组件,确保使能信号的输出在时钟信号为高电平时始终保持稳定,从而避免“毛刺”现象;最后,利用后级的“与”门完成时钟高电平的筛选生成门控时钟,确保生成时钟信号的功能正确性和完整性。这个结合体构成了数据保持模块,用于进行时序保护和时钟信号的筛选。数据保持模块设计如图2 所示。

图2 数据保持模块

基于文章的设计思路,首先电路对同一组中的N个触发器的输入信号执行“与非/或”逻辑运算,其次将这一运算的输出信号作为使能信号传输至数据保持模块,最后利用数据保持模块输出门控时钟并连接到触发器的时钟端,实现其预定功能。

3 仿真结果及分析

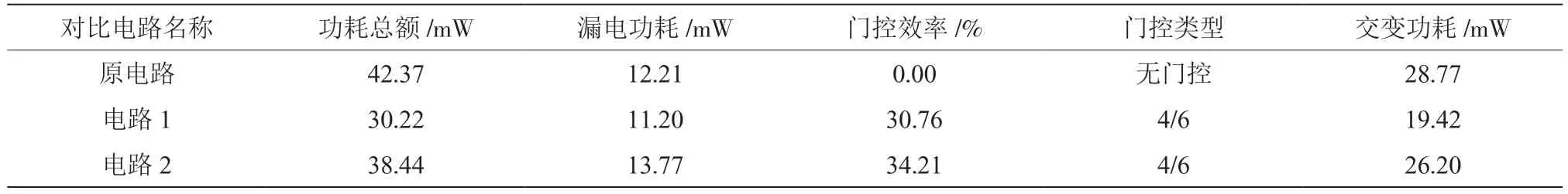

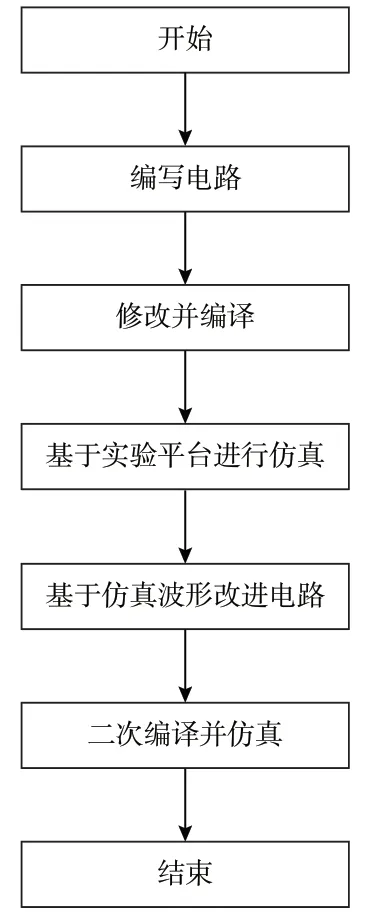

文章制定的仿真流程如图3 所示。选择的测试电路为ISCAS 89,由于其功能不固定,被广泛应用于各类电路测试任务。此外,文章采用Verilog HDL 搭建测试平台,设定加入文章所提出的新型时钟门控技术改进的电源电路为电路1,采用传统时钟门控技术进行优化的电源电路为电路2,仿真对比结果如表1所示。

表1 仿真对比结果

图3 仿真流程

由表1 可知,电路1 在降低能耗方面的效果更加显著,在减少功耗方面的性能优越。

4 结 论

文章围绕电源管理中的关键挑战,即降低电子设备时钟门控电路的功耗,设计了一种新型的低功耗时钟门控电路,为电源管理和节能技术的发展提供一定的帮助。通过开展本研究,填补现有技术的不足,从而推动时钟门控电路设计朝着更高效和更低功耗的方向前进。