异质栅介质双栅隧穿场效应晶体管TCAD仿真研究

2024-03-07谭淏升

谭淏升

(上海电力大学 电子与信息工程学院, 上海 200090)

随着集成电路技术的飞速发展,芯片所包含的晶体管数量逐渐增多,传统金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transistor,MOSFET)的功耗面临极限。由于存在短沟道效应,受限于关态电压下亚阈值泄漏电流和室温下亚阈值摆幅的理论极限值,传统MOSFET在某些场景下不再适用[1-2]。为了替代MOSFET,隧穿场效应晶体管(Tunnel FET,TFET)因其具有低功耗和陡峭的亚阈值摆幅等特性而备受研究人员关注。TFET的工作原理与传统MOSFET不同,其导通是基于载流子的带带隧穿(Band to Band Tunneling,BTBT)过程,因此能够实现更低的亚阈值摆幅[3]。但TFET自身也存在局限性,如开态电流较低、双极性导通等,阻碍了TFET在电路中的应用[4]。针对上述缺陷,研究人员提出了很多解决方案。例如:在改善电流方面,采用多材料栅[5-7]、采取不同厚度的源漏区[8-11],以及采用新型材料等,将开态电流提升了多个数量级,但仍未能满足现实需求;在抑制双极性方面,采用源漏区与栅极重叠或欠重叠的器件结构[12-14],以及非对称沟道,改变交界面的隧穿情况[15],使得双极性电流降低到pA (10~12 A)和fA (10~15 A)量级。尽管上述方法改善了TFET器件的开态电流并抑制其双极性特性,但同时使得器件的成本和工艺复杂程度有所增加,如重叠和欠重叠等技术改变了器件的基本结构,难以与以往工艺技术相匹配,从而降低器件的可拓展性。

本文在双栅隧穿场效应晶体管(Double-Gate Tunnel FET,DGTFET)的基础上,结合成本、与以往工艺技术匹配度,以及工艺复杂程度等多方面因素来优化器件。在保证晶体管基本结构仍与以往器件相似的前提下,融合多种结构的优良特性,将源区材料替换为窄禁带半导体材料,栅氧化层采用异质栅介质结构,同时将不对称掺杂和高k介质Pocket区整合运用到DGTFET上。异质栅介质可以在提升器件开态电流的同时降低双极性电流。仅在漏端添加高k介质Pocket区,可以改善栅漏交界面的隧穿宽度,有益于提升器件对于双极性的抗性,源端正常导通,故不需要此结构。采用TCAD软件进行仿真实验,对比分析传统器件以及有无异质栅介质和高k介质Pocket区的DGTFET,研究栅介质的介电常数、长度、Pocket区厚度等参数对DGTFET直流特性、亚阈值摆幅和双极性电流的影响。

1 器件结构和仿真模型

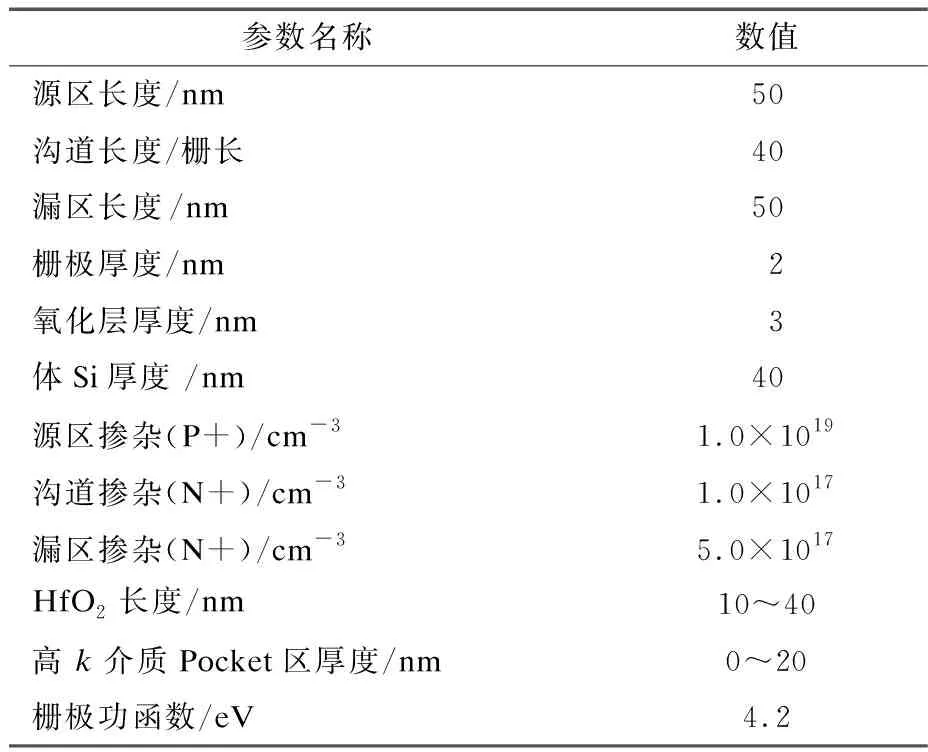

本文仿真实验采用的DGTFET器件结构如图1所示。其详细参数如表1所示。

表1 器件仿真结构参数

图1 仿真实验的DGTFET器件结构

利用Sentaurus TCAD进行器件的建模仿真。由于隧穿过程是非局部的,因此采用非局部带带隧穿模型、非局域隧穿模型和Fermi-Dirac统计模型,电子隧穿路径在模型内设置为非局部。由于高掺杂浓度会对材料的禁带宽度等参数产生影响,因此引入禁带变窄模型,以及与掺杂浓度和电场有关的迁移率模型等。

重掺杂所导致的深能级杂质和缺陷会产生间接复合,对载流子的寿命和器件的性能影响较大,因此本文引入了俄歇复合模型和载流子重组模型SRH(Shockley-Read-Hall)。

2 转移特性

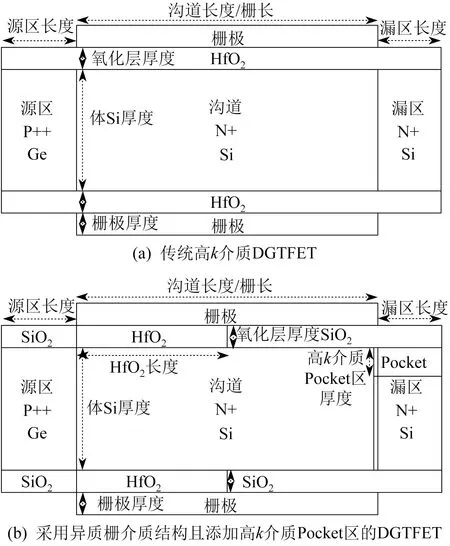

选取栅氧化层下方1 nm处为观测点,漏极电压Uds=0.5 V,栅极电压Ugs=1.5 V,传统以Si为材料源的DGTFET和将源区材料替换为Ge的TFET的开态能带图如图2所示。

图2 不同源区材料开态能带图

由图2可以看出,在器件处于导通条件时,沟道区的能带由于栅极施加正电压从而被拉低。源区价带的电子可以通过较小的隧穿距离到达沟道的导带,以Ge为源区材料的隧穿宽度更窄,在同等栅极电压条件下,电子发生隧穿的可能性更大,将会有更多的电子到达导带,由此产生更大的开态电流。因此,隧穿距离的大小可直接影响到器件开态电流的大小。本文选用Ge作为源区材料与沟道形成异质结。

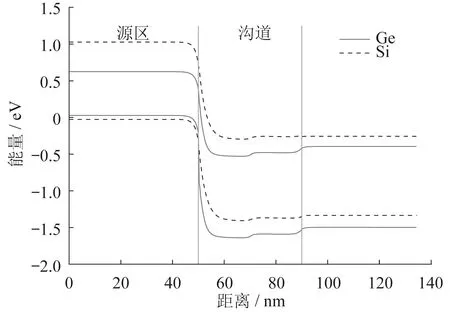

不同栅氧化层材料的介电常数不同,器件的开态/关态电流等特性参数也不相同。选取的3种栅氧化层材料分别为:SiO2,介电常数k=3.9;Si3N4,k=11.8;HfO2,k=25。3种材料所构成器件的开态/关态能带图及转移特性曲线如图3所示。图3(a)中,Uds=0.5 V,Ugs=1.4 V;图3(b)中,Uds=0.5 V,Ugs=1.5 V;图3(c)中,Uds=0.5 V,Ugs=-2.0~1.4 V,Ids为源漏电流。

图3 不同介质开/关态能带图及转移特性曲线

由图3可以看出,由于施加栅极电压的不同,所以沟道能带会整体上下移动,并与源区或漏区形成比较窄的隧穿势垒,更有利于价带电子隧穿到导带而形成更大的电流。栅氧化层材料为HfO2的器件在负栅极电压下的隧穿宽度明显比栅氧化层材料为SiO2的隧穿宽度要小,表明同等电压条件下,采用高k介质做氧化层材料的器件所形成的双极性电流更大,但同时高k介质提升了栅极与源区之间的耦合,增大了器件的开态电流。

图3(c)中的转移特性曲线与上述结果相符,与常规材料SiO2相比,氧化层采用高k介质材料能进一步提高DGTFET的源漏电流,改善器件的导通特性,同时增大器件的双极性电流,降低器件对于双极性的抗性。氧化层为SiO2时器件的开态电流为3.11×10-7A/μm,氧化层为HfO2时提升到了5.17×10-5A/μm,器件的双极性电流从1.0×10-14A/μm提高到了1.0×10-11A/μm,提高了3个数量级。

亚阈值摆幅是表征器件栅控能力强弱的重要参数。其值越小,栅极电压的微小变化就会使电流发生明显变化,器件便能在更低的电压状态下工作。其平均亚阈值斜率Sk为

(1)

式中:UTH——器件的阈值电压;

Uoff——器件最小漏电流所对应的栅极电压;

ITH——对应阈值电压下的电流;

Ioff——器件最小漏电流。

根据图3(c)中的实验数据可得出,SiO2为栅氧化层材料的DGTFET平均亚阈值摆幅(取电流为1.0×10-7A/μm时的对应电压为阈值电压)为131 mV/dec,HfO2对应器件的平均亚阈值摆幅为57.84 mV/dec。由此可见,采用高k介质可以优化器件的亚阈值摆幅。

本文结合各种材料的优点,采用异质栅介质结构,在靠近源区即正向传输发生隧穿的异质结附近采用高k介质,在靠近漏区采用低k介质,以降低栅极与漏极的耦合作用,从而在保证器件开态电流不发生明显变化的前提下,尽可能地降低双极性电流,改善器件的双极性特性。

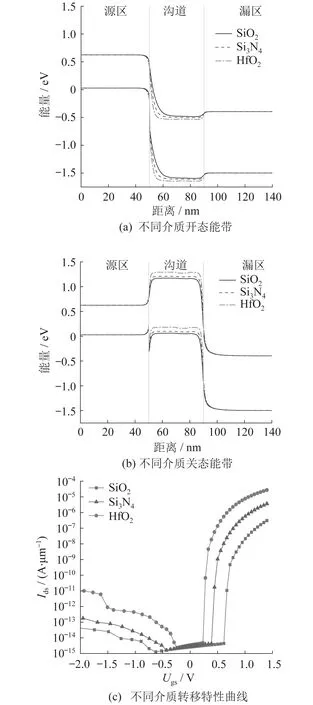

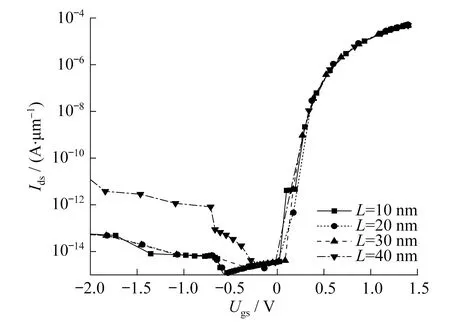

高k介质的长度L分别取10 nm,20 nm,30 nm,40 nm时,对应器件的转移特性曲线如图4所示。其中,Uds=0.5 V。

图4 不同长度L的高k介质对应器件转移特性曲线

由图4可以看出,由于采用异质栅介质结构,综合了低k介质和高k介质的优点,且在高k介质HfO2的不同长度下,器件的源漏电流并未发生明显变化,此时,器件的亚阈值摆幅为28.3 mV/dec。因此,从特性角度来说,高k介质的长度对于正负栅压下器件的影响并不明显。器件发生隧穿的位置在沟道和源区的交界处,并未扩展到沟道内部。当HfO2的长度L=40 nm时,器件的双极性电流突然增大,这是因为此时器件沟道上方氧化层全为HfO2,负栅压下隧穿主要发生于沟道和漏区的交界处,与源区采用高k介质同理,双极性电流也会增大。因此,器件对于介质的介电常数k较为敏感,而对于异质栅介质的长度L(小于沟道长度时)变化并不敏感。

3 双极性

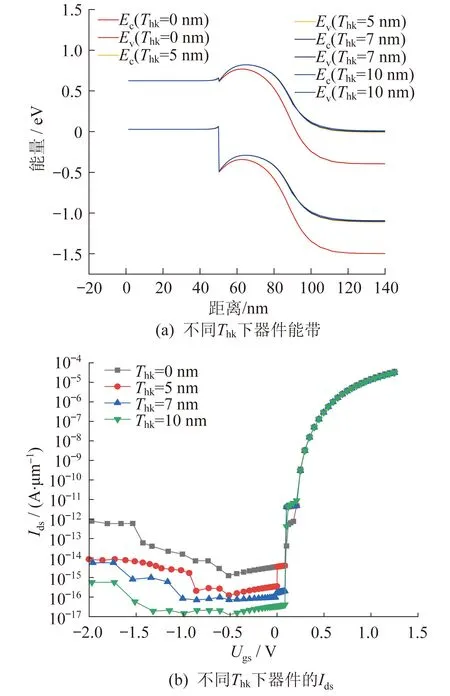

TFET产生双极性电流的本质原因是,在负栅压情况下,沟道区与漏区交界面处隧穿宽度减小,使得电子隧穿概率增大。因此,要提升器件的双极性抗性,就要扩大负栅压下TFET沟道区和漏区交界面处的隧穿宽度,在漏区加入高k介质Pocket区。对于如图1(b)所示的器件结构,Pocket区宽度设为40 nm,厚度Thk选取0 nm,5 nm,7 nm,10 nm,对应器件在负栅压下的能带图和转移特性曲线如图5所示。

图5 不同Thk对应器件在负栅压下的能带图和转移特性曲线

图5(a) 中,Ec和Ev分别表示导带和价带,Uds=0.5 V,Ugs=-2.0 V;图5(b)中,Uds=0.5 V,负栅压下的源漏电流Ids即为器件的双极性电流Iamb。

根据图5可以得出,在负栅压下,加入高k介质Pocket区的器件沟道和漏区交界处的隧穿势垒增大,电子隧穿产生率降低,从而使得电子隧穿更加困难,双极性电流也会降低,即器件承受的负栅压会进一步增大。未包含Pocket区的器件在-0.5 V左右,双极性电流开始急剧增大,而对于加入Pocket区的器件,其Thk的数值越大,双极性电流就越小,且电流急剧增大的电压起始点也在不断后移。当Thk=10 nm时,器件的双极性电流最低,约为1.0×10-17A/μm。

此外,由于高k介质Pocket区的主要作用区域为漏区,用于抑制双极性导通,对于正常导通并不会产生明显影响,因此添加Pocket区结构的器件与无此结构器件的转移特性在正常导通时表现相近。由图5(b)也可以看出,当栅极电压为正时,源漏电流曲线几乎重合。由此得出,随着Pocket区厚度的增大,器件的双极性导通效应逐渐减弱,双极性电流进一步降低,但器件的正常导通等方面未受到明显影响。

4 结 语

本文基于双栅隧穿场效应晶体管,提出了一种结合异质结、异质栅介质和高k介质Pocket区结构的DGTFET。与传统DGTFET相比,器件的开态电流得到了优化,并且器件的亚阈值摆幅缩减为28.3 mV/dec,相比于其他方法,在实现可能和特性表现上做到了一定程度的平衡和改善。对影响器件特性的参数进行了分析研究,改变高k介质的长度(小于沟道长度时)对器件特性并无明显影响;漏区的高k介质Pocket区有利于提升器件抑制双极性的能力,同时对器件的开态电流等特性并无明显影响,且随着Pocket区厚度的增大,器件抑制双极性的能力逐渐加强。同时,由于器件的基本结构仍是传统结构,因而在后续工艺的实现方面,可节省不少成本。在实际应用时,应结合实际情况修改器件的相关参数,以适应不同需求。