卫星图像数据高速传输与处理系统的设计与验证*

2024-02-28耿世松

白 玉,胡 旋,耿世松

(1.沈阳航空航天大学 电子信息工程学院,沈阳 110136;2.中国科学院软件研究所,北京 100190)

0 引 言

当前传统宇航级器件的开发通常是面向特定任务的专星专用器件,这一特性决定了传统宇航级器件的开发具有硬件环境不可复用、研制成本较高且开发周期较长的弊端[1-2]。为解决上述问题,本文采用商用硬件平台,并借鉴“软件定义卫星”系统架构[3]。Xilinx公司ZYNQ系列产品提供了完美的SoC解决方案,其具有处理系统(Processing System,PS)与 可编程逻辑(Programmable Logic,PL)搭配高性能体系架构,这为星上系统的研制提供了无与伦比的灵活性与可拓展性。其中可重复编程、时序管脚可控制的 ZYNQ UltraScale+板卡采用 XCZU7EV 芯片作为控制和处理中心,其功能强大、性能高,更加有利于实现商用器件向宇航级产品的过渡。,

在目前国内外大多数星上数据传输与处理系统中,容易出现可靠性安全性不高,传输速率较低,兼容性通用性较差等问题。早期研究中,文献[4-9]有人采用以太网帧协议解决了传输丢帧问题,但传输无效数据浪费带宽。对于其中使用的数据传输协议,LVDS高速接口最高速率仅能达到100 Mb/s,TLK2711协议线速率可达到1.8 Gb/s但复杂度过高。且上述解决方案均未阐述使用商用开发平台实现高速实时且可靠通用的星上数据传输系统。针对上述问题,本文采用Xilinx发布的一款可扩展Zynq UltraScale+ MPSoC ZCU106为商用卫星开发平台,其不仅满足各项数据指标需求,同时支持星上复杂软硬件算法的快速开发与编排。本系统可用于星上设备间需要高速数据传输的场景,使用Xilinx器件更具商用价值且缩短研制周期,为目前开发商用卫星智能算法与软件的更新迭代提出新的方向。

1 星上高速系统设计

1.1 系统总体设计方案

本文采用可重复编程、时序管脚可控制的 ZYNQ UltraScale+ 作为主控器件,采用其PS与PL的异步架构以满足本系统软件开发与硬件设计相联合的需求。针对已有星上数据传输存在的不足,本文创新性地提出了一种高速实时且可靠通用的数据传输处理系统设计方案。本设计采用Xilinx开发平台,从而可配置其提供的Aurora8B/10B IP以实现线速率2.5 Gb/s的接口交换速率,此方法简单高效的实现了链路数据传输;采用自定义的帧格式对传输数据加密,添加帧头构成内帧,以保证传输的可靠性并且节约了带宽和资源;采用异步架构实现PS与PL数据互传,为ARM端各类嵌入式及软件算法的开发提供保障。最后为验证本系统具有算法的通用性及适配性,在逻辑侧以Sobel算法对图像进行实时处理。

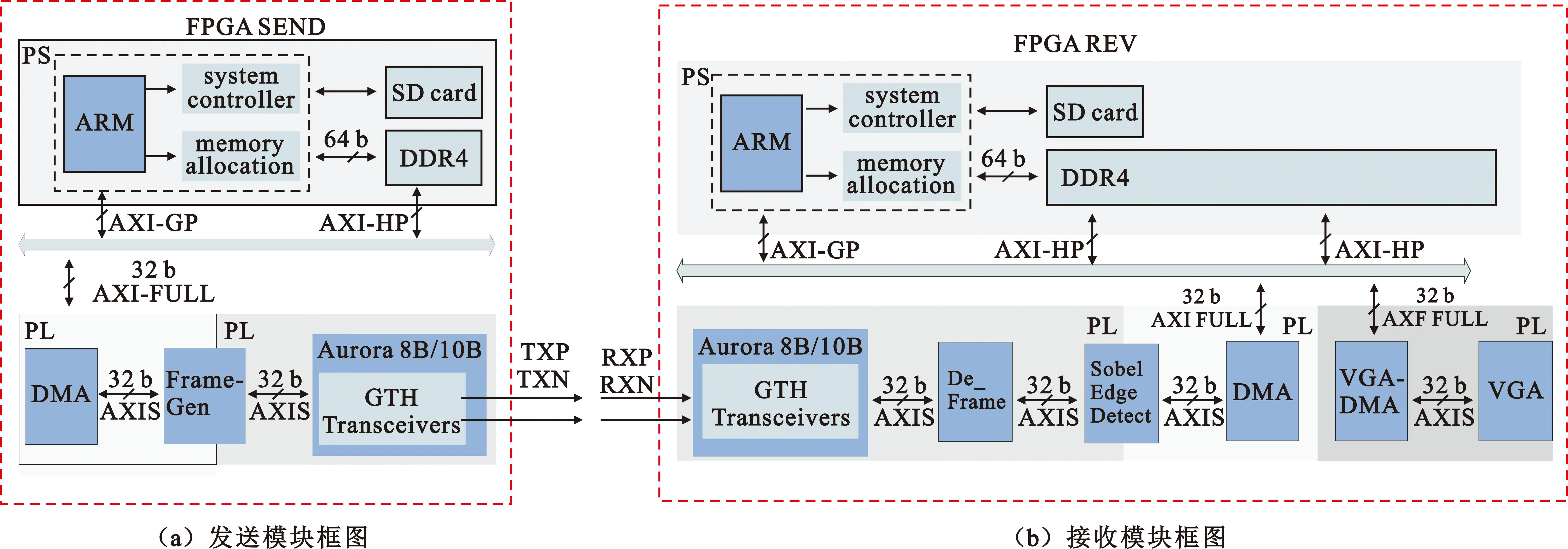

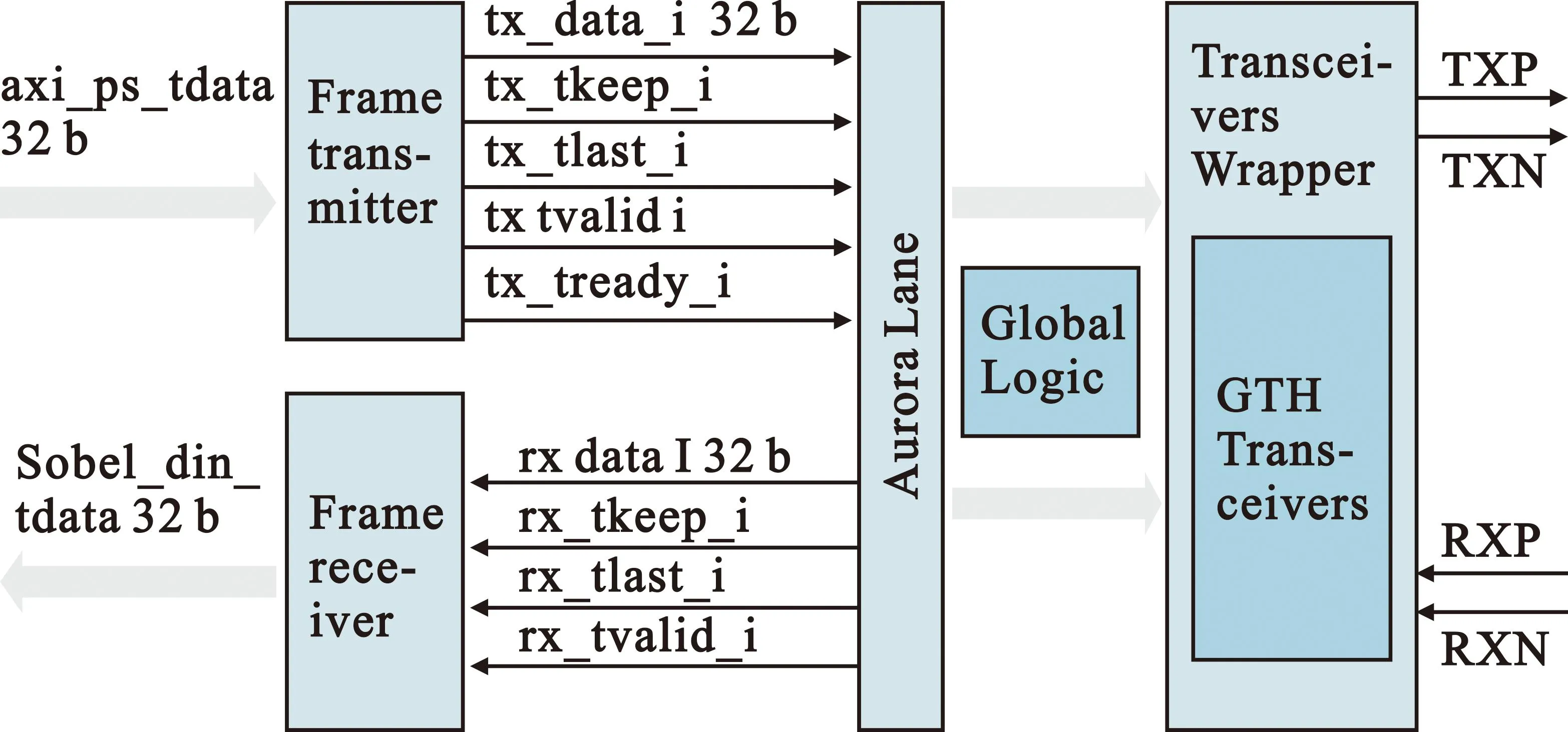

发送总体框图如图1(a)所示。大容量星上图像数据存入DDR4内存后,PL通过直接存储器(Direct Memory Access,DMA) 访问PS。传输前对数据传输链路做自定义的帧信息添加(Frame_Gen),其对图像数据加上专用帧标志,帧号,图像分辨率等信息,以保证传输的可靠性与安全性。通过GTH并采用差分SMA接口来完成数据的高速串行发送。其中采用简单高速的Aurora协议进行数据互传,以通用性较强的高速串行收发器GTH基于Aurora协议来传输数据。在进行板间接口数据传输时,采用Serdes传输机制即可从数据中恢复出时钟,以此保证时钟同步。内部各IP间数据流传输基于AXI-Stream总线实现,相比其他星上传输系统接口,其具有更高的通用性及系统适配性。

图1 卫星数据传输与处理系统总体设计框图

接收总体框图如图1(b)所示,接收端同样通过串行GTH接收数据,并将数据发送给帧头信息提取模块对帧数据进行解析。之后同样通过DMA方式将数据送入DDR4存储。为验证整个系统的通用性,本文采用优化的实时Sobel算法对卫星图像进行边缘检测。最后将其处理后的数据通过VGA接口在显示器显示以观察处理后的图像边缘。

1.2 星上系统设计关键技术

本文将星上高速系统的设计分为星上异步架构数据传输、星上链路专用帧转换、星上高速数据传输接口3个部分。

1.2.1 星上异步架构数据传输

采用软硬件联合设计的方式实现星上异步架构数据传输,此种方式为后续星上软件定义开发提供基础保证。

为实现PS与PL双方共享内存,本文创新地采用板卡的异步架构设计,两者通信的物理基础是AXI高速总线协议。采用AXI DMA并配置为简单双工模式以实现DDR4的高速读写。DDR4的系统时钟为1 067 MHz,物理接口位宽为64位,因此DDR4的理论支持的最大速度为16.66 GB/s。

本文Block Design总体框图如图2所示。此处数据互传涉及跨时钟域传输,因此读写时钟不一致会造成传输数据混乱的情况。为采用最简单的方式解决此问题,本文添加异步FIFO(AXI-Stream Data FIFO)进行不同时钟域间的数据传输与缓存。在整个系统进行实时数据传输处理过程中,AXI DMA负责读取DDR4中的图像数据,同时还要负责将接收端处理后的图像数据写入DDR4。其中PS与PL的高速数据传输主要使用AXI_HP接口和AXI_GP接口完成。AXI_HP接口与PL相连后,相互独立的读写通道经过FIFO缓存。通过DMA将数据存储在DDR4存储器,以此完成流式数据与存储器映射数据间相互转化。系统对 AXI DMA 的控制是在 PS 上实现,通过运行C代码完成DMA初始化及寄存器配置。为减少CPU的空转损耗减少星上传输延时,本文最终采用中断方式实现DMA发送和接收。

图2 Block Design示意图

1.2.2 星上链路专用帧转换

采用线性状态机设计对星上帧信息加密成自定义专用帧,以保证星上信息传输的可靠性与安全性。

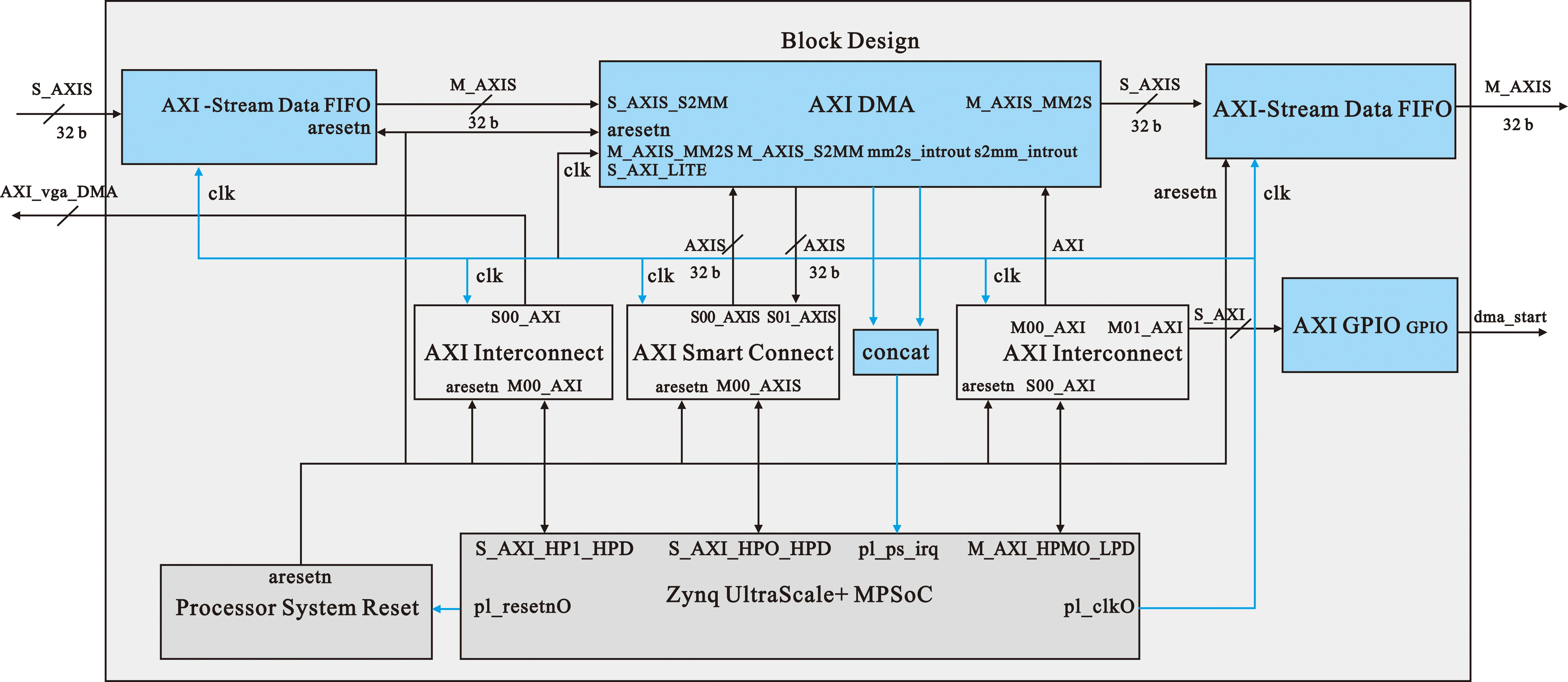

为了在进一步保证传输效率的同时提升系统的准确性与安全性。数据发送端要对接收到的PS端数据进行帧头信息的添加构成内帧,并在接收端进行帧头信息的提取以进行同步。为保证系统通用性,此节仍按照AXI-Stream协议与Aurora接口进行交互。本文采用自定义的帧信息格式并在接收端进行数据检验,以此保证系统的安全性。帧头信息自定义格式包括2 b帧标志、6 b帧号、12 b图像的行数、12 b图像的列数。发送模块帧头信息添加采用状态机实现,设计具体如图3所示。

图3 帧信息添加状态机示意图

复位系统后进入S_IDLE状态,等待一帧图像数据的到来。当检测到一帧图像数据第一拍信号有效时,进入S_ADD_HEAD状态。期间添加帧头信息,维持一个时钟周期,进入S_WRITE_DATA状态。一帧图像传输完成后进入S_FRAME_END。此种状态机实现帧信息添加方式,有效解决了复杂逻辑的实现。其既覆盖了链路所有情况出现的可能性,又保证了系统不会重复处理,极大的提高了传输的效率。

同理,解帧模块也采用状态机实现。类似封帧模块,用于帧标志、帧号、图像分辨率信息的提取,并将图像数据传输给Sobel Edge Detect模块进行后续算法处理。

1.2.3 星上高速数据传输接口

采用Aurora协议实现星上高速数据互传,以保证系统高速性和稳定性。

为了以简单的方式实现星上链路的高速数据交互,本文以GTH收发器作为物理层、Aurora协议实现链路层功能。为保证星上模块间用户数据交互的通用性及灵活性,以AXI-Stream接口来实现各模块衔接。此方式相比传统专星专用的星上链路研制,具备可配置即插即用的功能。其具有带宽高、支持全双工和单工通道、帧格式帧长度可灵活定制等特点。

由于系统要求Aurora IP核通道的线速率(Line Rate)配置为3.125 Gb/s,且协议要求时钟必须为同一bank或相邻bank的时钟,故此输入参考时钟(GT_Refclk)156.25 MHz,用户时钟(User_clk)78.125 MHz[10]。Aurora采用帧模式(framing)进行全双工数据传输,其接口模块如图4所示。

图4 Aurora与AXIS交互关系图

发送和接收数据位宽均设计为32 b(Lane Width=4 B),这样整个系统数据位宽相同,适配性灵活性很高。由于发送的数据经过RocketI/O 进行了8B/10B编码,故而通道串行线速率为3.125 Gb/s×80%=2.5 Gb/s。本节各个模块的设计均使用Aurora的输出时钟user_clk故没有进行跨时钟域处理。

2 星上图像处理算法验证

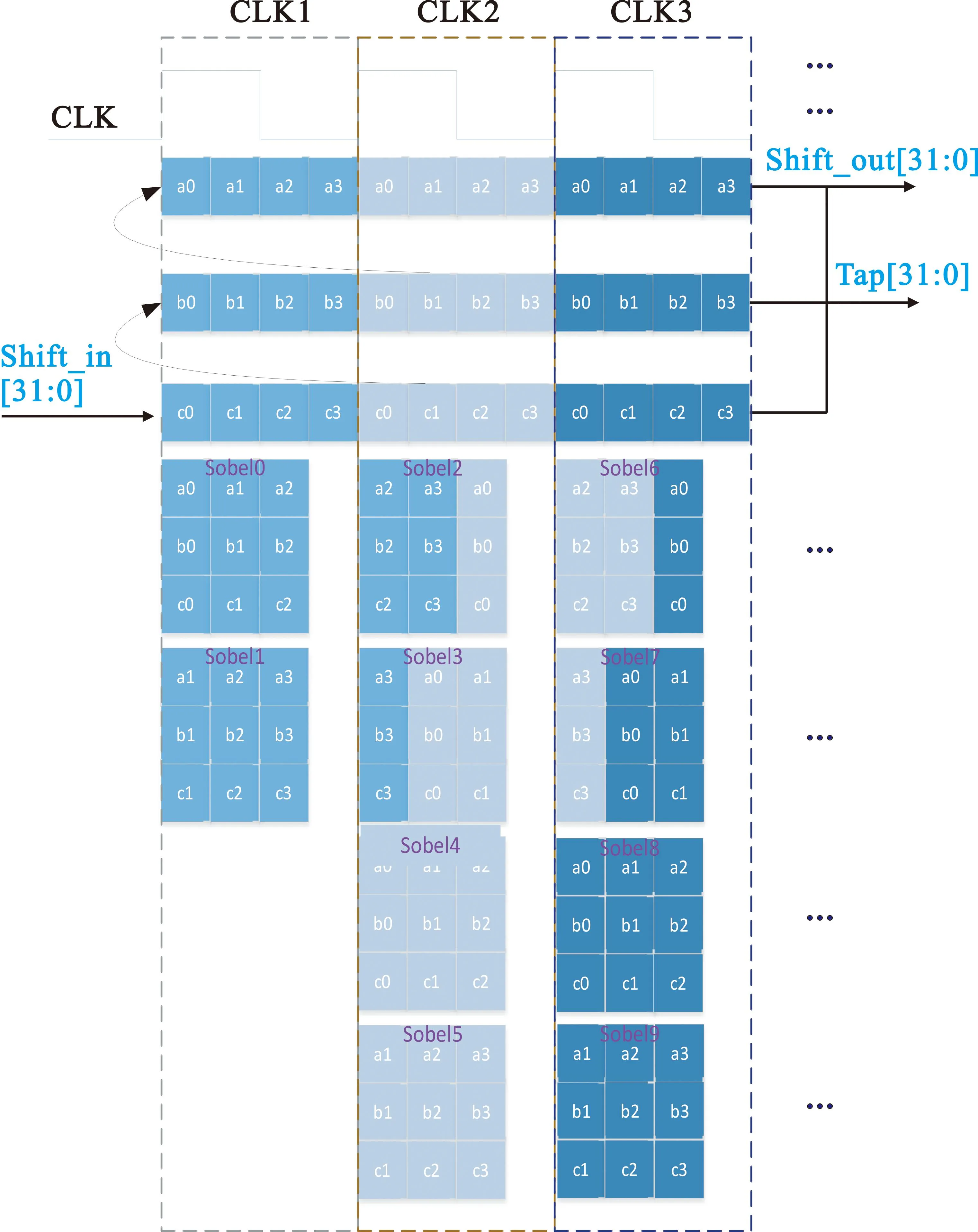

传统算法在系统上实现多为一个时钟处理单像素,而本系统传输时一个时钟传输4个像素。为解决为各类其他传统算法在本系统使用的通用性问题,采用Sobel图像边缘检测算法验证系统性能。同时,系统对于星上互传的图像数据具备实时处理能力。Sobel算法采用一阶导数实现局部平均的计算方法。其优势在于平滑去噪,提高检测精度。同时本文提出的优化Sobel处理方案,相比现有的FPGA实现Sobel算法的思路,传输延时更小,性能也更加优越。相比以往Sobel算法,本设计创新的将一个时钟输入的4个像素同时并行处理,可将系统速率提高3倍。其对后续其他复杂星上通用性实时处理算法开发具有一定的理论及现实指导意义。

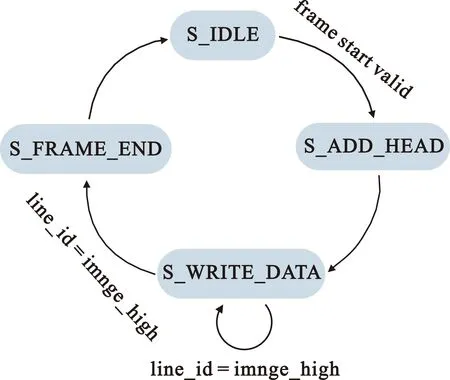

现有Sobel算法为一个时钟输入一个像素(一个像素为8 b),由于系统一个时钟输入4个像素(数据位宽32 b)。为满足实时性需求必须将时钟提高四倍,通过异步FIFO将数据位宽将为8 b处理。但此方法一个时钟只能处理一个像素,不能满足本系统高性能需求。故将32 b像素在一个时钟同时输入进行Sobel运算,算法的设计整体流程如图5所示。由于Sobel算法需要3行3列矩阵运算,故需要采用双FIFO流水线操作对两行图像数据进行缓存。本文采用FIFO Generator中的Common Clock Block RAM进行一行数据的缓存,数据读写深度设置为2 048。由于数据位宽为32 b,本文Sobel算法处理部分时钟采用user_clk=78.125 MHz。

图5 优化后的Sobel算法实现流程图

以图中Sobel1为例,把图像每3行3列的数据分别乘上算子中对应位置的值再相加,然后进行如下运算,得到Dx和Dy。

Dx=(a2-a0)+(b2-b0)×2+(c2-c0)

Dy=(a0-c0)+(a1-c1)×2+(a2-c2)

由于数据传输链路位宽32 b即一个时钟传入4个像素,因此在CLK1下需要进行Sobel1和Sobel2运算,并且将第三个和第四个像素用寄存器缓存与CLK2传入的像素进行Sobel运算。同理在后续的时钟下,每个时钟同时完成4次Sobel处理。

按照上文所述Sobel算法原理,对上面求得的Dx和Dy做平方和的平方根,再取近似值Dx和Dy的绝对值和得到Dxy。本文为对星上图像进行较准确的边缘检测,阈值设置为100。若Dxy的值大于该阈值则表示该点为边界点,就让VGA显示一个白点,否则显示黑点。于是得到了一幅卫星图像的轮廓,为满足1 080P像素显示需求,VGA接口部分模块时钟为148.5 MHz。

3 试验与分析

本文实现软件开发与硬件设计相结合的设计架构,其中Aurora高速片间传输及Sobel并行算法等PL端设计是基于Xilinx Vivado2019.1平台开发的。数据源发送与接收以及DMA配置与驱动程序是PS端基于Xilinx SDK开发的。在测试中,将1 920 pixel×1 080 pixel的8 b灰度图卫星图像数据源放入SD卡,用于进行整个系统的性能测试。采用Xilinx专用的调试工具集成比特误码率测试仪(Integrated Bit Error Ratio Tester,IBERT)及在线逻辑分析仪(Integrated Logic Analyzer,ILA)验证数据传输与处理的各项性能指标。本系统整个测试流程如下:

1)通过在PL端设计状态机实现计数逻辑并且在SDK设置计时对DMA速度进行测试,通过观测SDK界面DMA发送接收内存数据以验证数据传输准确性;

2)通过集成逻辑分析仪对Frame_Gen以及De_Frame模块信号及数据进行观测,以验证设计的准确性;

3)通过集成比特误码率测试仪对数据链路进行误码率测试;

4)通过VGA接口显示Sobel边缘检测之后的数据并和Matlab实现Sobel边缘检测的图像处理结果对比,验证结果的准确性。

3.1 PS与PL互传性能

本文DMA发送速度能达到157.3 MB/s,接收速度能达到140.7 MB/s。AXI DMA数据存储在0x01100000中,处理完成后的数据写入地址0x01500000。DDR内存结果显示数据传输准确无误码,由此可见DMA实现了PS与PL数据准确且高速的互传。

3.2 可靠性测试及安全性分析

由于测试所用图像数据为1 080P的灰度图,因此一帧图像数据的帧头为c0438780。其中frame flag=2’b11,frame ID=6’b000000,image high=1 080,image width=1 920。帧信息添加模块将帧头添加到由PS输入的数据流前,输出数据流为m_axi_tx_tdata。解帧模块接收到帧头信息c0438780后认为一帧数据到来,此自定义专用帧头以保证系统的安全性。除去帧头信息后将有效数据m_tdata传输给后续算法处理。图6(a)为帧信息添加模块输出结果,图6(b)为帧信息提取模块输出结果。经测试系统传输准确无误码,具有较高的可靠性及安全性。

图6 数据发送接收链路测试结果

3.3 误码性评估及线速率测试

ZCU106中提供的SMA接口信号一共4个,包括一对发送数据信号txp和txn,一对接收数据信号rxp和rxn。在进行系统仿真收发测试时,对于硬件验证单板只能进行单核自回环连接,所以将TX(txp和txn)和RX(rxp和rxn)约束至开发板SMA接口,其外部采用光纤进行自环连接,模拟光纤高速数据互传过程。通过IBERT IP对本系统的高速收发器接口进行误码率发送器发送伪随机码,接收器接收后检查数据传输的准确性。测试眼图结果如图7所示,可见信道质量良好,线速率达到2.5 Gb/s,眼图张开率82.35%,没有数据接收误码。

图7 IBERT测试眼图

3.4 边缘检测算法验证结果

本次测试应用到的卫星图像为机场图像。在进行上板验证之前,采用Matlab对图像进行Sobel处理并采用Vivado自带仿真工具进行仿真。

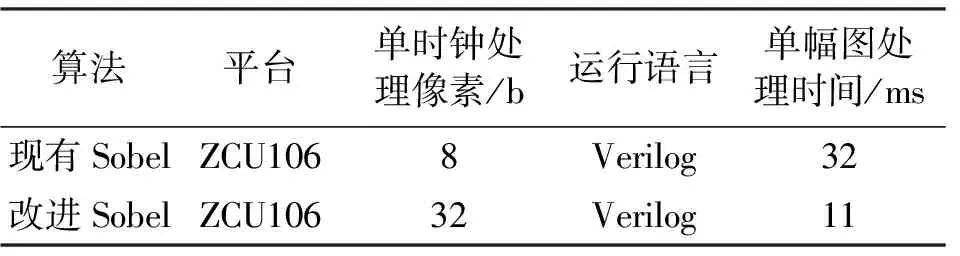

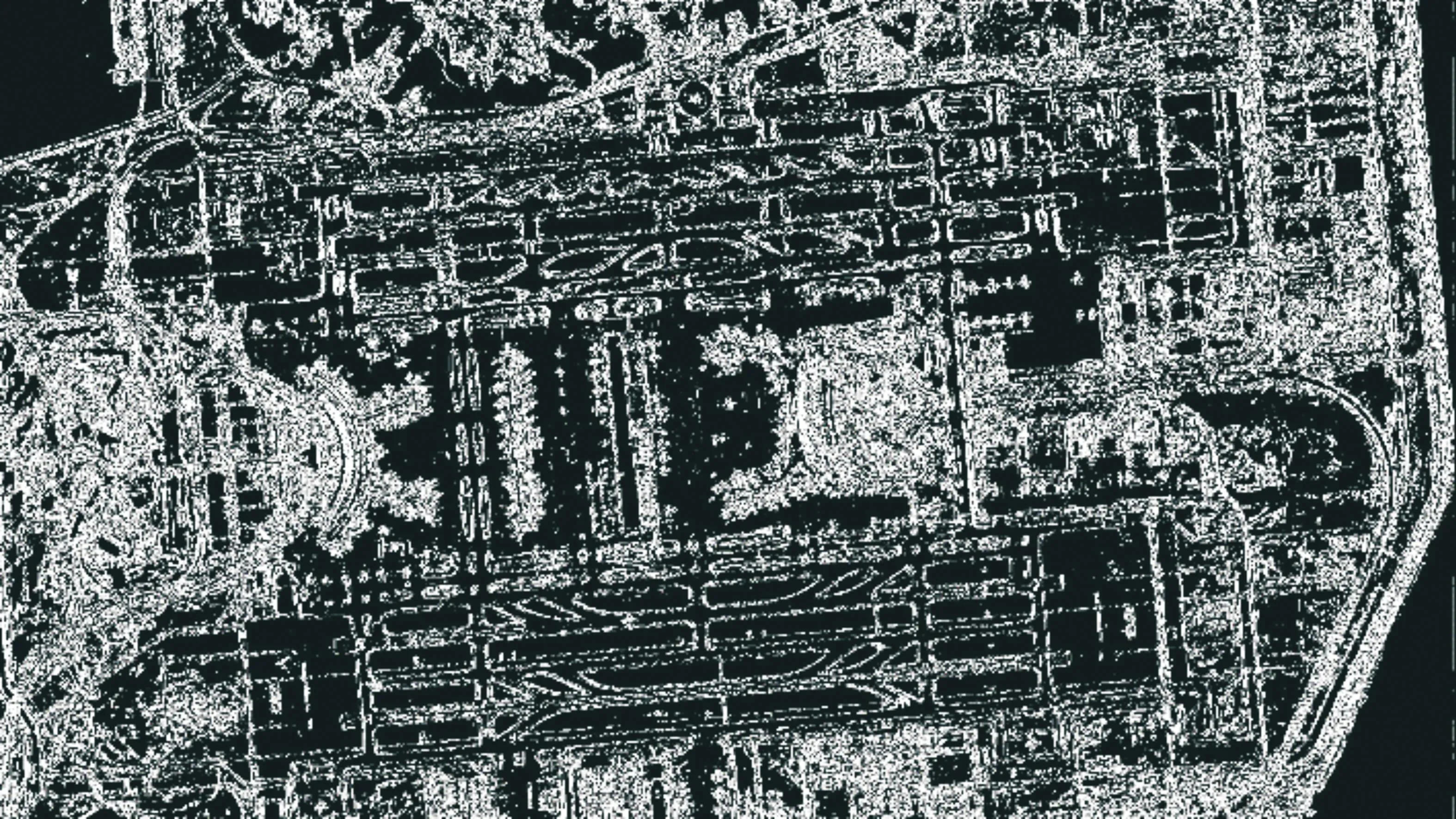

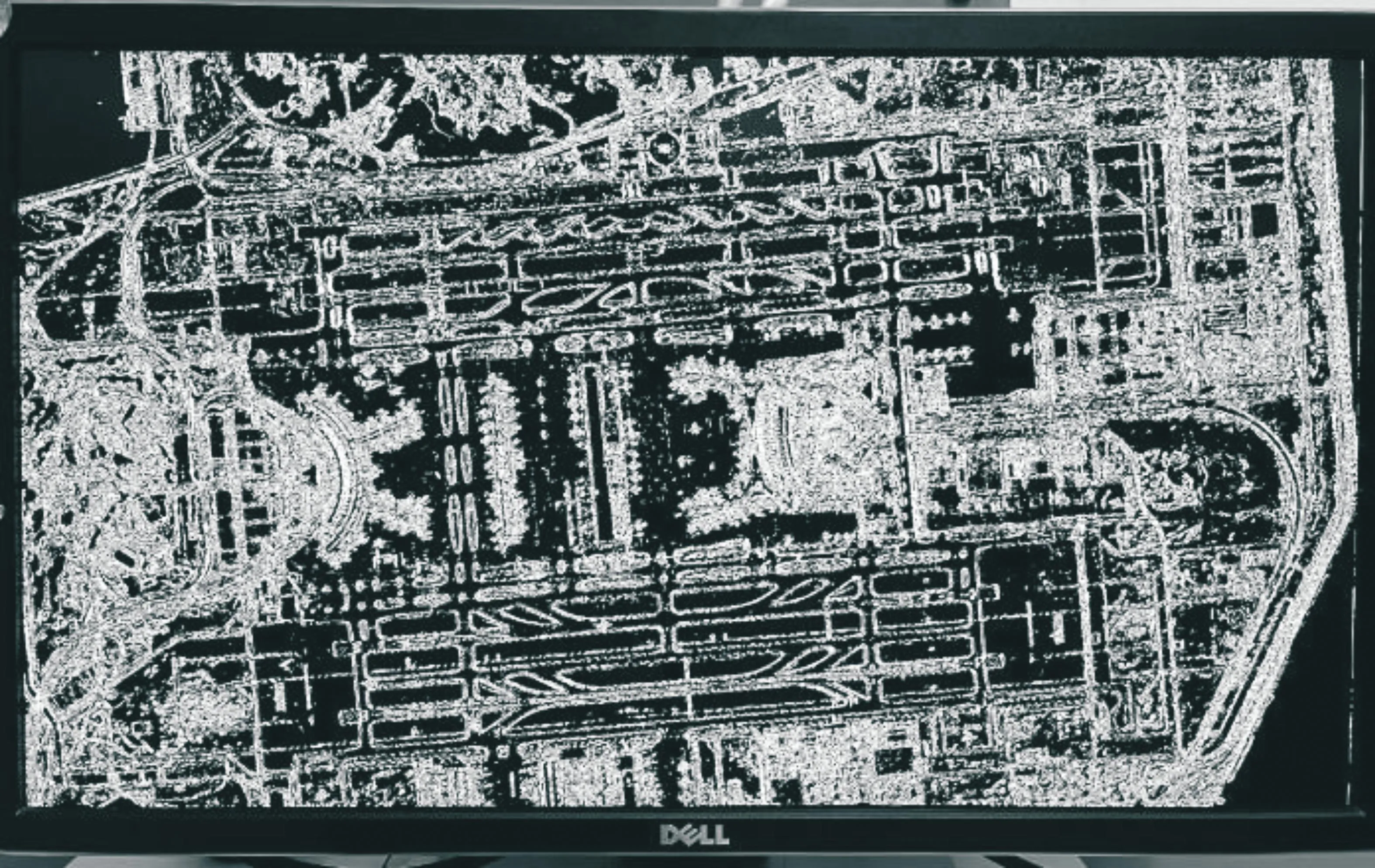

各个Sobel处理运行时间如表1所示,采用现有Sobel算法处理一幅图需要32 ms,改进的并行Sobel算法用时11ms。试验结果表明相比CPU实现图像处理,FPGA将处理时间缩短了10倍左右。相比现有Sobel算法,采用改进的并行化Sobel算法将处理时间缩短了3倍。将Vivado仿真后的数据结果利用Matlab工具恢复可视化图像,如图8所示。Sobel边缘检测后在dell显示器显示结果如图9所示。将显示器显示结果与Matlab仿真Sobel处理后的结果对比,表明利用本系统较好地实现了Sobel边缘检测功能,且呈现出的图像边缘信息也较为理想。

表1 Sobel处理运行时间对比图

图8 Sobel处理仿真显示结果

图9 Sobel处理后显示器显示结果

4 结束语

高速实时稳定可靠的商用星上数据高速传输与实时处理系统成为航天卫星研制的瓶颈。本文基于Xilinx ZYNQ UltraScale+设计了一种星上数据高速传输与实时处理系统。采用DMA方式实现PS与PL数据高速互传,数据传输准确且读写性能优异。发送端采用帧信息添加和接收端提取模块以保证链路的可靠安全传输,采用简单通用的Aurora协议作为星上设备交换高速接口,并且采用两种Sobel算法证明系统具有较好的通用性与实时性,对星上数据处理设备的研制及星上图像算法的处理具有一定的借鉴意义。

但是,本文研究仍然有值得改进的地方:一是PS端采用C代码对DMA进行配置以及初始化,对整体性能存在影响;二是对卫星图像的Sobel算法可以进一步优化,以实现对卫星图像更加有效的去噪,最大程度提取关键边缘信息。