基于面向TTE的新型数据综合系统的设计与实现

2024-02-22张会新洪应平姚玉林杨应杰

张会新,洪应平,姚玉林,杨应杰

1.中北大学仪器科学与动态测试教育部重点实验室;2.91515部队

0 引言

TTE是目前基于以太网的新型总线技术,将传统以太网与时间确定性紧密联系。相较于传统以太网,TTE具有高宽带、实时性、确定性、可靠性等特点[1-3]。通过计算PCF帧以及获取同步时间来提高时钟同步精度[4-6],能够有效实现全局时钟同步,显著提高了网络数据的可靠性和网络资源利用率。同时,TTE完全兼容AS6802协议和IEEE802.3协议[7-9]。而TTE发展已成必然趋势,读取TT数据需设备兼容TTE协议,传统总线与新型总线无法混合编帧。同时,在实际工程中设备采用多种通信端口。各种通信端口协议、传输距离、通信速率不同[10-12]。数据组合存在冗杂的数据处理问题。综合上述背景,本文提出了面向TTE的新型数据综合系统的设计与实现,将多种协议数据综合传输与TTE相融合,实现了远程控制。在能够满足系统高稳定性、高确定性要求的同时,还可通过上位机调控所需数据流,提高测试效率。

1 总体设计方案

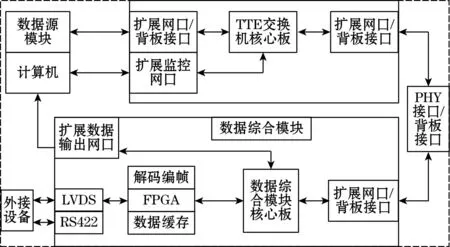

测试系统遵循模块化、高稳定和高效率的设计思想,整个系统由3块模块构成,分别为数据源模块、数据综合模块和交换机模块,数据源模块作为背板使数据综合模块和交换机模块通信。模块与模块之间使用VPX高速接插件,完成各模块之间数据传输。同时,各模块上配备1块TTE核心板,内部集成TTE功能协议,方便接收TTE数据流。其总体设计框图如图1所示。

图1 系统总体框图

该系统主要实现数据接收与发送两部分。TTE数据由数据源模块,经TTE交换机模块将数据流传输到数据综合模块,以此来实现数据接收。数据综合模块可将接收TTE数据经扩展数据输出网口发送给计算机,通过对比来验证数据的准确性。同时,数据综合模块底板可以接收LVDS数据、RS-422数据,还配备千兆以太网口接口。该模块将接收的多种数据经综合编帧,按要求输出。

2 关键硬件电路设计

2.1 TTE交换机模块

系统中TTE交换机板卡作为“交通枢纽”,实现TTE数据的接收与转发,不参与数据流的综合编帧。该板卡所使用的以太网PHY芯片为88E1145。TTE核心板与底板各配备1块88E1145芯片,底板为TTE核心板引出3路以太网口:第1路与上位机相连,方便更改TTE核心板的参数配置,同时监控交换机数据延迟与抖动,以及TTE同步精度;第2路与TTE数据源板卡相连,转发TTE流数据;第3路镜像输出流过交换机的数据,方便监控。底板中扩展出以太网接口,通过接插件与数据综合板互通,形成TTE数据回路。

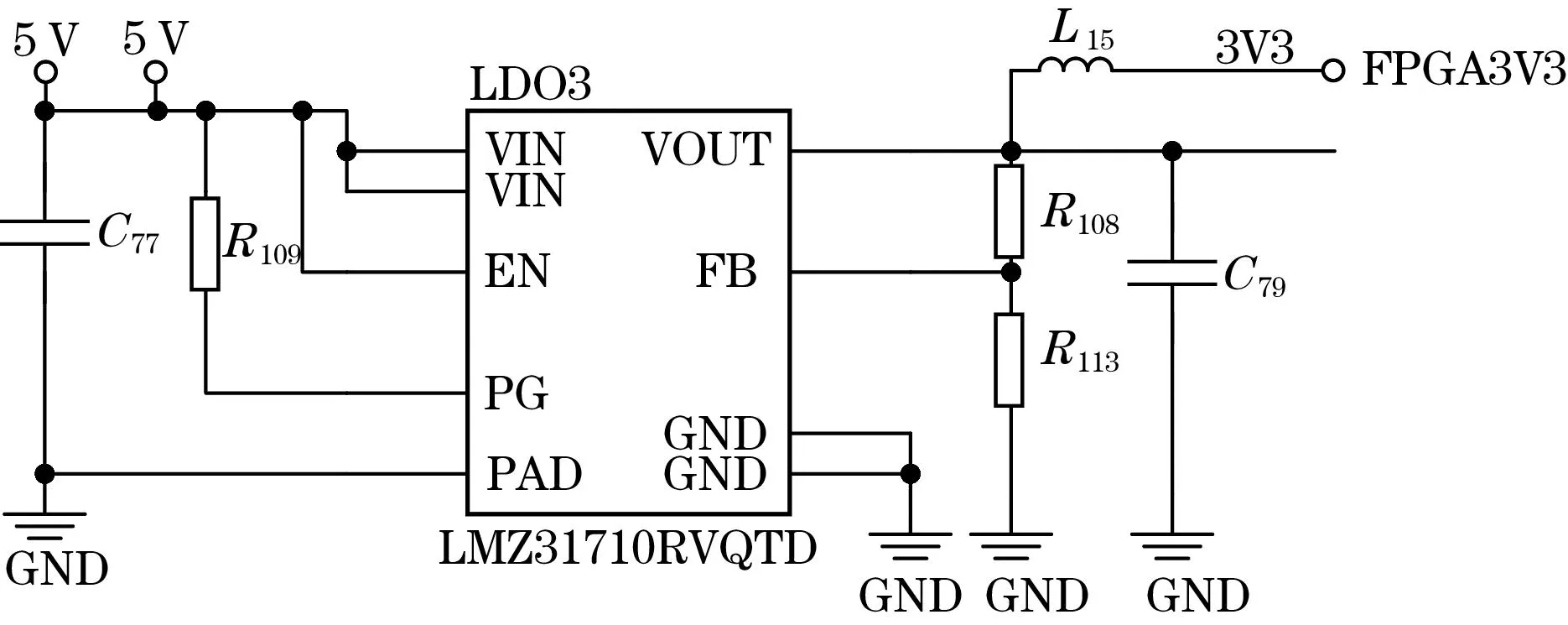

2.1.1 电源电路设计

为使系统更加稳定,设计电源输入电压为5 V,同时各模块电源分离处理,减少器件之间干扰。为保证系统稳定以及启动需大电流推动,选用LMZ31710RVQTD稳压芯片。在满足系统不同电流运行的情下,可通过调节VOUT、FB引脚的电阻提供稳定电压。图2为LMZ3170RVQTD电路图。

图2 LMZ3170RVQTD电路图

2.1.2 网络变压器设计

为了增强电流信号,增大传输距离,提高抗干扰能力,设计了网络变压器电路,如图3所示。GST5009LF适合长距离千兆以太网、全双工应用,支持4对5类UTP电缆,适用于极端环境。

图3 网络变压器电路

2.2 数据综合模块

数据综合板卡用于整合处理数据。板卡中配备TTE、RS-422、传统以太网、LVDS通信接口。主控芯片为XC7K160T,其内部有8对高速串行收发器,通信速率为12.5 Gbit/s,更高效处理数据。36 Kbit双端口RAM,内置FIFO逻辑,用于片上数据缓冲。支持1 866 Mbit/s的DDR3接口。该板卡具有缓存功能,将其他数据与TTE数据进行混合编帧。RS-422等其他类型数据在帧中有固定位置,最终通过以太网传输到上位机。

2.2.1 千兆网电路设计

为了提高数据综合编帧能力,确保数据传输的稳定性和有效性,设计了千兆网电路,如图4所示。

图4 88E1111电路图

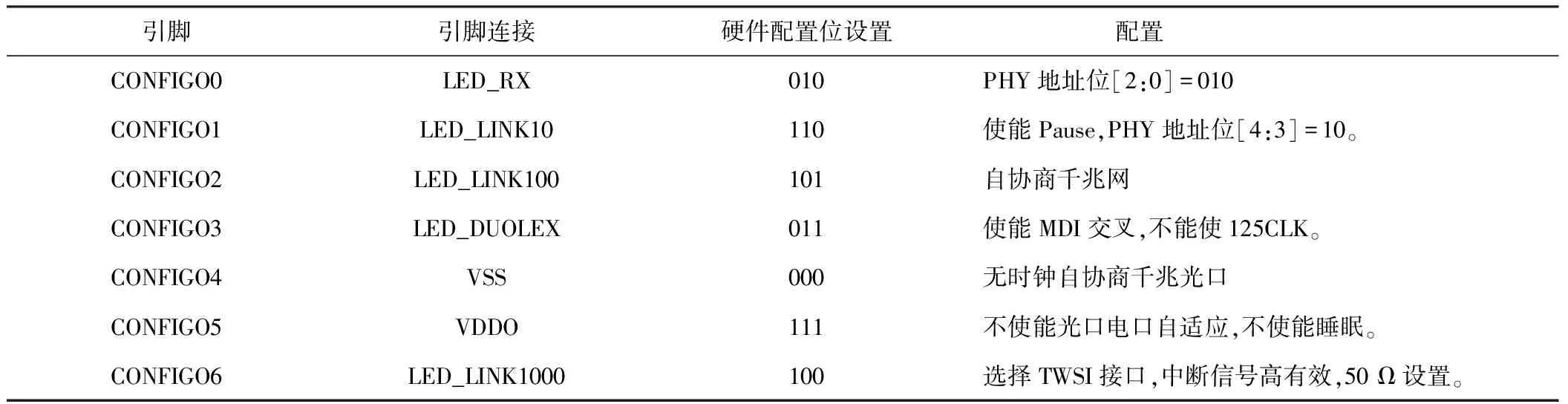

88E1111-BAB2I000芯片可依据混合信号实现均衡、回声和串扰消除,同时以每s千兆位的速率进行数据恢复和纠错。该芯片复位时低电平有效。复位信号拉高前芯片上电10 ms,其拉高时钟需10个时钟周期。同时,操作MDIO接口还需再等5 ms。复位通过配置CONFIG[6:0]引脚可实现PHY Adderss、PHY Operate Mode(操作模式)、Auto-Negotiation(自适应模式)。PHY芯片模式配置如表1所示。

表1 PHY芯片模式配置

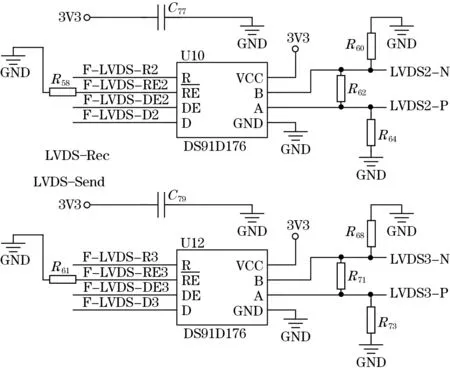

2.2.2 LVDS通信模块设计

LVDS信号的恒流源模式低摆幅输出可实现高速传输能力,同时点对点传输速率可达800 Mbit/s。稳定性好、抗压强度大。因此TTE数据与LVDS数据混编更加必要,经过调研比较多种芯片,最终选取多点低压差分信号线路驱动器及接收器,芯片型号为DS91D176,电路如图5所示。驱动器输入端接收LVTTL/LVCMOS信号转化为M-LVDS信号。接收端将此信号转化为3 V的LVCMOS信号。

图5 LVDS电路

2.2.3 RS422通信模块设计

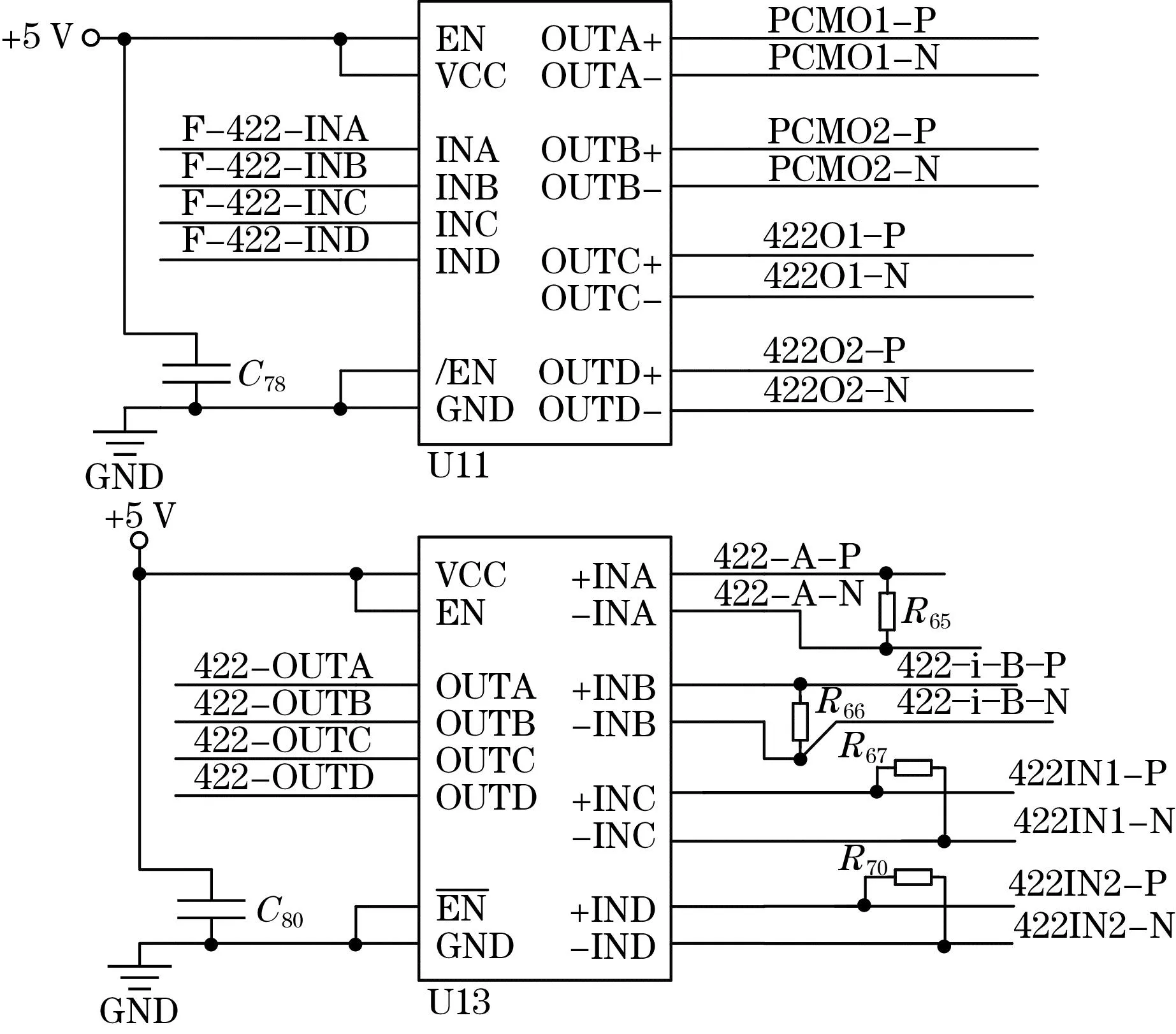

为了提高TTE数据灵活性,适应传统化设备,本系统数据综合板卡引入RS422接口。其数据信号输出为差分信号,由驱动能力强的发送器和输入阻抗高的接收器组成硬件电路,在传输距离和速度上优于RS232接口。本系统中RS422接口的收发器选用DS26C31芯片,具有4路差分线路驱动器,拥有多个收发节点,更好平衡数字数据传输。将TTL或CMOS电平转化为RS422电平,保留CMOS低功耗特点。该电路使其在不加载RS422总线时断电。同时,二极管静电放电不会对输入造成影响。电路如图6所示。

图6 RS422电路

3 系统逻辑设计与实现

3.1 整体逻辑设计

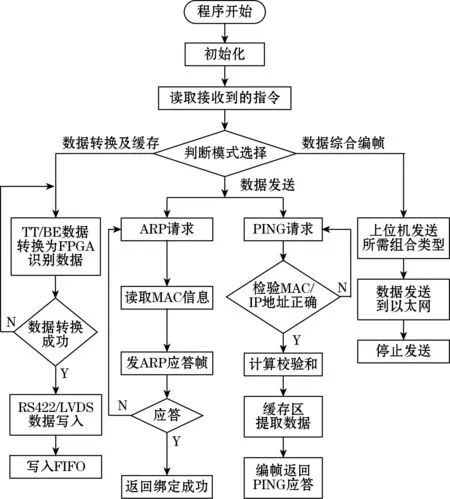

系统总体实现以下功能,分以下3种模式,分别为数据转换及缓存、数据发送和数据综合编帧。系统总体逻辑图如图7所示。系统上电,板卡及芯片开始复位和初始化。TT/BE数据经TTE核心板转为FPGA可识别数据。同时将转换数据与RS422、LVDS分别写入FIFO,按组合类型进行编帧等待上位机指令。当上位机经ARP、ICMP(PING)、UDP协议与上位机互通后,按指令发出综合数据。上位机实时监测TTE数据以及同步情况,另一网口将数据镜像输出。

图7 系统控制逻辑流程图图

3.2 TTE数据结构

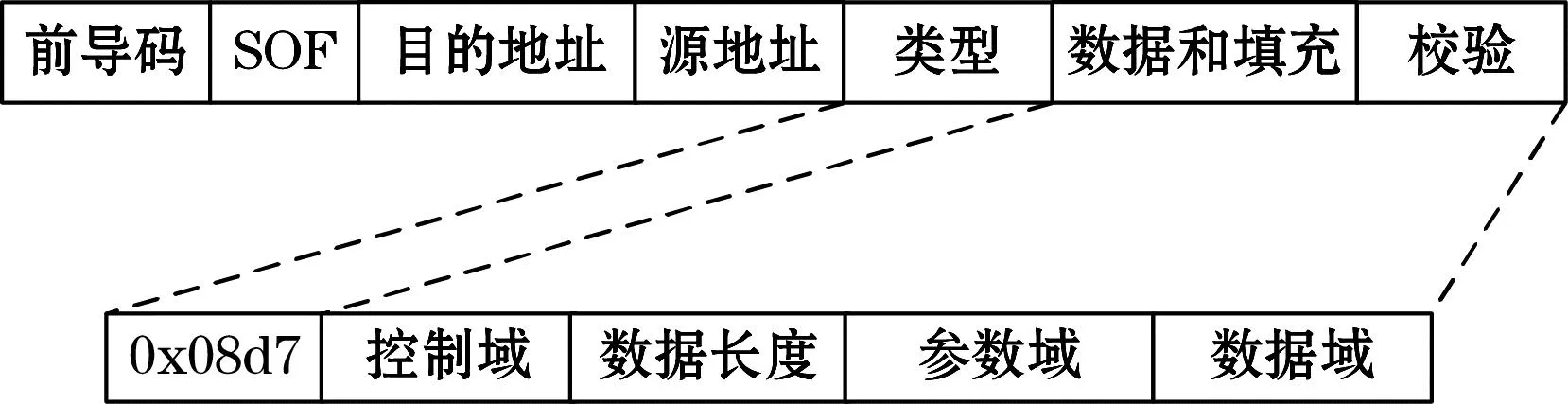

相较于传统以太网,TTE增加了时间触发流量类型。包括时间触发(TT)消息、速率约束(RC)消息以及尽力传输(BE)消息。这3种数据符合标准以太网帧。TT/BE数据实时兼容AS6802协议和IEEE802.3协议,只是它们帧格式的Type域不同。TTE网络设备提前设定了离线时间调度表,可以按照定义的表收发时间触发业务。时间触发消息(TT)便可避免物理链路和发生碰撞,减少数据帧延迟和抖动,提高数据传输安全性和实时性。此外,除了TT业务,还可去处理非时间触发业务,确保业务即时传输。若非时间触发业务未处理,合适时间会再次触发TT业务。TT帧格式示意图如图8所示。

图8 TT帧格式

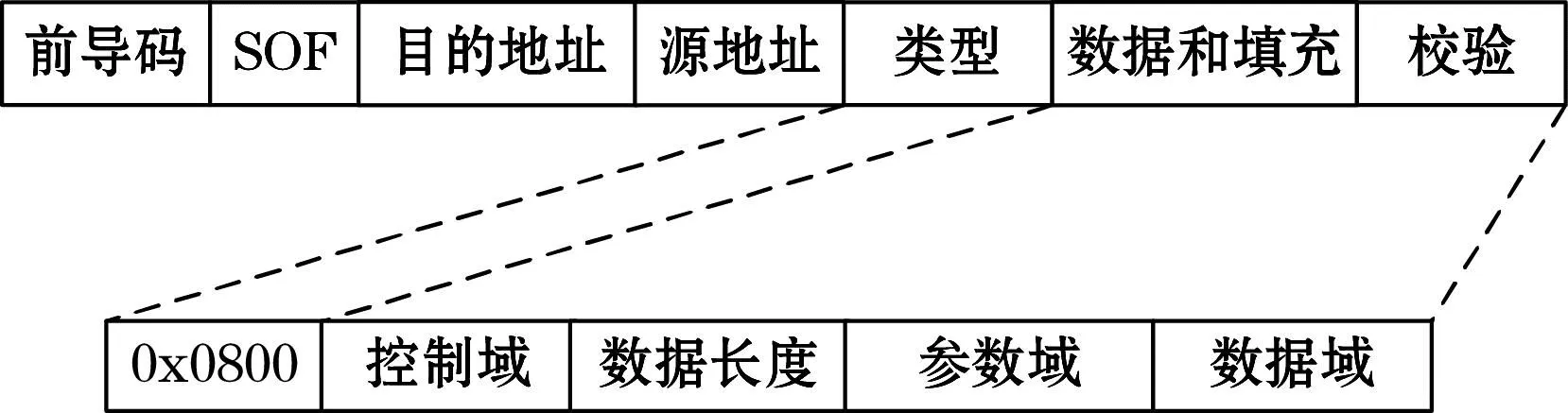

尽力传输(BE)消息符合IEEE802.3标准的传统以太网,兼容现有的以太网标准。BE业务在传输时无需考虑传输时间、延迟与抖动,不考虑能不能到达目的节点。在TTE数据中,BE业务在无其他业务时才会传输,其传输优先级最低。图9是BE帧格式示意图。

图9 BE帧格式

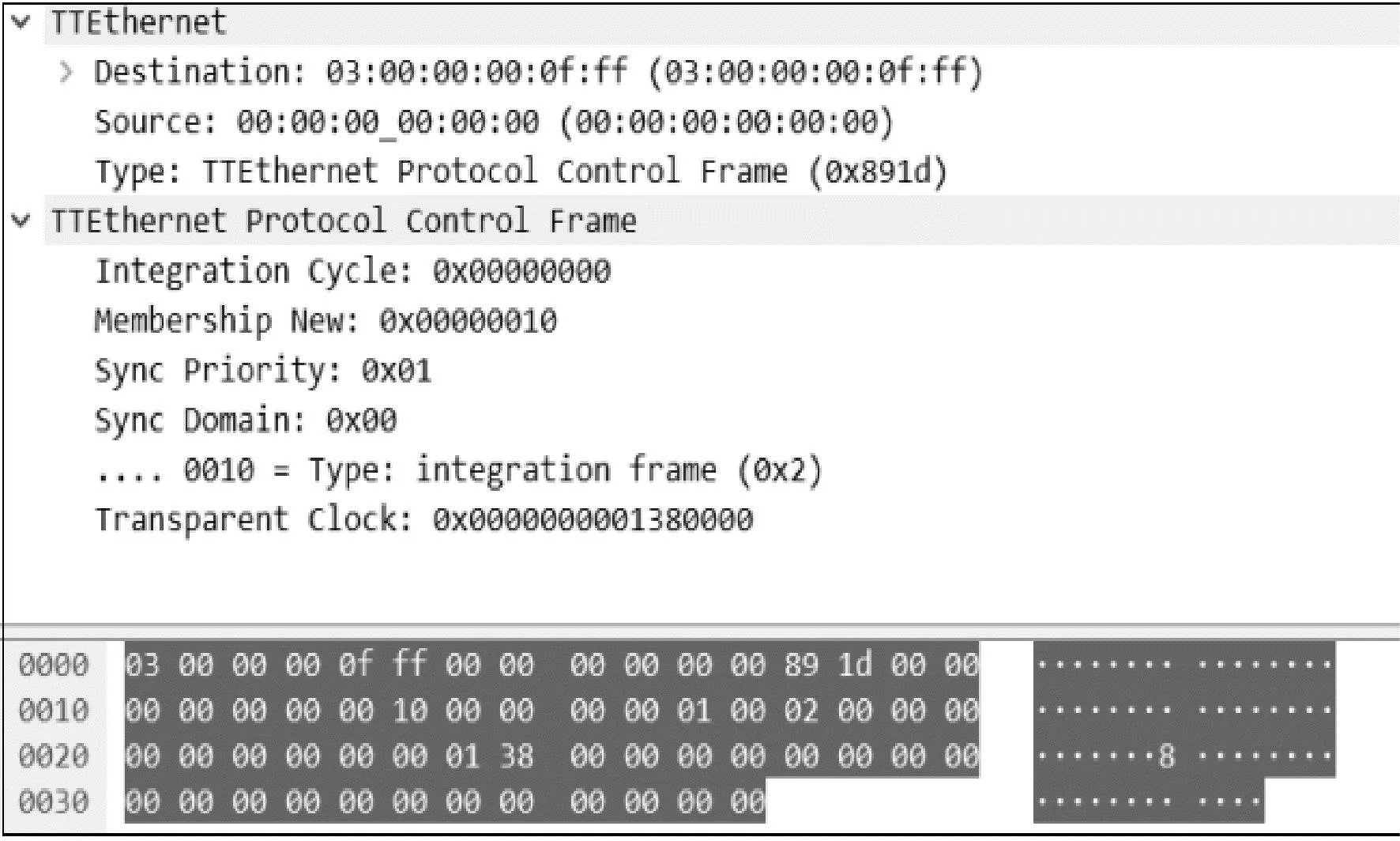

协议控制帧(PCF)仅作用于时钟同步阶段,属于TT帧。时钟同步阶段,同步主节点将PCF帧发送到压缩主节点,压缩主节点根据PCF帧所到时间计算平均值,后将新的PCF帧发送到同步从节点来实现同步。PCF帧格式示意图如图10所示。

图10 PCF帧格式

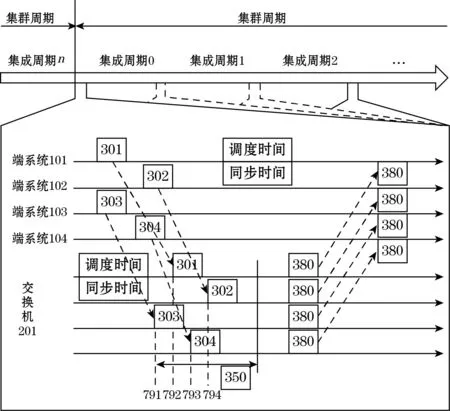

3.3 PCF帧同步逻辑

时间触发以太网由全局高度统一的本地时钟来保证TT数据的安全性、实时性。分布式时钟同步对TTE很关键。主要通过计算机、网络帧抓包来查看时钟同步情况,确定系统是否正常。本系统测试时,数据编帧后发送到上位机,经监测计算机可实时查看同步信息。同步主节点(SM)先将PCF帧发送到压缩主节点(CM)。压缩主节点将点到点所消耗时间取平均值,重新组合FCF帧返回同步主节点,实现同步。PCF帧时钟同步逻辑如图11所示。101~104端系统为同步主节点,201交换机为压缩主节点,其余节点为同步客户端。同步控制器转发301~304 PCF帧到压缩主节点。压缩主节点建立一组新的PCF380后返回端系统,将终端系统与其他控制系统连接起来。

图11 PCF帧时钟同步逻辑

3.4 TTE数据转换逻辑设计

根据时序可将测试数据转化为所需要的波形。TT、BE数据需设备兼容TTE协议。上位机将TTE数据经交换机板卡发送到TTE核心板。将TTE数据转换为FPGA所需波形模块,实现了上位机与数据综合板卡互通。数据综合板卡读取数据包时,核心板卡先将TX_REQ(数据请求信号)拉高,TX_DVAL(数据有效信号)也随之拉高,从而开始传输有效数据。数据传输完成后,有效信号拉低。网路包发送时序如图12所示。

图12 网络包发送时序

3.5 TTE数据综合逻辑设计

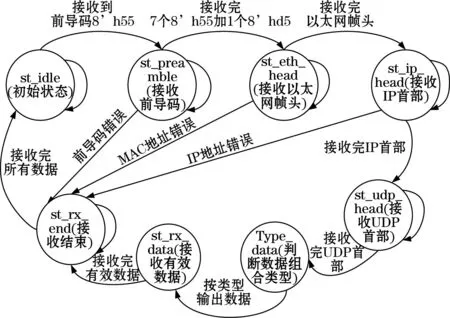

数据综合模块接收到由交换机转发数据综合模块的TTE数据后下载缓存,该模块将TTE帧解码提取数据部分后发送给地面设备。同时数据类型处可区分多种总线数据的标志部分。TTE数据帧结构在数据解码时与传统以太网帧格式相同,而帧类型不同。数据综合模块将各通道的综合数据按照表2的内容向外发送并进行数据编帧。综合数据编帧格式(数据域)如表2所示。编帧后数据包含前导码、IP地址、端口号、协议类型等,经UDP发送。UDP发送模块状态跳转逻辑如图13所示。

表2 综合数据编帧格式(数据域)

图13 UDP发送模块状态跳转逻辑图

4 测试结果与分析

该系统由数据源板卡、数据综合板卡、交换机板卡组成。图14为TTE综合测试系统。数据源板卡通过VPX接插件将交换机板卡和数据综合板卡相连接,同时提供板卡电源和模拟TTE数据。此外搭配TTE上位机管理软件,配置板卡的基本参数,以实现对TTE数据同步精度、通信抖动的监测。

图14 TTE综合测试系统

TTE时间同步测试前,将TTE综合测试系统以及上位机搭建完成。数据发生器产生数据源,编帧后由交换机发送数据综合板卡,该板卡将数据混合编帧后发送到上位机监控界面。可实时监测上位机交换机以及数据综合板卡时间同步精度等信息。TTE交换机各参数监控如图15所示,试验结果表明,交换机同步精度为64 ns,系统完成同步。

TTE数据综合板卡各参数监控如图16所示。时钟同步精度可达40 ns,通信抖动为392 ns。

图17为PCF同步数据图,包含IP地址、MAC地址、帧类型、数据、PCF帧类型、整合周期以及同步时钟延迟信息。

图17 PCF帧同步数据

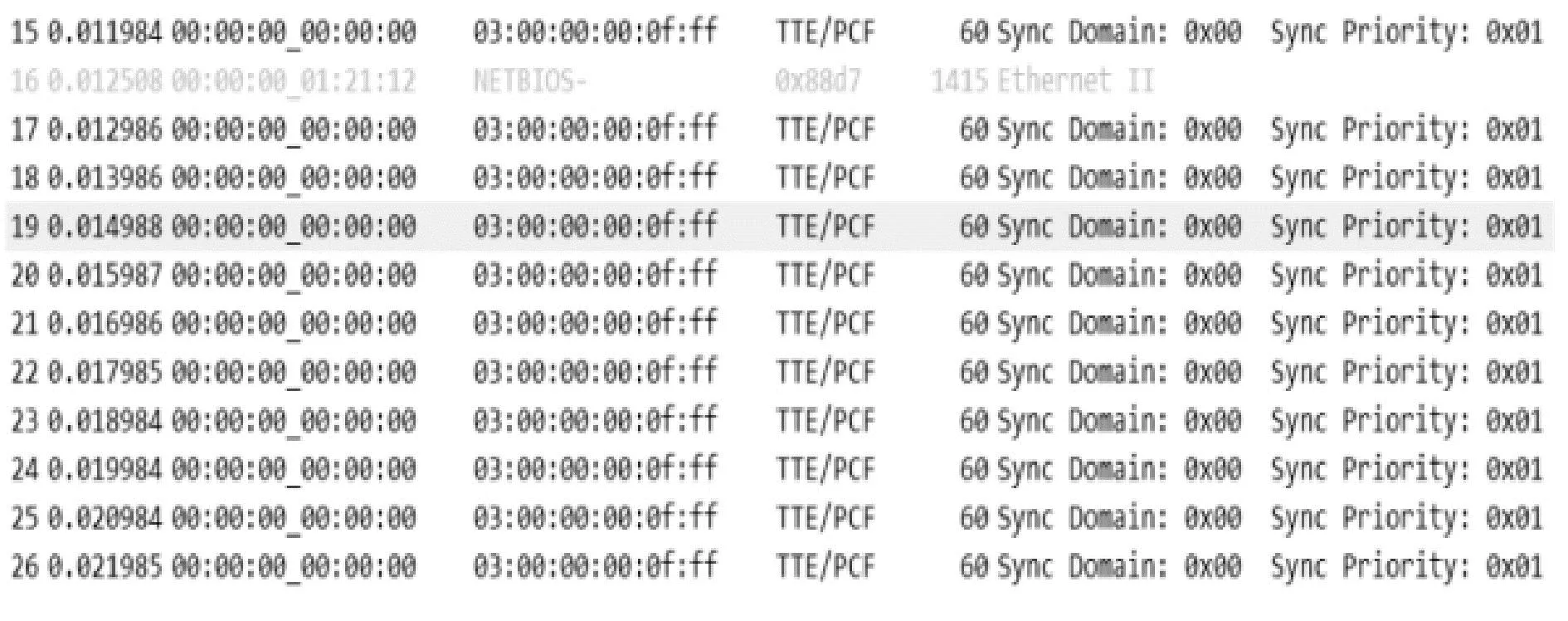

镜像网口输出经过交换机的PCF帧以及数据类型为0x88d7的TT数据,如图18所示。

图18 镜像网口报文

系统与上位机连接后,将适配器网络IP地址、端口号等设置完成后,上位机发送数据综合排列类型指令,数据经传输、转换、综合后,通过UDP协议发送到上位机。UDP数据信息如图19所示。行标号0030、0090、00f0、0280分别为LVDS、RS422、TT、BE数据。实验结果表明:该系统实现多种数据混编,满足设计需求。

图19 UDP数据信息图

5 结束语

本文提出的面向TTE的数据综合测试系统,以FPGA为控制核心,千兆以太网作为主要通信接口,采用模块化思想设计各种功能板卡,完成了TTE网络与传统以太网的协议兼容,实现了与传统总线的数据融合。系统通过上位机进行控制,能够设置输出数据类型,试验结果表明,该系统能够在同步精度高达40 ns、通信抖动仅为392 ns的前提下,对多种数据混编后稳定输出,无乱码现象。