Virtex-5系列SRAM型FPGA单粒子效应重离子辐照试验技术研究

2024-02-04赖晓玲郭阳明

赖晓玲,郭阳明,巨 艇,朱 启,贾 亮

(1.西北工业大学 计算机学院,西安 710072;2.中国空间技术研究院 西安分院,西安 710000)

0 引言

静态随机存储器(SRAM,static random access memory)型现场可编程逻辑门阵列(FPGA,field programmable gate array)是一种可以重复编程的FPGA,电路功能由存储在器件内部配置存储区的配置文件确定,用户可以通过配置接口进行在线调试或者远程加载。随着微电子技术的不断进步,SRAM型FPGA已经发展成为具有丰富的可编程逻辑资源,支持高速应用的大规模可编程器件。由于SRAM型FPGA具有高性能、可重构的优点,已经广泛应用于宇航领域,成为星载设备的核心处理器件[1-3]。但是SRAM型FPGA具有大量配置存储单元,在空间环境下受到高能粒子轰击可能发生单粒子效应从而对电路功能产生影响,因此空间应用时必须进行单粒子效应敏感性评估和防护设计[4-5]。

Xilinx公司的SRAM型FPGA器件功能强大、性能优异。根据性能、资源和规模的不同,该公司的SRAM型FPGA器件可分为Spartan、Artix、Kintex和Virtex系列等。其中,Virtex系列是Xilinx公司的高端器件,具有逻辑资源丰富、高带宽、高速度和大规模集成的特点,适用于高端通信、数据中心、嵌入式视觉、高性能计算和控制系统等领域,也越来越多的应用在航空航天中[6]。

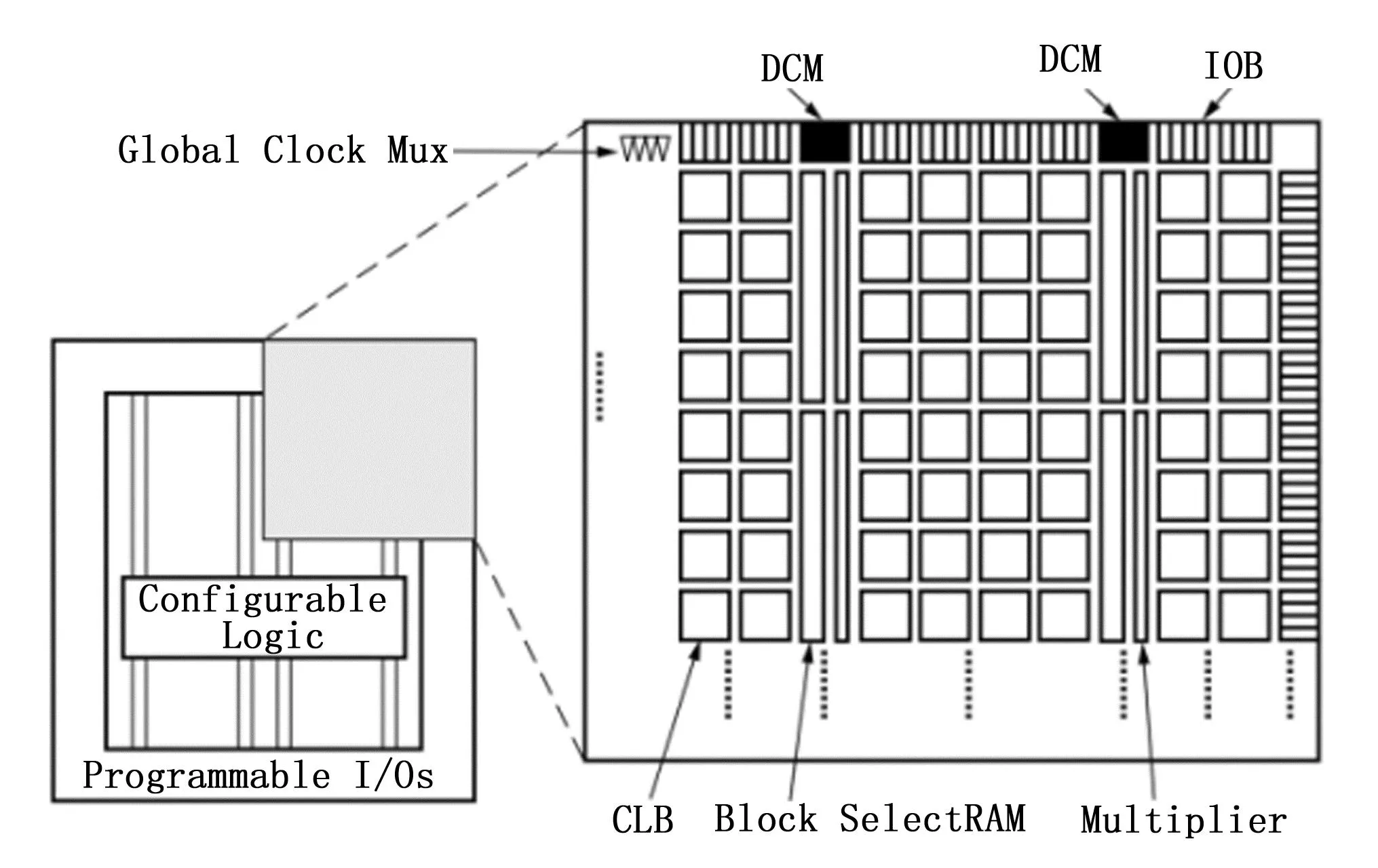

SRAM型FPGA可以看作由配置存储器和用户可编程逻辑构成的两层架构[7]。用户可编程逻辑包括可编程块(CLB,configuration logic block)、IO块(IOB,IO Block)、块存储器(BRAM,block RAM)、数字时钟管理模块(DCM,digital clock manager)、DSP48、其他资源(如处理器核、PCIe、高速接口等)。用户可编程逻辑的具体功能与连接关系由配置存储器(CRAM,configuration RAM)决定。SRAM型FPGA两层架构示意图如图1所示。

图1 SRAM型FPGA两层架构示意图[7]

根据国内外试验研究[8-9],Xilinx公司的SRAM型FPGA属于体硅CMOS器件,空间应用时主要受到总剂量效应和单粒子效应的影响。单粒子效应包括单粒子闩锁(SEL,single event latch-up)、单粒子翻转(SEU,single event upset)、单粒子功能中断(SEFI,single event function interruption)和单粒子功能失效(SEF,single event failure)[10-12]。SEL是指单个粒子入射产生的电荷触发了器件内部的寄生P-N-P结构电流正反馈,最终导致器件烧毁。SEU是指单个粒子入射引起电荷沉积导致的存储单元状态翻转。SEFI是指器件中的特殊存储单元发生SEU后导致器件功能丧失,如SelectMAP SEFI、FAR SEFI及POR SEFI等。SEF是指用户逻辑电路中的存储单元(主要指触发器Flip-Flop和BRAM)或配置存储器发生SEU造成用户功能电路错误或者失效。SEFI和SEF都是器件内部的存储单元发生SEU对电路功能造成影响,区别在于存储单元的类型和所属电路功能不同。

SRAM型FPGA空间应用时,用户主要关心器件所加载的用户功能电路在轨发生SEF的概率。导致用户电路失效的来源主要包括CRAM、BRAM、用户Flip-Flop和特殊电路寄存器发生的单粒子翻转。CRAM发生单粒子翻转可能导致查找表(LUT)、CLB、路由矩阵、布线开关等发生变化,造成电路逻辑错误或互联线桥接错误,引起工作电流增加,此外,SEU在用户逻辑电路中通过故障耦合和传递,最终导致用户电路输出错误、功能异常甚至功能中断。CRAM的单粒子翻转在FPGA全部单粒子翻转事件中占90%至95%,是器件发生SEF的主要原因。BRAM一般用于存储用户电路运算过程中产生的大量数据或参与计算的参数。根据数据更新频率的快慢,单粒子翻转导致电路运算结果错误的持续时间存在差异。用户Flip-Flop用于实现控制电路中的寄存器或少量数据寄存,发生单粒子翻转可能导致电路状态异常或者运算数据错误。NASA给出了SRAM型FPGA单粒子功能失效率(SEF)的计算公式[5]:

P(fs)error∝PConfiguration+P(fs)Functional Logic+PSEFI

(1)

其中:PConfiguration是配置存储器翻转导致的失效率;P(fs)Functional Logic是用户逻辑电路翻转导致的失效率,主要来源是用户Flip-Flop的单粒子翻转和组合逻辑的单粒子瞬态被后续寄存器捕获后产生的翻转;PSEFI是器件发生SEFI导致的失效率,概率极低。可以看出,CRAM、BRAM和用户Flip-Flop发生的单粒子翻转是导致器件功能失效的主要因素,是单粒子翻转防护设计的重点对象。

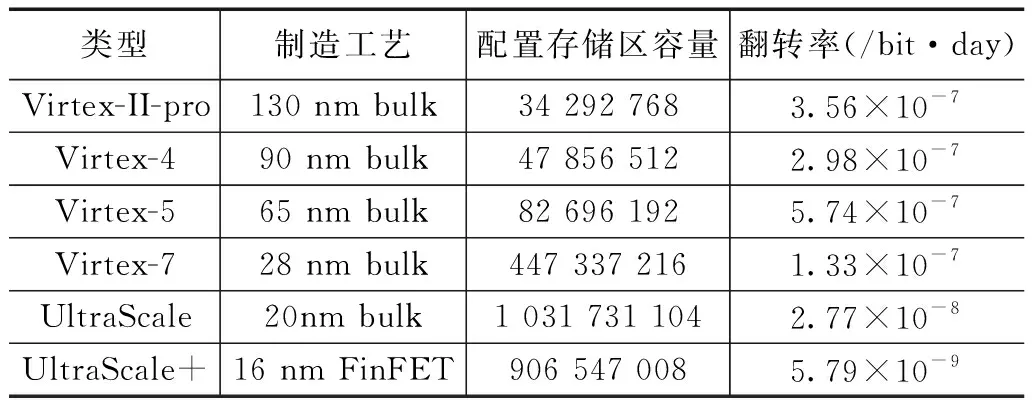

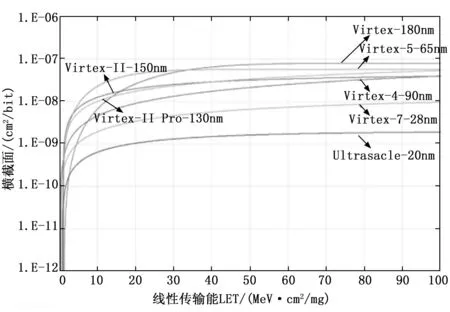

国内外学者开展了大量针对Xilinx公司的SRAM型FPGA器件单粒子效应的地面模拟辐照试验。在美国国家航空航天局NASA针对商用现货(COTs,commercial off-the shelfs)器件编写的器件辐射环境选用指南[13]中,将Xilinx的SRAM型FPGA器件的单粒子效应指标数据进行了整理归纳。如图2所示,该图为在重离子加速器试验中获取的SEU韦布尔曲线,主要覆盖了制造工艺特征尺寸在180 nm~16 nm范围的SRAM型FPGA器件。从图中可以看出,工业级器件的单粒子翻转效应的线性传输能(LET,linear energy transfer)阈值均小于3 MeV·cm2/mg,不能满足在轨单粒子翻转指标要求,需对该类器件进行加固设计[14-16],并对加固的有效性进行准确评估。上述器件CRAM在地球同步轨道(GEO)上的SEU概率如表1所示。

表1 Xilinx主要器件配置存储区的GEO在轨预示

图2 Xilinx的主要SRAM型FPGA器件的配置存储器单粒子翻转试验数据[13]

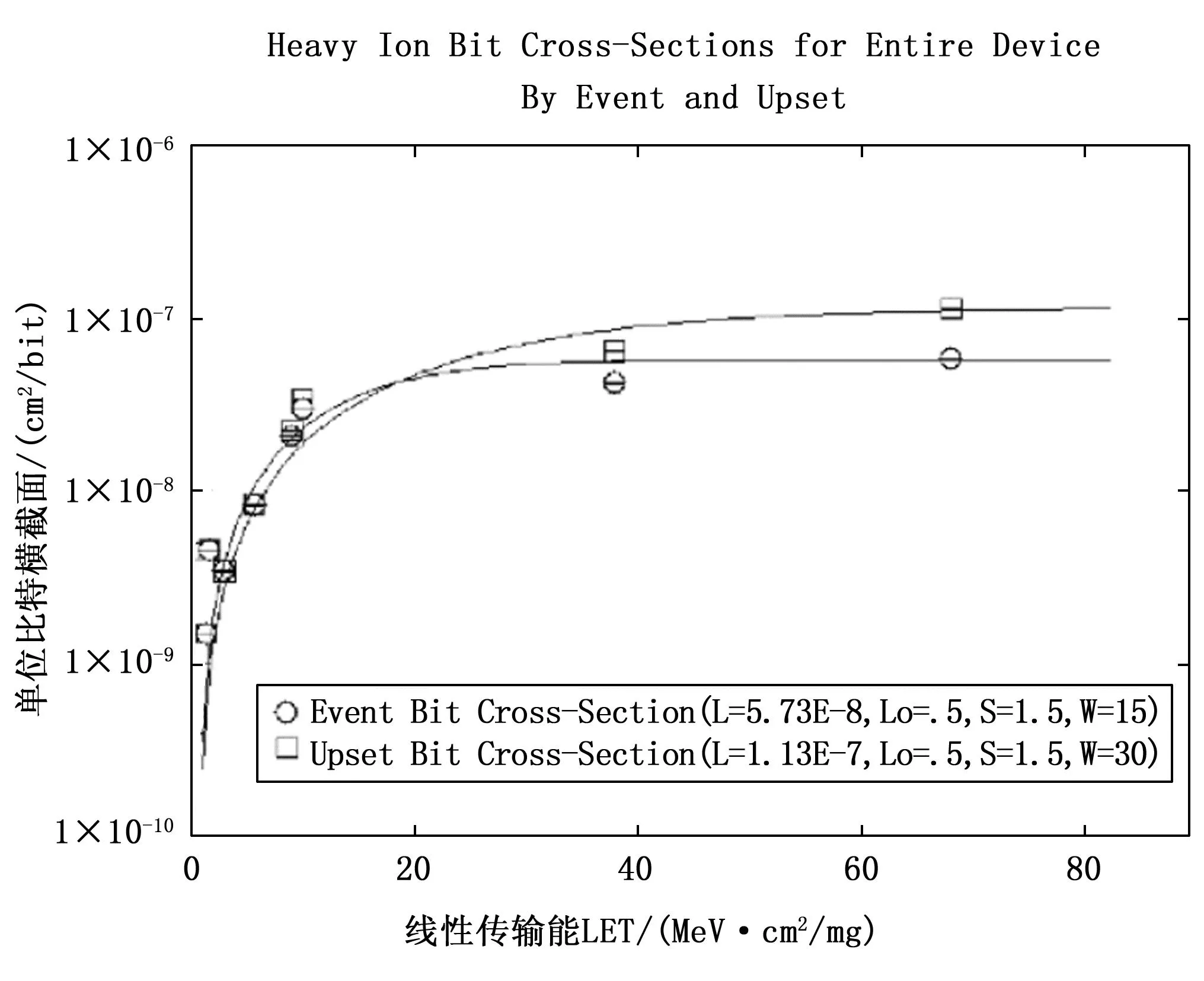

Virtex-5系列包含宇航级与工业级器件。宇航级器件型号为XQR5VFX130T,采用三模冗余、单粒子瞬态滤波、12管DICE结构锁存单元等多种SEU加固技术,能够满足空间应用高可靠要求。Xilinx公司联合美国喷气推进实验室JPL、波音公司等机构联合开展了宇航级Virtex-5系列器件的辐照试验。试验结果表明宇航级器件CRAM的单粒子翻转率(GEO轨道)小于10-10次/比特·天,SEFI概率小于2.76×10-7次/器件·天[17]。该系列器件已被应用于美国宇航局开发的高性能、可重构数据处理系统SpaceCube2.0中。国外Heather Quinn等[18]开展了Virtex-5商业级器件的高能粒子辐照试验研究。试验对象为商业级器件XC5VLX50,获得了重离子饱和翻转截面为5.73×10-8cm2/bit,质子饱和翻转截面为8.61×10-14cm2/bit,利用韦布尔拟合方式获得曲线如图3所示。NASA出具的报告也给出了工业级器件的CRAM在GEO轨道的SEU概率和SEL的大致数据范围,但未能提供具体的测试方法及对SEF的评估结果。国内没有查到关于Virtex-5系列FPGA的单粒子效应辐照试验数据。因此,为评估该器件空间应用的可靠性,需要开展该器件的单粒子效应地面模拟评估试验研究,特别是开展基于典型应用电路的SEF研究,指导航天器电子设备元器件选用和抗辐照加固设计。

图3 XC5VLX50重离子试验韦布尔曲线[18]

本文针对Xilinx公司工业级Virtex-5系列SRAM型FPGA开展了单粒子效应地面辐照试验方法研究,提出了CRAM和BRAM的单粒子翻转测试方法,设计典型电路,开展了三模冗余设计前后SEF测试。通过设计单粒子效应测试系统,并参照QJ 10005-2008《宇航用半导体器件重离子效应试验指南》的相关规定开展重离子辐照试验,获得了Virtex-5器件的SEU、SEF和SEL试验数据。最后利用空间环境模拟软件针对GEO轨道进行了在轨翻转率分析计算,可为该器件的空间应用提供基础数据。

1 试验方法

1.1 辐射源

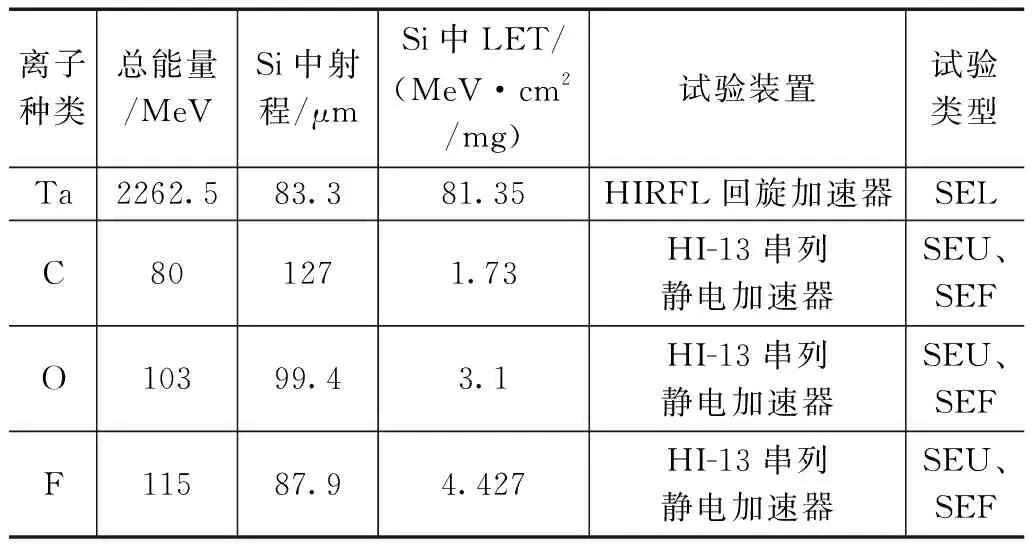

国内可开展地面重离子辐照试验的试验装置主要有中国近代物理研究所的HIRFL回旋加速器和中国原子能科学院的HI-13串列静电加速器。根据被测器件硅衬底厚度和粒子射程,选择回旋加速器的Ta粒子开展SEL试验,选择串列加速器的C、O和F粒子开展SEU和SEF试验。试验所用粒子信息如表2所示。

表2 Virtex-5 SRAM型FPGA重离子辐照试验用粒子信息

1.2 试验对象

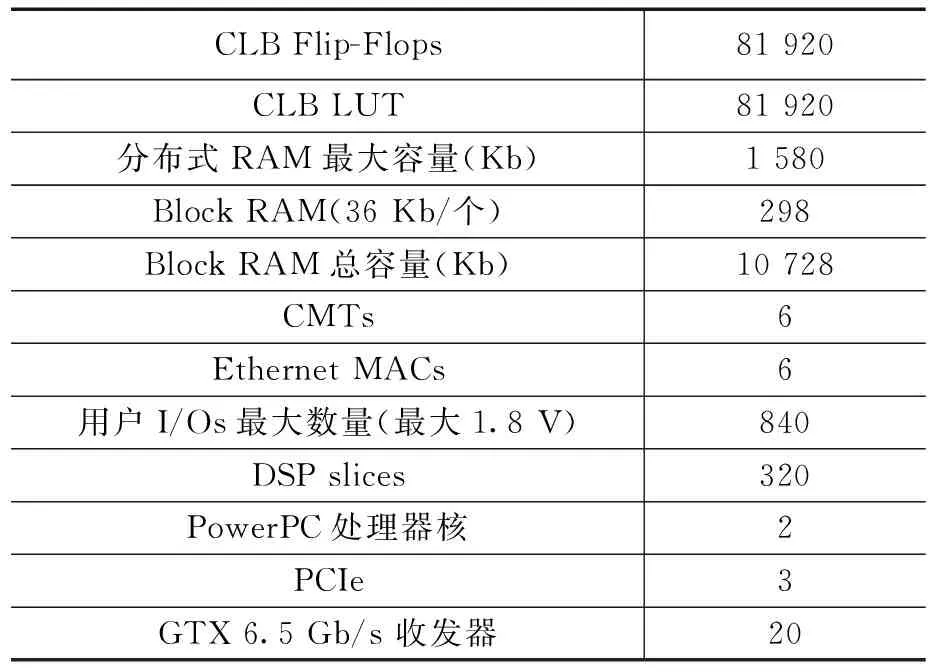

Virtex-5 器件采用65 nm铜CMOS工艺,内核电压为1.0 V。Virtex-5系列SRAM型FPGA器件架构示意图如图4所示。本文试验对象为XC5VFX130T-1FFG1738I,该器件内部集成了20 480个CLB Slice(可提供81 920个用户Flip-flop或最大1 580 Kb分布式RAM)、320个25×18位的 DSP48E、228个36 Kb的Block RAM和其他一些硬核资源[20]。XC5VFX130器件的各类资源组成如表3所示。

表3 Virtex-5系列XC5VFX130T器件特性[6]

图4 Virtex5系列FPGA整体结构及内部CLB结构简图[19]

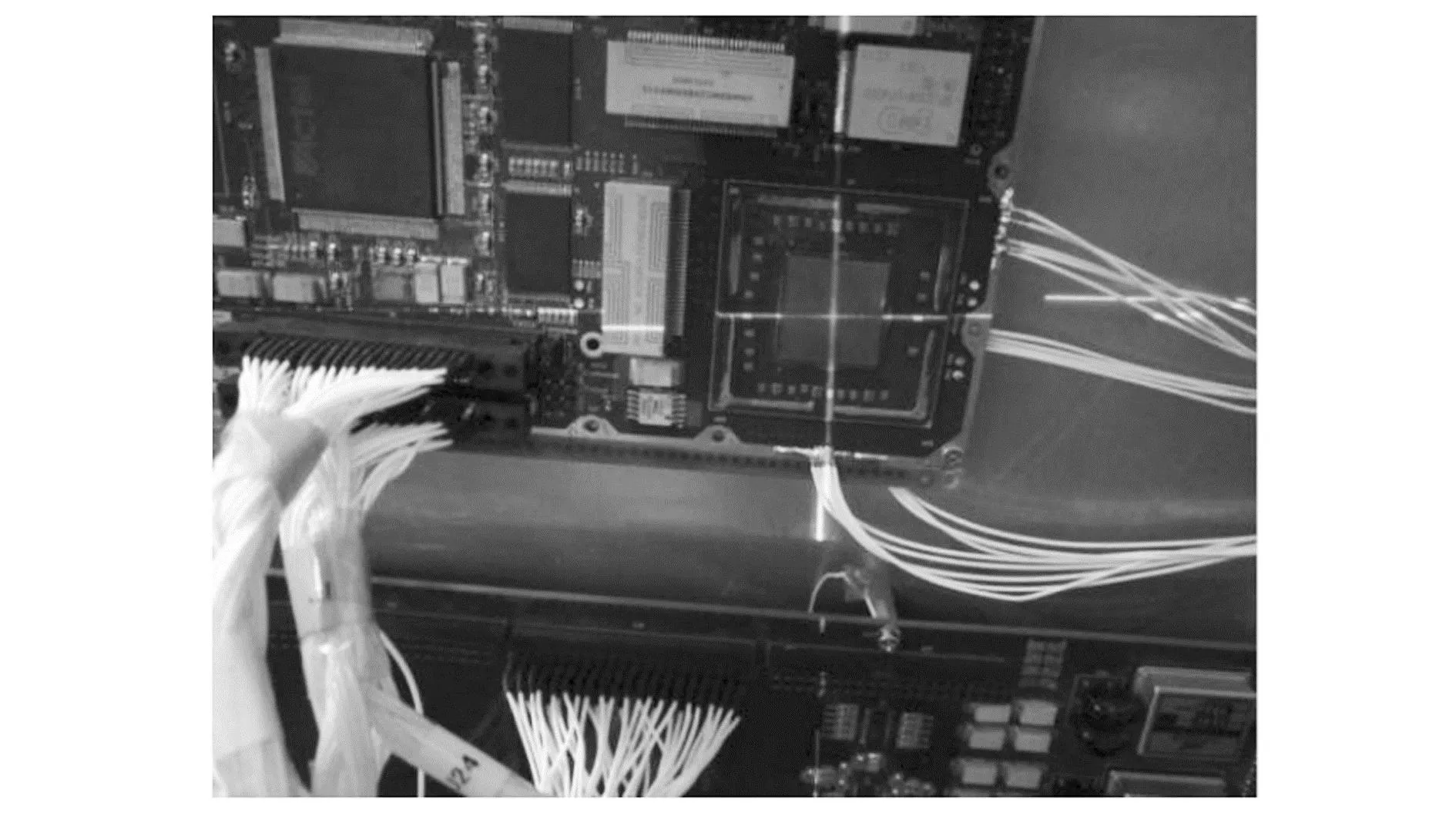

被测器件为倒装器件,重离子入射时会穿过衬底区域,导致无法到达芯片敏感区或由于能量损耗影响有效LET值的准确性。试验前需要对待测器件进行开帽及衬底减薄处理,如图5所示。开帽处理的目的是将芯片或器件的封装罩(通常是塑料封装或金属封装)去除,减薄的目的是使得重离子更容易进入并与器件内部相互作用。要保证开帽减薄后的器件外部引出端和内部引线未受到损伤,电性能测试功能及电流正常。在本次试验中,减薄后芯片衬底到敏感区距离约为70 μm。

图5 DUT减薄前后照片

1.3 单粒子效应检测装置组成

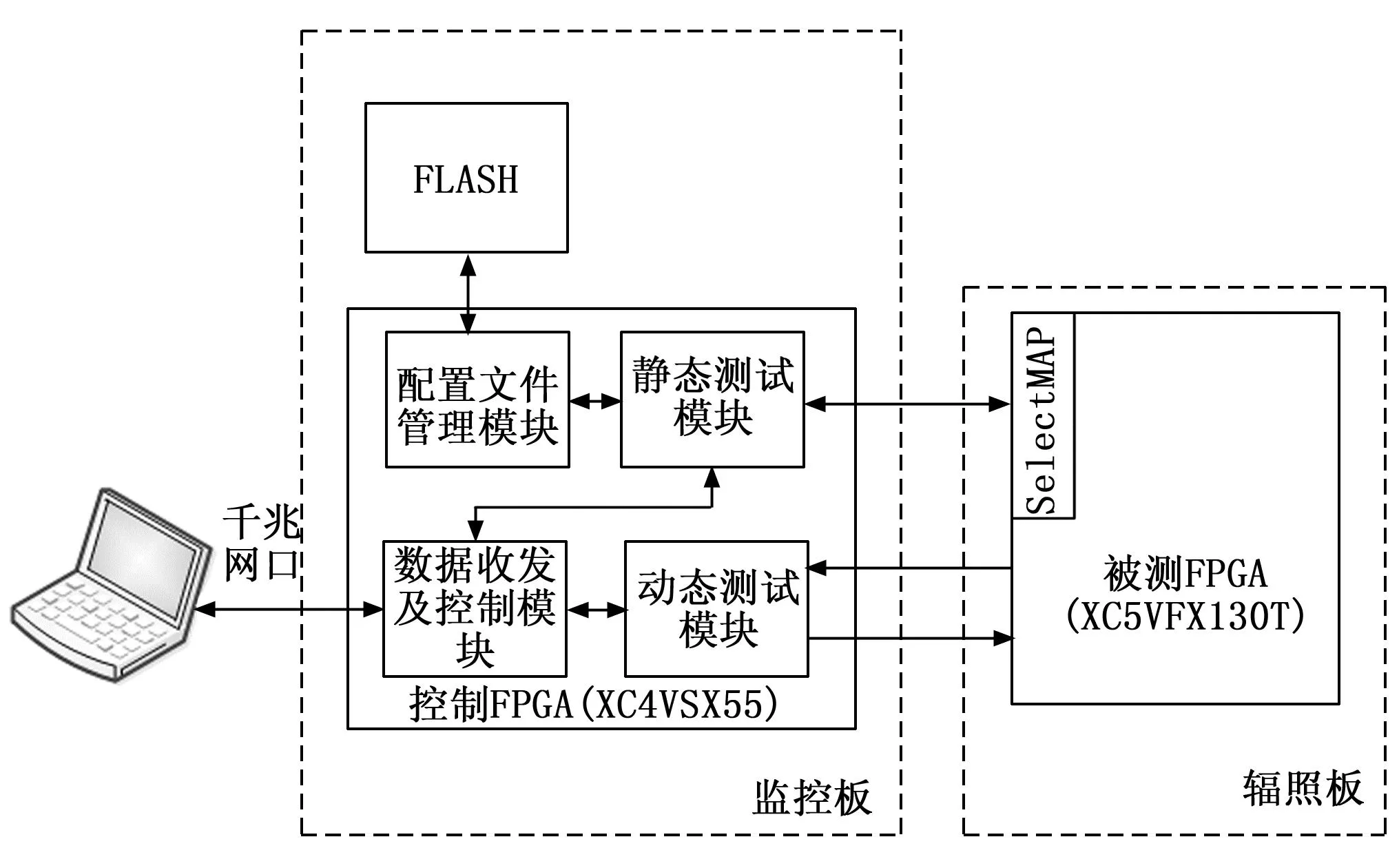

单粒子效应检测系统由上位机软件、监控芯片载板和DUT载板组成。上位机软件作为测试系统控制中心与数据存储分析平台,完成测试项目、测试模式、测试数据、参数设置和人机交互。远程控制监控芯片完成对自身功能参数的设置及对被测芯片的配置、测试和数据上传,并对上传数据进行分析和显示。监控芯片载板与上位机之间基于UDP协议的高速网络连接,以达到高速可靠的数据交互和板间连线最少化的双重目的。监控器件型号为XC4VSX55,作为主控器件通过SelectMAP端口对DUT进行器件配置、刷新和回读,同时使用LVDS接口作为与DUT动态测试电路之间的接口,控制DUT的测试模式、产生测试用输入数据并接收其测试结果数据。DUT载板的核心器件为XC5VFX130T,电压域包括3.3 V、2.5 V和1.0 V,由桌面电源进行单独供电。单粒子效应检测系统整体设计方案结构如图6所示。

图6 SRAM型FPGA单粒子效应测试系统结构示意框图

监控芯片载板上的核心器件为XC4VSX55,主要功能模块包括配置文件管理模块、静态测试模块、动态测试模块和数据收发控制模块。配置文件管理模块负责从FLASH读取位流文件。静态测试模块实现对被测FPGA进行加载和回读的功能。动态测试模块实现向被测FPGA发送输入数据和接收输出数据的功能。数据收发控制模块实现静态数据与动态数据的分析和与上位机之间的数据交互功能。其中静态测试模块通过SelectMAP口实现CRAM与BRAM静态SEU数据回读,因此SelectMAP读写访问接口属于核心电路。按照器件手册要求,Virtex-5系列SRAM型FPGA的SelectMAP口读写时序如图7所示[21]。

图7 Virtex-5系列SRAM型FPGA SelectMAP口读写时序图(8比特模式)[21]

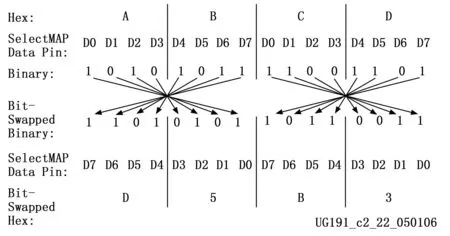

需要注意的是,从FLASH中读取的位流文件再写给SelectMAP口时,应该先进行高低位交换,如图8所示。即以8比特为单位,将D0位赋给D7位,D1位赋给D6位,以此类推,D7位赋给D0位。

图8 SelectMAP口配置数据高低位交换说明[21]

1.4 单粒子效应检测装置搭建

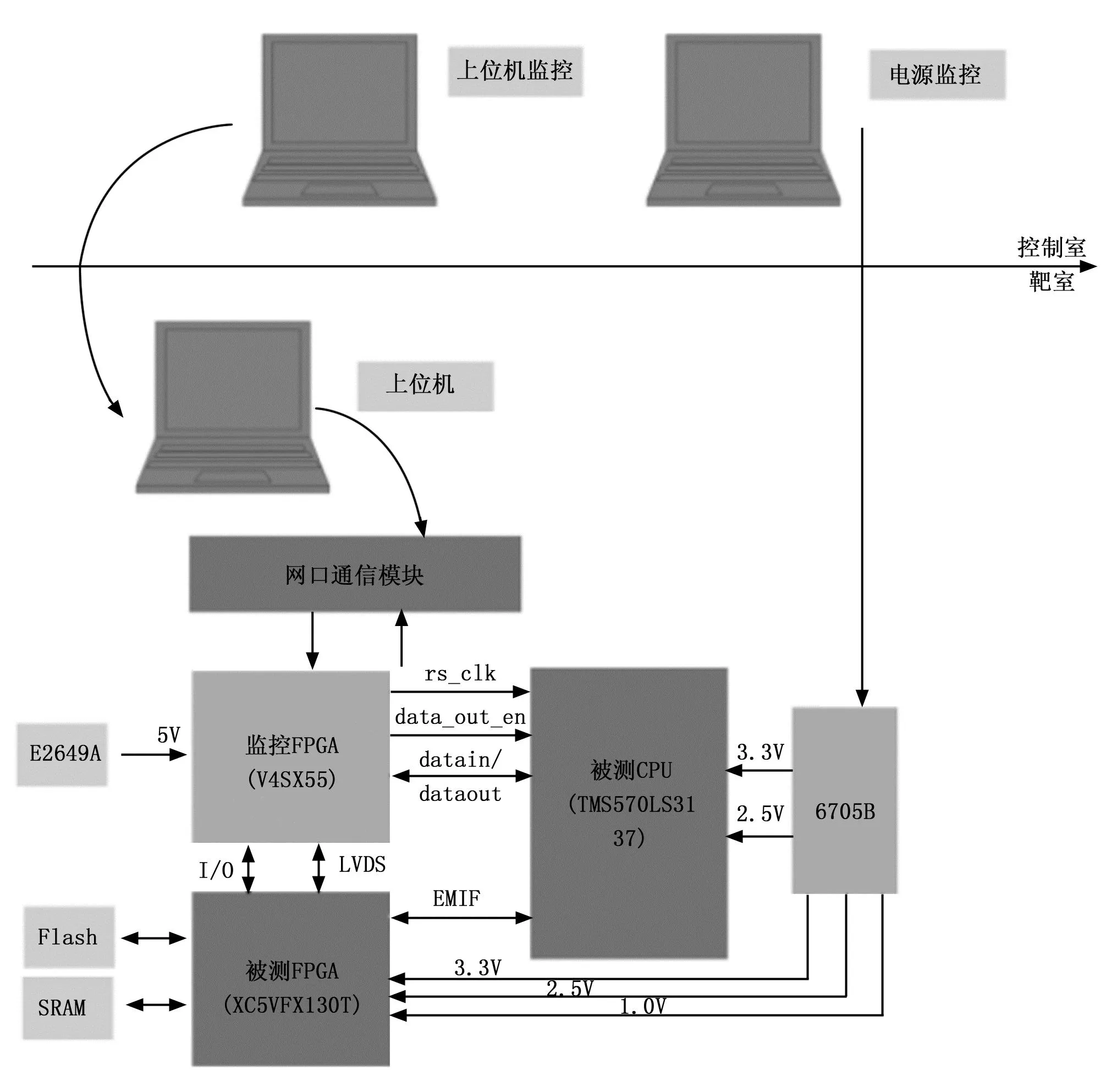

辐照试验时,单粒子效应测试系统搭建于设有高能重离子辐照终端的靶室内,试验人员通过位于控制室的两台笔记本对靶室内的上位机与桌面电源进行远程控制。试验装置连接关系如图9所示。试验系统搭建好后,束流终端利用红外线进行定位,将束流对准DUT且完全覆盖芯片。位于中国原子能科学院真空罐内的DUT如图10所示。整个试验中,粒子入射方向均采用垂直于样品方向,试验温度为室温。

图9 试验系统连接关系示意图

图10 真空罐中的被测FPGA芯片

1.5 单粒子效应测试方法

1.5.1 SEU测试方法

SEU测试的目标是检查被测器件中CRAM和BRAM的SEU响应,采用静态测试方法,即先对DUT加载配置文件,然后开始辐照。在辐照过程中,会关闭用户逻辑电路的工作时钟,并且复位信号一直有效,使用户逻辑电路处于静止状态,这样可以避免单粒子瞬态效应被电路捕获引入不真实的SEU。在辐照前,对被测器件进行回读并保存数据作为参考。当DUT结束辐照后,其状态会与初始状态进行比较,以获取静态翻转计数。

在FPGA配置完成后,将工作时钟暂停,然后对器件进行辐照,辐照量可以事先指定,或者直到出现需要停止辐照的条件。按照业界标准,本次试验结束的条件是总注量达到1×107个/cm2或者SEU次数达到1 000次。通常需要通过累积多次较短的辐照注量来达到试验结束条件,以避免导致停止辐照的条件提前出现。此外,当SEU数量达到一定程度导致芯片温度超过安全阈值或工作电流超过安全范围时,辐照过程就会被停止。

一旦束流关闭,就会向FPGA发送一个“捕获”命令,该命令将CRAM和BRAM的数据通过Select MAP口读出并发送至监控芯片。然后,监控芯片通过对比回读数据与初始数据来统计翻转数量。

1.5.2 SEF测试方法

在SEF测试中,采用动态测试来评估单粒子轰击对用户电路的实时影响。静态测试中被测器件处于静止状态并施加辐射,而动态测试则是在被测器件所加载的功能电路在正常工作过程中暴露于辐射之下。即在动态测试过程中,FPGA会以预定的工作时钟和输入数据进行操作。当重离子与FPGA相互作用时,可能引起功能电路发生SEF。动态测试以真实工况为条件,可以更真实地评估FPGA功能电路对SEF的敏感性,达到识别潜在的单粒子翻转敏感电路和设计更健壮的错误检测和纠正机制的目的。

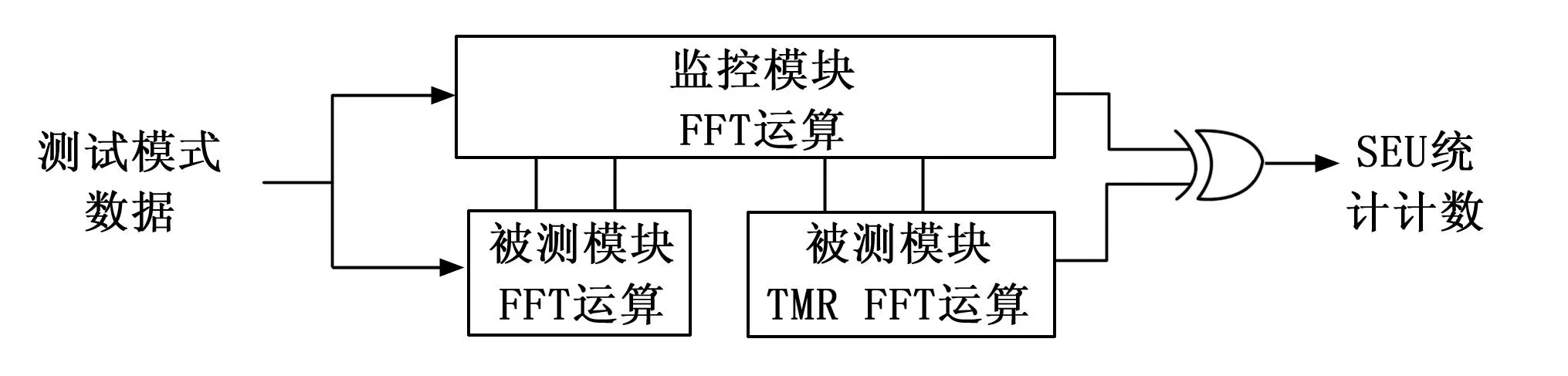

本次试验所采用的SEF的动态测试方法,具体是向DUT加载用户电路,并使用户电路处于工作状态,然后开始辐照,监测用户电路的输出数据,与预期结果进行对比和进行SEU次数统计。连续10秒输出数据持续错误时停止辐照,统计记录一次SEF。用户电路为输入数据宽度为32位,数据深度为32位的16384点FFT浮点运算模块。为同时对三模冗余加固效果进行评估,在DUT中还新增一组采用相同数据源和相同配置的三模冗余FFT运算模块。监控FPGA中实现相同配置的FFT浮点运算模块,与DUT中的运算结果进行对比。FFT测试电路结构如图11所示。

图11 FFT测试基本通道结构示意图

1.5.3 SEL测试方法

SEL的试验主要目的是为获取单粒子闩锁阈值,因此采用较大LET能量的Ta粒子作为辐射源。在测试中,向DUT加载典型配置程序使其处于正常的工作状态,其余设置参照SEF测试,需要额外增加程控电源对电流进行实时监控。为确保电流的增加是由SEL导致而不是由于SEU累计造成的电流功能异常,在观测到大电流后,先关闭辐射束流,然后进行重加载。

在本次试验中,发生SEL的判据为DUT的工作电流增大至正常工作电流的2倍,同时用户电路功能中断,且无法通过重加载恢复电路功能和正常电流,必须通过加断电来消除大电流。试验结束条件为总注量达到1×107个/cm2或者发生一次SEL。发生SEL后,需立即切断供电以保护器件不受大电流影响造成硬损伤。

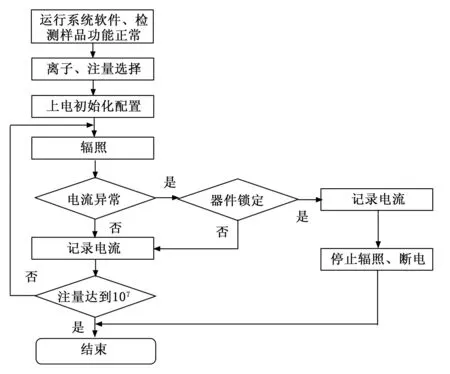

SEL测试流程如图12所示,具体流程如下:

图12 SEL测试流程图

图13 XC5VFX130T配置存储区威布尔拟合曲线及参数

1)选择粒子种类和注量率,对系统进行上电初始化配置;

2)运行典型功能程序;

3)开始辐照;

4)检测电流异常,判断器件是否闩锁(数值为正常电流的2倍值):如果否,跳转5);如果是,跳转6);

5)记录电流数值,并继续辐照至离子注量达到结束值,跳转7);

6)通过复位或重加载操作电流若可以恢复,则跳转至5),若无法恢复,则认为器件锁定,此时记录电流,停止辐照,并切断器件电源;

7)试验结束。

2 试验结果及分析

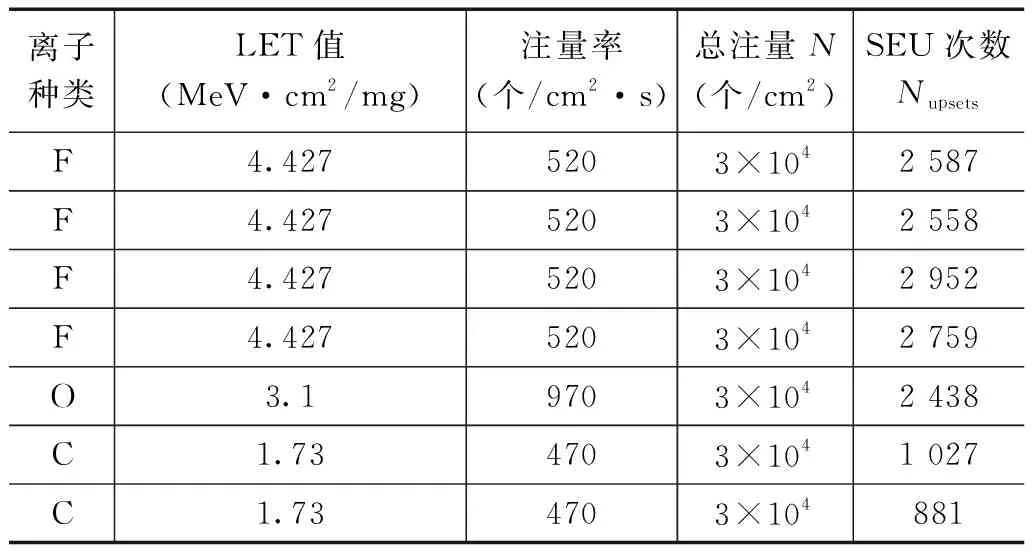

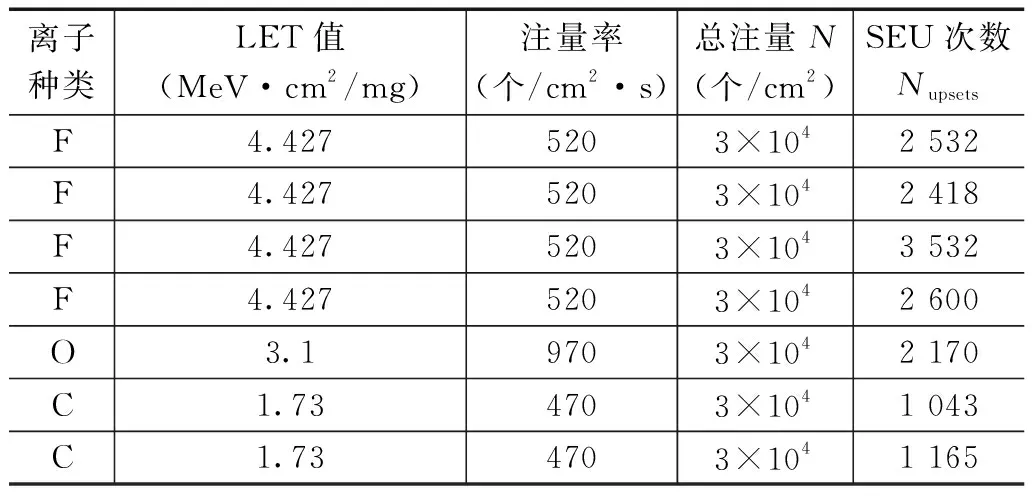

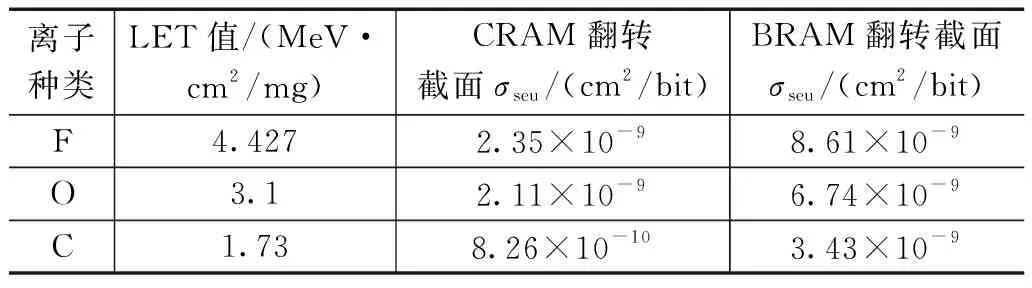

采用LET值为1.73~4.43 MeV·cm2/mg的C、O和F离子对器件进行SEU测试辐照。每个粒子辐照完成后,会利用SelectMap总线回读出当前待测FPGA的CRAM数据,并与原始配置比特文件进行对比,统计出有差异的数据个数,即为发生翻转的总次数。试验得到的CRAM及BRAM的SEU测试数据分别如表4和表5所示。

表4 XC5VFX130T配置存储器的SEU测试数据

表5 XC5VFX130T BRAM的SEU测试数据

为获取器件存储区在轨评估数据,需计算出重离子辐照下各类存储资源的单粒子翻转截面。CRAM与BRAM的每比特静态翻转截面σseu的计算公式如下:

σseu=Nupsets/(F·N·sinθ)

(2)

式中,Nupsets为SEU次数,即为试验中统计的各类存储资源的翻转数据结果;F为器件存储单元数量,该器件的CRAM数量为49 234 944个,BRAM单元数量为15 140 480个[20];N·sinθ为离子入射的有效总注量,其中,N为试验设定的辐射粒子源的总注量,倾角θ为入射离子束与器件平面的夹角,本试验为垂直入射,因此θ为90°。

按照公式(2)对CRAM与BRAM的SEU测试数据进行处理,可得到静态翻转截面数据如表6所示。

表6 CRAM与BRAM的静态翻转截面

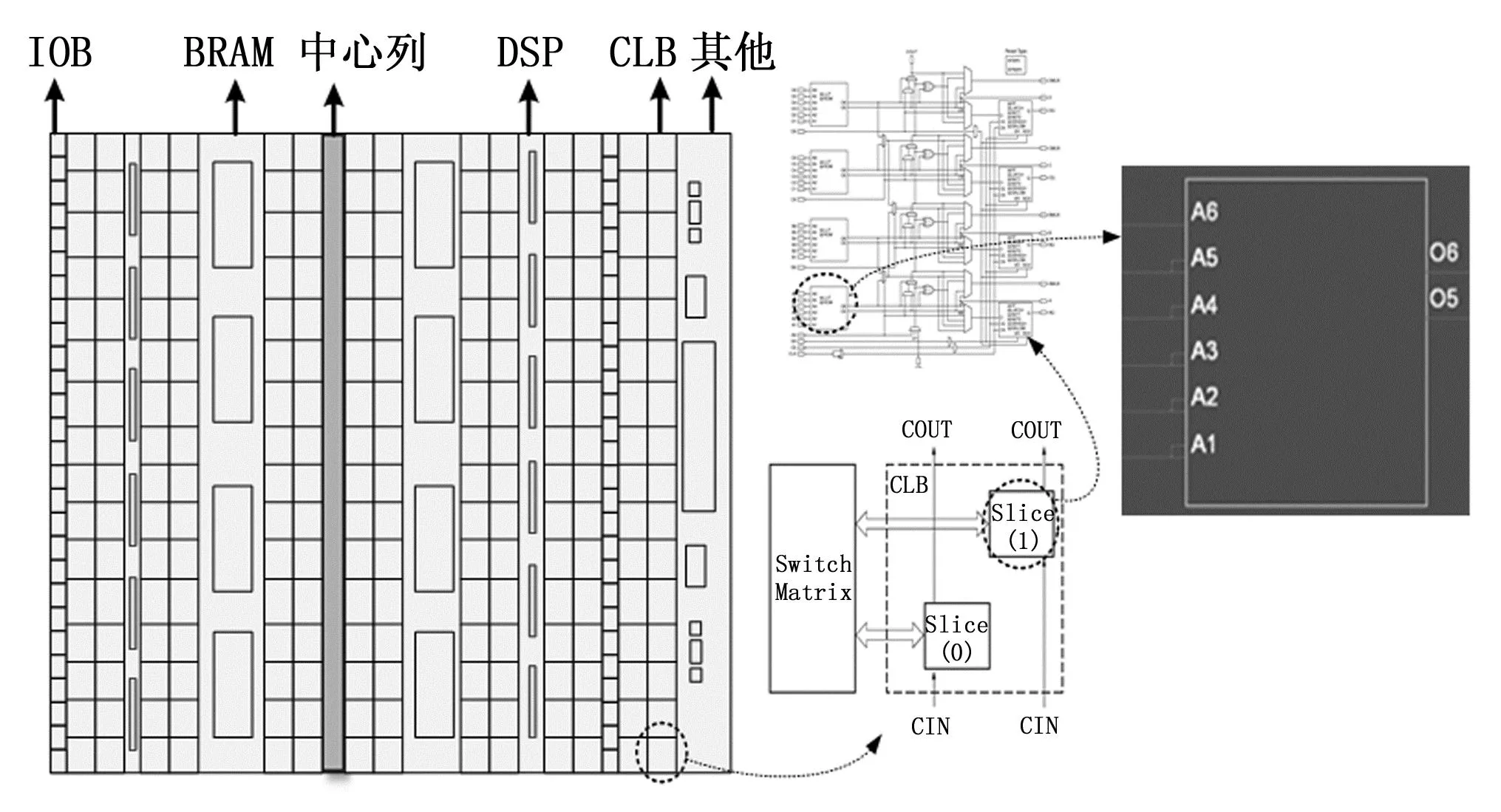

利用本试验获得的CRAM的SEU截面,结合文献[9]给出的饱和截面,进行韦布尔拟合,得到CRAM翻转截面与LET值的拟合曲线如图12所示。其中,韦布尔曲线的关键表征参数为:饱和截面为1.13×10-7cm2/bit,翻转LET阈值为0.5 MeV·cm2/mg,形状参数W为15.97 MeV·cm2/mg,指数参数S(无量纲)为2.193。以上数值与文献[18]所得数据量级一致,进一步验证了本次试验所采用的方法有效且准确。

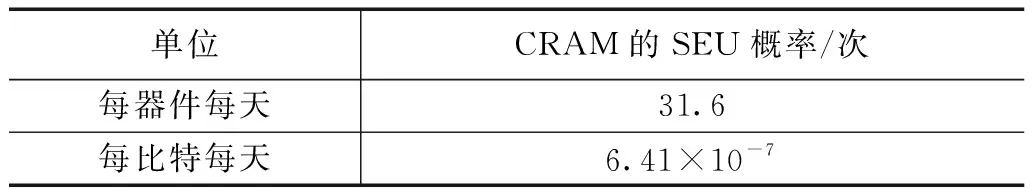

利用所得的韦布尔拟合参数和CREME96模型,使用空间环境模拟软件Omere对在轨翻转概率进行计算。结果如表7所示。轨道环境选择GEO轨道,太阳状态处于平静期(Solar min),屏蔽层为厚度100 mils的铝材料,计算结果为CRAM的SEU概率为6.41×10-7次/比特·天。该结果显示工业级器件的CRAM翻转概率比宇航级器件低3个数量级,这进一步说明,COTs器件在空间应用时,必须重视单粒子翻转敏感性并对其采取多种类、有针对性的加固措施。

表7 XC5VFX130T配置存储器在轨翻转率(GEO,太阳平静期,100 mils铝屏蔽,CREME96)

SEF试验中被测器件加载的典型应用电路为FFT浮点运算。采用O粒子进行辐照,监测功能中断次数,并根据公式(2)计算得到典型应用电路的SEF截面。再利用公式(3)计算得到加固倍数。

(3)

式中,μ表示加固倍数,加固倍数越大,反映加固措施效果越好。σsef1表示加固前的典型电路SEF截面,σsef2表示加固后的典型电路SEF截面。

FFT浮点运算模块的SEF试验数据如表8所示。

表8 FFT浮点运算模块试验结果

FFT浮点运算模块的SEF截面为10-6量级,三模后SEF截面相对于三模前下降了22%,即仅采用三模措施时的加固效果为4.8倍。由于三模冗余是一种容错措施,可以屏蔽三模电路其中一模电路的单粒子翻转错误,但是随着单粒子翻转累积导致另外一模电路也发生错误,三模冗余电路将无法产生正确的判决结果,导致三模冗余措施失效。因此,三模冗余措施必须结合刷新措施一起使用。利用刷新措施及时纠正CRAM的SEU,避免SEU累积导致两模电路同时错误的情况发生。

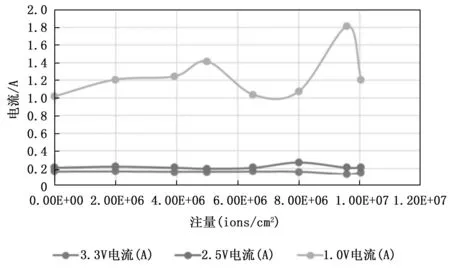

SEL试验采用LET值为81.35 MeV·cm2/mg的Ta离子对被测器件进行辐照,直到离子总注量达到1×107个/cm2。辐照过程中监测3.3 V、1.2 V和1.0 V电压域的电流变化情况,如图14所示。1.0 V为器件核压,其工作电流有异常增大现象,但电流没有达到正常工作电流的两倍,且电流到达1.8 A后迅速降至1.0 A。经分析该电流异常现象可能是由于单粒子翻转导致。试验数据表明该器件单粒子闩锁阈值大于81.35 MeV·cm2/mg。

图14 FPGA SEL试验过程电流变化图

3 结束语

Virtex-5系列FPGA采用65 nm工艺,经重粒子辐照试验验证,该系列器件的单粒子闩锁阈值大于81.35 MeV·cm2/mg,CRAM的SEU阈值小于1.73 MeV·cm2/mg,采用CREME96模型,考虑太阳平静期,100 mils铝屏蔽时,GEO轨道CRAM每比特翻转概率为6.41×10-7次/天,每器件翻转率为31.6次/天。试验结果表明该器件属于单粒子翻转敏感器件。本文对三模冗余措施的加固效果进行了评估,结果说明仅采用三模措施加固效果不明显,建议与刷新措施结合使用。