高功率1 550nm氧化限制型VCSEL设计与仿真

2024-01-29王伟谭云飞

王伟,谭云飞

(1 无锡学院 江苏省集成电路可靠性技术及检测系统工程研究中心,无锡 214105)

(2 南京信息工程大学 电子与信息工程学院,南京 210044)

0 引言

由于空间空穴燃烧(Spatial Hole Burning,SHB)和电流拥挤效应,有源层载流子分布不均匀,所以传统的垂直腔面发射激光器(Vertical-Cavity Surface-Emitting Lasers,VCSEL)一般都是多模激射[1]。考虑到多种激光应用场景都需要VCSEL 工作模式为单模,而在小口径芯片中引入氧化限制型结构,VCSEL 能实现单模输出,这是最常见且最有效的方法。同时合适的孔径会增大芯片的输出功率,降低阈值电流,所以受到了很多学者的青睐。氧化孔径约在3 μm 内时,可以实现单模输出。曾有文献阐述,小尺寸850 nm VCSE的氧化孔径小于3.5 μm 时,VCSEL 已经可以单模工作,且输出功率为4.8 mW[2]。2021年,HASSAN A M A 等展示了毫米级氧化物孔径的单模表面光栅VCSEL,可获得稳定单模工作并具有高光束质量,脉冲输出功率可达3 W,光束发散角为0.053°[3]。虽然氧化孔径缩小对于模式控制效果最直接,但同时该方案会带来较高的微分电阻,继而导致芯片发热,降低激光输出功率,而且过高的电流密度也会影响芯片的稳定性[4],大大缩短芯片的寿命。实际芯片的制备工艺想要很精确地控制孔径大小也很难,所以目前使用该方法制备该波段VCSEL 较少。

2022年,中国科学院长春光学精密机械与物理研究所首次报道了毫瓦量级出光功率的单横模1 550 nm波段VCSEL。VCSEL 的中心波长位于1 547.6 nm,工作温度为15 ℃时最高出光功率可达到2.6 mW,最高单模出光功率达到0.97 mW[5]。在此研究基础上,2023年该实验室又报道了连续输出功率超过1 W、脉冲输出功率超过10 W 的1 550 nm 波长VCSEL 阵列,通过分析每个单元VCSEL 的热阻特性,优化单元间距,最终VCSEL 阵列工作温度为15 ℃时,测得最高连续输出功率达到1.05 W;即使工作温度增加至65 ℃,VCSEL 最高连续输出功率仍能达到0.42 W[6]。

对于高功率VCSEL 来说,要提高其输出功率,势必要扩大其氧化孔径,而孔径的扩大会导致光束质量的降低,如何平衡两者的关系是目前需要探索的研究方向。2012年,中科院的刘迪等为了使VCSEL 具有较高输出功率,同时具备较好的光场质量,对具有不同氧化孔径的芯片进行了实验研究,得出由电流引起的自热效应给芯片带来温升的结论[7]。对于1 550 nm VCSEL 来说,合理的氧化孔径能够提高输出功率,同时将其与多结技术结合能够有效优化VCSEL 的输出特性,十分值得研究。本文通过建立单结和多结VCSEL 模型,结合不同氧化限制型结构,对不同氧化孔径与输出特性的关系进行仿真分析。

1 氧化限制型原理及模型建立

1.1 原理

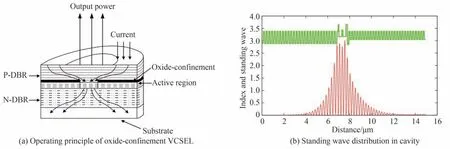

氧化限制型VCSEL 的横截面结构如图1(a)所示[8],VCSEL 的氧化限制层一般为含Al 量较高的AlGaAs 材料。芯片工作时,电流从顶部电极注入,受氧化层的限制注入于有源层中,之后辐合产生激光,激光被上下分布的布拉格反射器(Distributed Bragg Reflecter,DBR)反射,于是谐振腔中形成稳定的驻波,如图1(b)所示。

图1 氧化限制型VCSEL 工作原理及谐振腔内驻波与折射率分布Fig.1 Operating principle of oxide-confinement VCSEL & standing wave distribution pattern in cavity

IGA K 等曾在2013年对VCSEL 的关键光电参数如阈值电流与有源区的关系给出了简单的公式,VCSEL 的阈值电流和其他半导体激光器类似,其与有源区体积的关系式为[9]

式中,Ith表示阈值电流,Va表示有源区的体积。从式(1)可以看出,想要降低阈值电流可以考虑减小有源区体积,而VCSEL 的有源区可以看成是圆柱结构,所以减小体积就可以考虑缩短有源区的厚度。其实在使用多结结构堆叠或者增加芯片尺寸时,芯片的阈值电流会逐步增加,也是因为多个有源区级联之后导致其厚度增加,而恰好使用氧化限制的方法能够有效降低阈值电流,所以将两种技术结合将有望设计出高输出功率、高斜率效率、低阈值电流的VCSEL,这对于进一步优化多结1 550 nm 的VCSEL 芯片性能具有重要意义。

1.2 单结VCSEL 模型建立

研究者在设计氧化限制层时会考虑多个氧化层[10],以此为基础再分析氧化孔径对芯片输出特性的影响。图2所示的是根据理论模型设计的两种不同的氧化限制型VCSEL,图2(a)显示的是30 μm 单层氧化限制型芯片,其氧化层位于有源层和P-DBR 之间;图2(b)显示的是30 μm 双层氧化限制型芯片,在有源层和N-DBR 之间额外添加一层氧化层[11];图2(c)显示的是模型(a)电流注入的仿真结果,可以看到在模型的右侧(即芯片的外侧)出现部分空白,空白部分就是横向氧化限制,并且从仿真图中可以看出电流注入比较均匀,基本符合氧化限制型芯片的特征。这说明本文设计的氧化限制层参数比较合理,能有效限制芯片横向载流子运输,优化芯片的光电特性。

图2 单、双层氧化限制层VCSEL 建模及电流注入仿真图Fig.2 VCSEL models with different oxide-confinements & current injection simulation diagram

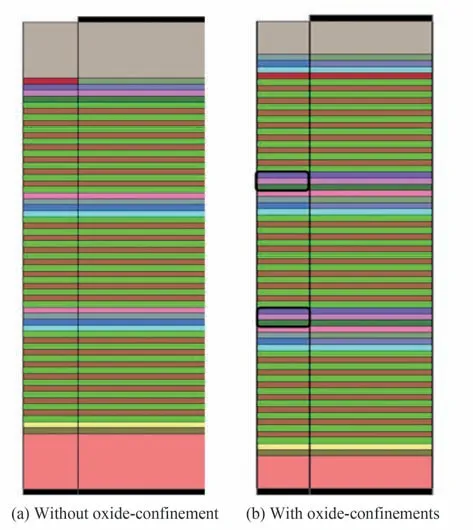

1.3 多结VCSEL 模型建立

在之前的工作中,已经设计并分析了不同结数的VCSEL 芯片,本小节以30 μm 三结VCSEL 为基础设计氧化限制层。多结芯片和单结芯片有所不同,因为多结是用有源区堆叠的方法实现的,意味着P、N 型空间限制层之间有多个有源区,所以有研究者在有源区与有源区之间增加氧化层[12]。图3 是三结芯片的氧化限制型结构图,图3(a)只有一层氧化层,图3(b)是在每两个有源区之间都添加了氧化层,两种结构依然通过调节腔长保证1 550 nm 波长激射。

图3 两种氧化限制结构的VCSEL 模型Fig.3 Two VCSEL models with oxide-confinement structures

2 仿真结果分析

以30 μm 单结VCSEL 芯片为研究切入点,首先根据其输出特性来分析两种氧化限制型结构以及不同氧化孔径的优劣,以此确定有源区与DBR 之间的氧化层位置、孔径和结构;其次研究输出特性相对理想的30 μm 三结VCSEL,并在有源区做多个氧化层设计,采用PICS3D 软件,仿真边界条件相同(芯片为顶发射,外加直流电压),根据结果对比两种氧化限制型结构VCSEL 的输出特性。

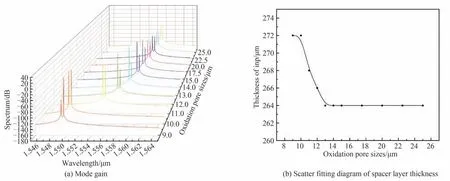

2.1 波长红移现象

在原有芯片基础上增加了氧化层之后,芯片的谐振腔会发生变化,并且在仿真不同氧化孔径VCSEL 的过程中发现,随着氧化孔径的增加,激射波长会红移。图4(a)所示的是不同氧化孔径下的模式增益,可以很清晰地看出,本文设计的芯片是多模芯片,其拥有两个纵向模式,并且随着氧化孔径从9 μm 增加至14 μm,芯片激射波长红移了约6.5 nm;而氧化孔径从14 μm 继续增加时,激射波长几乎不红移,这可能是因为氧化孔径增加带来的横模不变化,继而影响了纵模。对该现象采用调整两种结构的空间限制层厚度的方法来调整腔长,以实现最终激射波长在1 550 nm 附近。不同氧化孔径的InP 层厚度散点拟合如图4(b)所示,可以看到氧化孔径在8 μm 到14 μm 之间时变化十分明显,近似成线性;超过14 μm 之后空间限制层的厚度无需调整,这与图4(a)中的结果一一对应。

图4 不同氧化孔径VCSEL 的模式增益图及InP 厚度拟合Fig.4 Mode gain plot and InP thickness fitting plot of VCSEL with different oxidized aperture

2.2 单结氧化限制型VCSEL 输出特性分析

调节空间限制层厚度至VCSEL 激射波长在1 550 nm 附近后,对两种结构下的单结VCSEL 进行不同氧化孔径的仿真。仿真设置的边界条件均相同,所有芯片均为顶发射,温度设置为室温300 K,并外加直流电压,芯片的电流范围设置在0~0.08 A。如此设置是由于在仿真过程中发现氧化孔径较小时,芯片在电流增加过程中会出现结果难以收敛的情况,在实际测试中会表现为芯片工作电流有上限13]。不收敛有可能是由于存在多个氧化层,同时过小的氧化孔径会造成横向的光电限制效果过于强烈,导致功率下降。

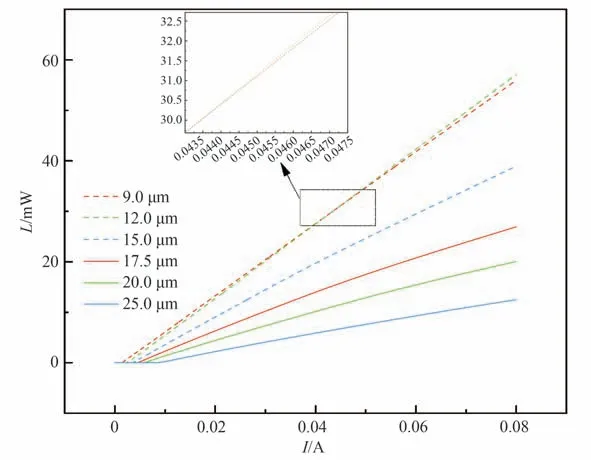

首先确定输出特性比较好的氧化孔径范围,以单层氧化层VCSEL 为例,分别设置氧化孔径为9 μm、12 μm、15 μm、17.5 μm、20 μm、25 μm 并进行仿真,仿真结果如图5所示。

图5 单层氧化限制层不同氧化孔径VCSEL 的I-L 图Fig.5 I-L plots of VCSEL with different oxidized apertures with single oxide-confinement layer

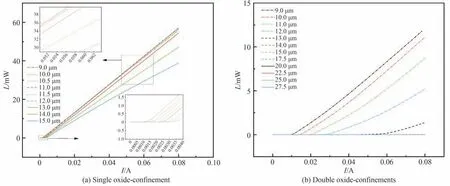

图中可以明显看出随着氧化孔径的增加,不仅阈值电流增加,芯片的输出功率随电流变化的下降幅度也十分明显,相对较好的孔径是9 μm 和12 μm,但是从二者的斜率效率(Slope Efficiency,SE)上比较,12 μm孔径的SE(0.72 W/A)略大于9 μm 孔径的SE(0.70 W/A),图中表现为功率增加幅度更大,二者约在43 mA处相交,但是阈值电流也比9 μm 孔径的约大了0.5 mA,所以在此处的氧化孔径上有必要增加一组仿真,来确定相对最合理的孔径。接着又仿真了氧化孔径为10 μm、10.5 μm、11 μm、11.5 μm、12 μm 的VCSEL,芯片输出功率如图6所示。

图6 10~12 μm 氧化孔径VCSEL 的I-L 图Fig.6 I-L diagram of VCSEL with an oxidized aperture of 10~12 μm

由于氧化孔径过于接近,在比较输出功率和阈值电流的时候可以参考图中局部放大的图片得到近似值:从各个曲线的趋势比较来看,氧化孔径为11 μm 时的芯片功率不仅最高,高达57.2 mW,而且斜率效率也更大;从阈值电流放大图来看,阈值电流从小到大依次约为0.75 mA(10 μm)、1.0 mA(11 μm)、1.5 mA(10.5 μm)、2.0 mA(11.5 μm 和12 μm),阈值电流的差距并不明显,这也是因为氧化孔径很接近。综合上述两点来看,氧化孔径为11 μm 的芯片输出特性较为理想,其实在实际操作过程中,这种氧化孔径不像仿真参数这么容易设定,会存在一定的误差,所以认为较为理想的氧化孔径为11 μm 也相对合理,这给实际的氧化过程带来了一定的容错率。

根据这个思路,用同样的方法对双层氧化限制层的芯片进行仿真,最终两种结构不同氧化孔径的输出功率随电流变化的情况如图7所示。图7(b)显示结果可以明显看出:双层氧化限制层的芯片输出特性十分不理想,输出功率最高的也只有11.79 mW(电流为78 mA 时的9 μm 氧化孔径芯片),斜率效率更是只有0.15 W/A。

图7 单、双层氧化限制VCSEL 输出功率与电流关系Fig.7 I-L plots of VCSEL with different oxide-confinements

与单层结构相比,本节提到的双层结构不仅输出功率和斜率效率十分低,而且阈值电流也十分大,最小都约为10 mA,可见这种结构的输出特性并不理想。根据仿真结果的分析比较,确定使用单层氧化限制层来设计氧化限制型VCSEL,该层位于P-DBR 和有源区之间,并且单、多结氧化限制型芯片的N-DBR 与有源区之间均不添加氧化层。

2.3 多结氧化限制型VCSEL 输出特性分析

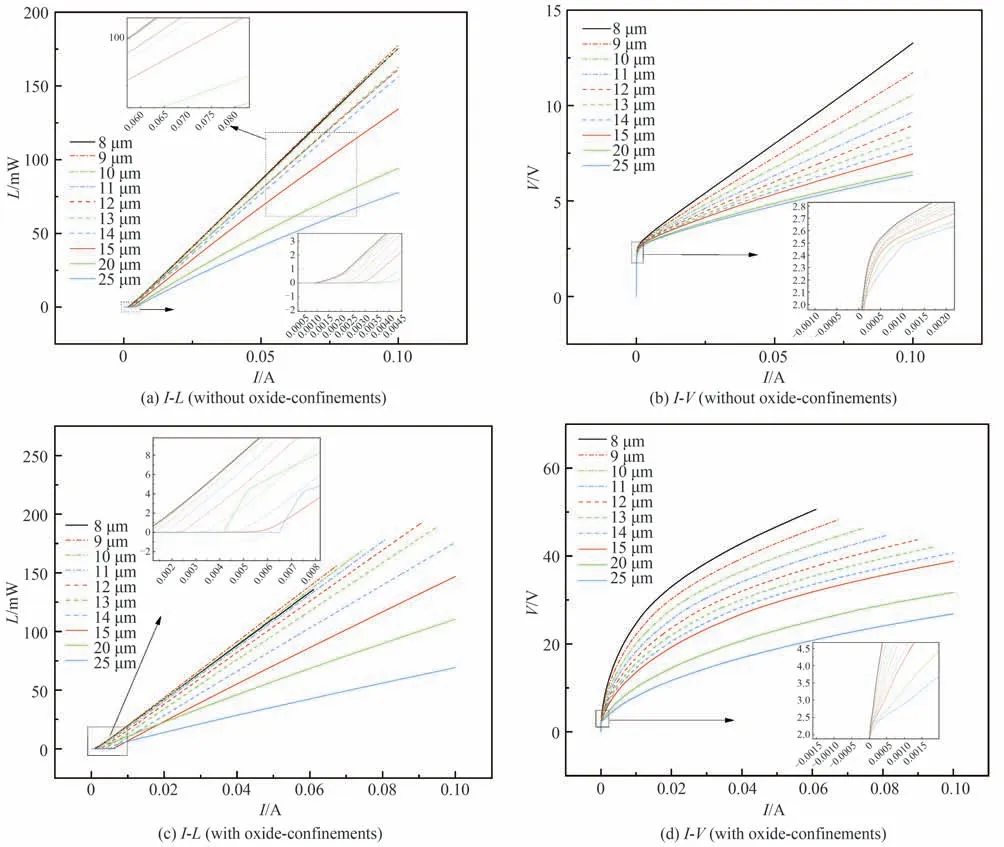

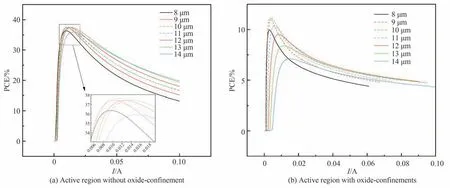

根据仿真结果绘制了两种结构的输出特性图,图8 为相同边界条件下不同氧化孔径VCSEL 的I-L与I-V曲线。最终对比结果表明在300 K 温度条件下,氧化孔径并不是越小越好,以二者的I-L曲线为例,均发现在氧化孔径为9 μm 时芯片的输出功率一直处于较高的水平,单层结构100 mA 时的输出功率约为177.55 mW,同时斜率效率也最高,约为1.79 W/A;多层结构由于提前出现功率翻转现象,9 μm 氧化孔径最高功率只有155.66 mA,但其斜率效率高达2.36 W/A。其实氧化孔径并非越小越好的现象也是因为电阻、热阻与氧化物孔径半径的平方成反比,过小的孔径容易带来过大的热损耗。

图8 有源区间有无氧化限制层芯片的I-L 和I-V 对比Fig.8 Comparison of L-L and I-V diagrams of chips with or without oxide-confinements in the active region

根据2.2 节的结论,本节没有继续细分孔径进行仿真。综合来看,氧化孔径9 μm 时芯片的输出特性较好。两种结构的I-L图对比可以看出,相同氧化孔径下多氧化层的VCSEL 输出功率和SE 比单氧化层的VCSEL 更高,但是从I-V图中也能发现,多氧化层结构的高功率通过数倍的外加电压实现。以9 μm 氧化孔径为例,50 mA 电流条件下二者的输出功率差距约为30 mW,随着电流增加,斜率效率会带来功率上更大的差距,但多氧化层结构的外加电压约为43.2 V,几乎是单层结构7.3 V 的6 倍。

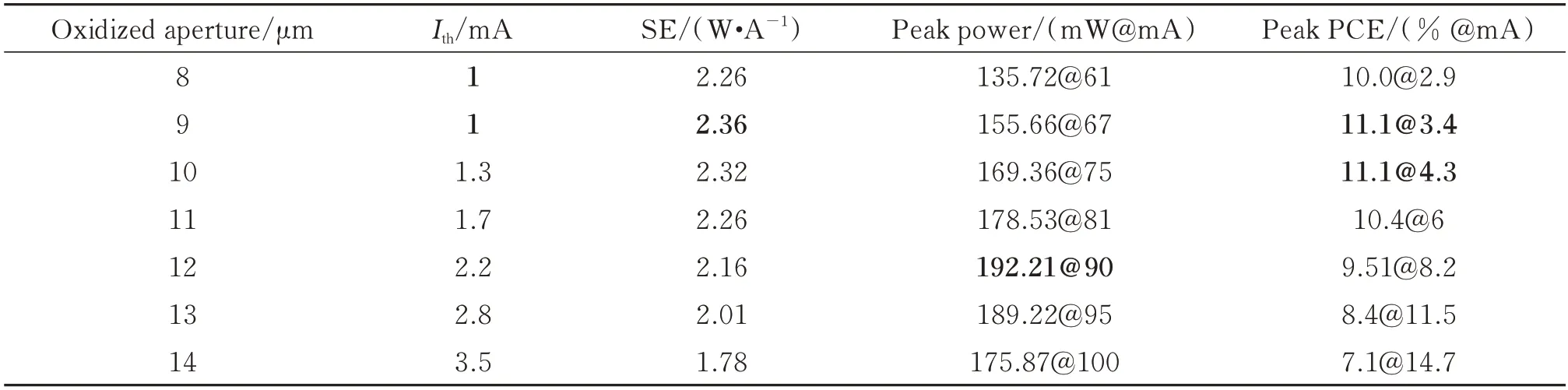

图9所示为不同氧化孔径VCSEL 的功率转换效率(Photoelectric Conversion Efficiency,PCE)曲线,还有部分芯片(VCSEL 的斜率效率和输出功率从氧化孔径15 μm 至25 μm 一直不理想,故未纳入计算和比较)对应的基本光电输出参数如表1、2所示。

表1 有源区之间无氧化层的VCSELTable 1 Active region without oxide-confinement

表2 有源区之间有氧化层的VCSELTable 2 Active region with oxide-confinements

图9 两种结构的光电转换效率对比Fig.9 Comparison of PCE between two structures

通过简单对比能看出,虽然本文提出的多氧化层结构能达到提升功率的目的,但是PCE 并不高,这也和外加电压过高有关。根据三结多氧化限制层的结构,隧道结上的氧化层(图3 黑框部分)对光子会发生本征吸收,限制光子运输[14];也可能是载流子在氧化层运输时能量有所损失[15]。所以相比单层氧化限制层,多层结构虽然输出功率相差无几,但是驱动电压需要数倍,效率降低。两种结构的PCE 随电流变化趋势接近,且9 μm、10 μm、11 μm 孔径的PCE 处于稍高水平,也验证了2.2 节的结论。同时两种结构的PCE 峰值差距明显,单结构10 μm 氧化孔径VCSEL 在电流11.4 mA 时达到37.7%的最高转换效率,而多层结构最高只有11.1 %,这其实并不理想。因此,这给VCSEL 的设计选择带来了新的思路,即适合需求的芯片很重要。例如当下最热的激光雷达技术,不仅对芯片的功率有所要求,还需要有较高的SE,使得脉冲电流驱动芯片时有更快的驱动速度;若是将VCSEL 芯片应用于3D 面部识别,由于有效距离较短,则不需要很高的输出功率,并且搭载在智能手机上的芯片需要较小的阈值电流和驱动电压。

3 结论

本文在高功率1 550 nm 的VCSEL 设计中引入了氧化限制型结构并对其不同氧化孔径条件下的输出特性进行仿真分析。以研究单结30 μm 氧化限制型1 550 nm VCSEL 为切入点,发现氧化孔径增加时激射波长有红移现象。对氧化孔径和InP 空间限制层关系数据拟合出曲线关系,发现氧化孔径从14 μm 继续增大时,激射波长几乎不红移;继而对不同氧化孔径进行仿真,并在10~12 μm 孔径附近细化尺寸仿真,得出单氧化层结构更有优势,相对理想氧化孔径为11 μm 的结论,此时单结30 μm VCSEL 的阈值电流约为1 mA,输出功率约为57.2 mW;按照同样的研究思路,对多结VCSEL 进行氧化限制设计,并且对是否要在有源区之间设计多层氧化层进行分析。最终发现两种结构均在9 μm 孔径时达到较高的输出特性水平,单层结构100 mA 时的输出功率约为177.55 mW,斜率效率高达1.79 W/A,最大功率转换效率为孔径为10 μm 时的37.7%;多层结构斜率效率更是高至2.36 W/A,但是多层结构有所缺陷,其转换效率相对于单层结构而言比较低,最高仅有11.1%。无论单结还是多结VCSEL,氧化孔径不是越小越好,这一点已经在PCE 分析中也有所体现。研究结果可为高功率1 550 nm VCSEL 的优化提供一定的参考。

致谢感谢Crosslight 公司给予软件PICS3D 试用的支持。