中红外硅基光波导的发展现状

2024-01-19冯露露胡祥建陈梦林

冯露露,冯 松,胡祥建,陈梦林,刘 勇,王 迪

(西安工程大学 理学院,陕西 西安 710084)

随着通信系统对高数据传输能力需求的日益增长,硅光子学在可见光和近红外(Near-Infrared,NIR)领域已经取得了较多的研究成果,但对中红外(MIR)领域的研究较少。MIR光谱范围为2.5~20.0 μm,硅光子学在MIR范围内具有潜在的应用前景,在波长为3~5 μm和8~12 μm范围内包含多个大气窗口[1],涵盖了较多化学和生物分子的强基础振动区以及分子指纹区(7~20 μm)。虽然分子振动可以发生在NIR和可见光区域,可以被先进的吸收光谱技术识别,但它们在MIR比在NIR和可见光区域强1 000倍,因为在这个波长范围内包含了几乎所有化学键的基本振动特征[2],使MIR波段适合的应用领域较广泛,例如生物传感器、医学监测、气体泄漏检测、片上红外传感器、发光二极管光源、激光器、光放大器、收发器和报警系统等[3]。

硅光子学中的基础无源器件是光波导,绝缘体上硅(SOI)是目前研究最多的应用平台。SOI平台光波导具有较多优点,包括复杂度低、光传输损耗低、加工产率高、成本低、机械及化学性能稳定,且与互补金属氧化物半导体(CMOS)工艺相兼容等,因此NIR波段的较多器件(例如低损耗波导、功率分配器、光栅耦合器、波分复用器、滤波器以及干涉仪等)已经在SOI平台上实现。与NIR相比,MIR硅光子学仍处于起步阶段。然而,硅的高折射率保证了高密度集成,与CMOS的兼容性可以实现低成本、大面积制造。此外,由于双光子吸收效应在MIR中可以忽略不计,因此它具有产生基于非线性光源的潜力。SOI在NIR硅光子学领域得到了广泛应用,由于在4 μm左右波长范围内,SOI波导氧化层(Buried Oxide,BOX)的强吸收限制了器件的工作波长,使MIR波段每一种光学功能都不能较好地实现。二氧化硅(SiO2)在大于3.6 μm波段的强吸收[4-5]限制了在该波长区域中的应用,使其他材料的异质集成逐渐发展,例如VI族与CMOS兼容的MIR透明介质。新的波导结构和制造技术也为MIR波段实现低成本、高密度、多功能的集成器件铺平了道路。这些研究技术被广泛应用于多个领域,例如通信网络、传感和非线性系统。同时,新材料和波导结构为MIR波导的研发提供了思路,但主要的挑战在于减少损耗和简化制造过程。

为了更好地对MIR波导进行研究,本文从波导材料和波导结构两个方面对不同工艺平台下的硅波导制备工艺以及其损耗等性能进行了分析。

1 中红外光波导材料

由于硅具有较高的折射率、较强的光学限制、较大的非线性以及与CMOS制造工艺的兼容性等优点,被广泛应用于光子学集成电路。SOI是目前研究较多的中红外应用平台,文献[6~7]指出微电子中常用的硅基材料,包括硅本身,不适用于波长超过8 μm的应用。虽然MIR集成光子学具有广泛的应用前景,但缺乏合适的MIR透明或低损耗光学芯和包层材料。近年来,研究者提出了SON、SOS、GOS、GOSI、SGOS、SOPS等MIR材料平台用来获得更长的波长。图1是几种材料浅色区为损耗小于2 dB·cm-1的波段。从图1中可以看出,在SiO2高损耗区域,蓝宝石、锗、氮化硅等材料都有取代的可能(浅色区为低损耗,深色区为高损耗)。

图1 中红外波段材料吸收特性Figure 1.Absorption characteristics of materials in mid-infrared band

1.1 SOI波导

SOI材料已被广泛应用于光电子集成电路(PIC)和光电集成电路(Opto-Electronic Integrated Circuit,OE-IC)。由于BOX在3 μm及4 μm以上表现出强吸收性[8],因此在MIR集成光子学中SOI不是较佳平台。文献[9]报道了一种具有较厚的Si层SOI波导。SOI的BOX厚度为2 μm,Si层的厚度为400 nm,在3.8 μm波长下,波导的损耗为3 dB·cm-1,在该波导的基础上设计了高性能平面凹光栅(Planar Concave Grating,PCG)和阵列波导光栅(Arrayed Waveguide Grating,AWG)[10-11]。文献[12]设计了一种高度为400 nm且宽度为1 600 nm的SOI条型波导,该结构以3.5 μm厚的BOX作为缓冲层,使泄露损耗小于0.01 dB·cm-1,SiO2的吸收损耗仅为3.4 dB·cm-1。该结构可用于设计和制备光学器件,例如气体传感器。该实验证明了更厚的波导可以拓展器件的工作波长范围,防止BOX对光波的强吸收,但该设计降低了器件的灵敏度和效率。

与标准波导结构相比,SOI槽波导可以提高间隙区域的电场振幅(可达50倍),从而在MIR硅光子学传感器中实现更高的灵敏度。文献[13]提出了一种SOI槽波导,在500 nm厚的Si层中刻蚀约80 nm的缝隙。在3.8 μm波长下,波导的损耗为2.6±0.24 dB·cm-1,传输损耗为1.4±0.2 dB·cm-1。通过热氧化使侧壁平滑,可以进一步降低界面损耗。槽波导是MIR传感的一种可行性选择,可支持在较长波长工作的材料平台上开发。文献[14]提出在全悬浮槽波导(Fully Suspended Slot Waveguide,FSSWG)平台基础上进行改进的方案。在2.2 μm波长下,将槽波导的传播损耗从7.9 dB·cm-1降低到2.8 dB·cm-1,弯曲损耗从0.76 dB·cm-1降低到0.15 dB·cm-1,槽波导环形谐振器的负载Q因子从1 650提高到8 550。

1.2 GOSI波导

硅的热光系数较大,导致器件性能对温度波动较为敏感。因此,若采用GOSI作为MIR波导平台,SOI基板中的氧化层可以作为一个隔离层来优化该问题。文献[15]报道了一种工作在3.682 μm波长下的GOSI波导,损耗约为8 dB·cm-1,实验证明了该结构可以实现具有低损耗MIR光子学结构。在后续工作中该实验通过采用快速热退火,提高了Ge的质量[16],从而进一步降低波导的传输损耗。当波长为3.682 μm时,波导的传输损耗为4 dB·cm-1。由于GOSI结构具有优异的热稳定性而且跟衬底具有电学隔离,GOSI波导利用厚底Si层来避免SiO2缓冲层的吸收。

1.3 SOS波导

蓝宝石的透明波段可以达到5.5 μm,由于SOS芯包层之间的折射率差较大,SOS有望成为MIR波导的理想材料。SOS制造工艺与SOI基本相似,通过化学气相沉积(Chemical Vapor Deposition,CVD)在蓝宝石基底上的外延生长,然后使用干法刻蚀在硅包层形成波导。到目前为止,实验证实了工作波长为2.75 μm[17]、4.50 μm[18-19]、5.18 μm[20]和5.5 μm[21]的SOS条波导。此外,在SOS上还实现了波长为2.75 μm[17]和4.5 μm[19]的光栅耦合器以及光子波长为4.50 μm[17]和5.5 μm[21]的环形谐振器等光学器件。文献[20]报道了在5.18 μm波长上测量出低波导传播损耗小于2 dB·cm-1。文献[19]通过使用抗蚀性回流,包括蚀刻、裂解和HF刻蚀循环和退火等后处理过程,实现了环谐振子的高固有Q因子(约278 000),且在4.5 μm的波长下TE模的传播损耗仅为0.74 dB·cm-1,改善了SOS波导的性能。然而,蓝宝石衬底在波长大于6.0 μm的波段也有较大损耗,完全蚀刻波导可以将波长从1.2 μm拓展到7.0 μm,并保持CMOS的兼容性。针对较长波长,可通过在MIR波段使用高透明的材料来进一步减少吸收损耗。

1.4 GOS波导

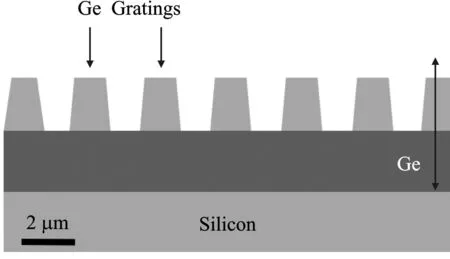

多数IV族光学器件都是在GOS平台上开发。文献[22]报道了采用活性离子刻蚀技术(Reactive Ion Etching,RIE)制备GOS波导。在硅衬底上镀2 μm厚锗层,条形波导的传输损耗低至2.5 dB·cm-1,半径为115 μm的弯曲损耗为0.12 dB。文献[23]采用反应离子刻蚀(RIE)和深反应离子刻蚀(Deep Reactive Ion Etching,DRIE)的波导刻蚀技术,以氯(Cl2)为刻蚀剂的活性离子刻蚀(RIE)和以六氟化硫(SF6)为刻蚀剂刻蚀(DRIE)制备了中红外GOS波导。

图2为刻蚀深度H为1.5 μm、光栅螺距为2 μm、占空比为0.5、工作波长为3.8 μm的单模传播的脊波导。图2(a)和图2(c)分别为RIE和DRIE刻蚀Ge波导光栅结构。图2(b)和图2(d)为刻蚀剖面图(刻蚀深度为H)。可以看出,DRIE刻蚀波导的侧壁轮廓基本垂直。在工作波长为3.8 μm时,RIE蚀刻波导的传播损耗为6.85 dB·cm-1,优化的DRIE蚀刻波导的传播损耗低于2.7 dB·cm-1。实验结果表明,利用光刻技术制作的波导,侧壁角度、粗糙度以及污染物等因素都会导致的器件损耗更高。

(a)

文献[24]设计了一种GOS脊波导,通过减压化学气相沉积方法在150 mm的硅片上外延生长4 μm厚的锗,经过循环退火工艺,用电子束光刻形成Ge波导,并在SF6和C4F8的混合刻蚀剂中刻蚀1 μm形成脊波导。在波长为8~11 μm时,器件的传播输损耗低于5.5 dB·cm-1。该实验证明了基于GOS的MIR波导工作波长可达11 μm,可适于8~13 μm大气窗口的传感应用。文献[25]设计了工作在4.7 μm波长下的GOS低损耗波导和7×8阵列波导光栅(Arrayed Waveguide Grating,AWG)。全刻蚀波导的传播损耗小于3 dB·cm-1,浅刻蚀波导的传播损耗小于1 dB·cm-1。

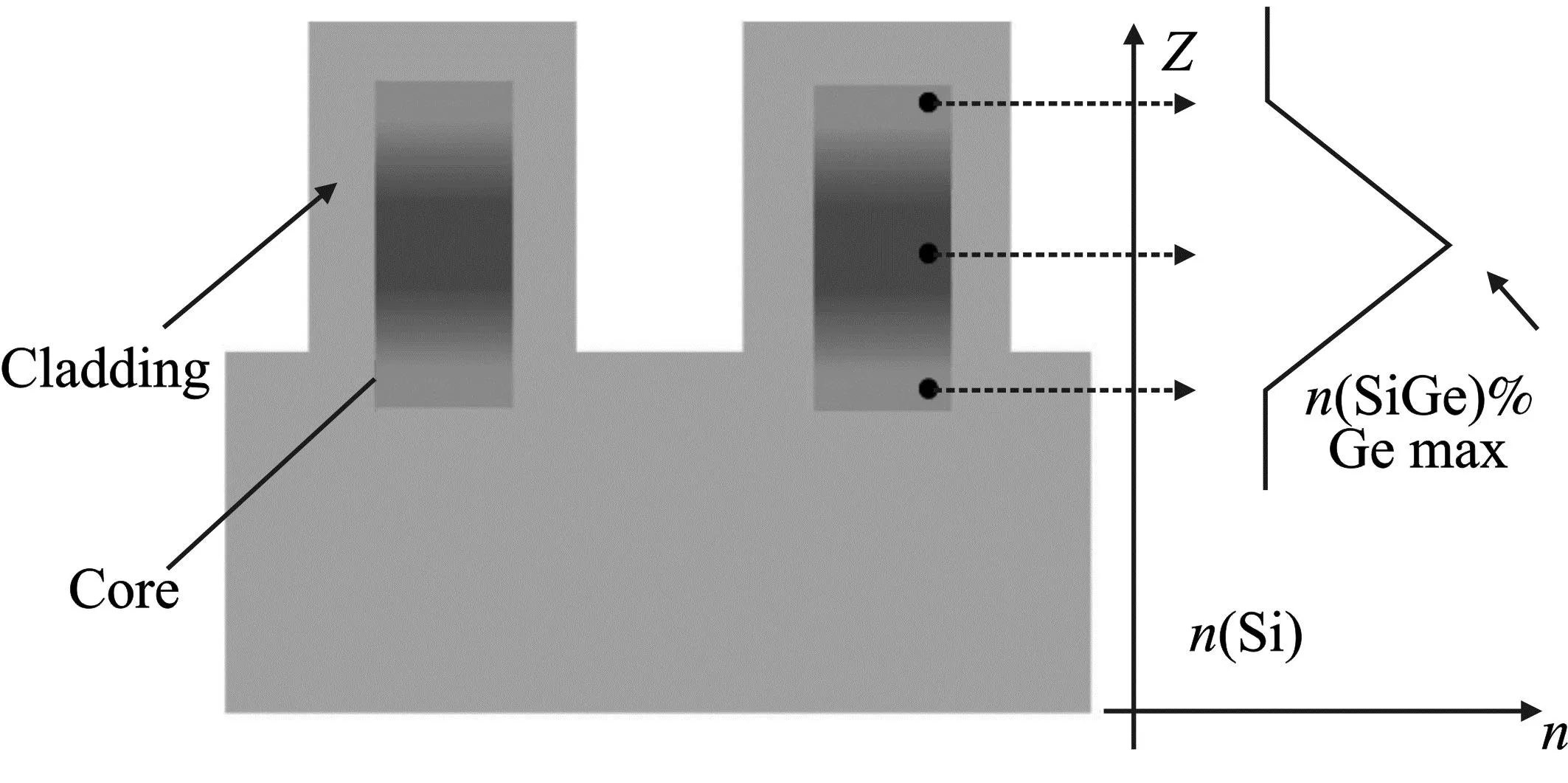

1.5 SGOS波导

目前,渐变SiGe波导在中红外集成光子平台具有广泛应用,表现出较高的透明度和较强的三阶非线性。锗和硅之间固有的晶格失配引入了较多缺陷,从而限制了光子器件的整体性能。文献[26~27]提出了一个具有厚外延硅基渐变SiGe波导的波导平台。如图3所示,Ge的浓度在0~40%之间,通过调整SiGe层的尺寸和厚度,该实验证明了该结构可以在较长的波长范围下工作。该波导具有8 μm宽的透明度范围,当波长为4.5 μm时,波导损耗低至1 dB·cm-1;当波长为7.4 μm时,波导损耗为2 dB·cm-1。与条型波导相同,波导损耗接近于理论值,波导横截面显示SiGe区域完全被外延硅包层覆盖,垂直方向上的强度分级与锗浓度的变化有关。文献[28]提出了一种在渐变SiGe衬底上沉积的Si20Ge80波导。该实验测量了在波长在5.5~8.5 μm范围内,仅为6 μm厚的富锗SiGe波导的传播损耗可低至2~3 dB·cm-1。

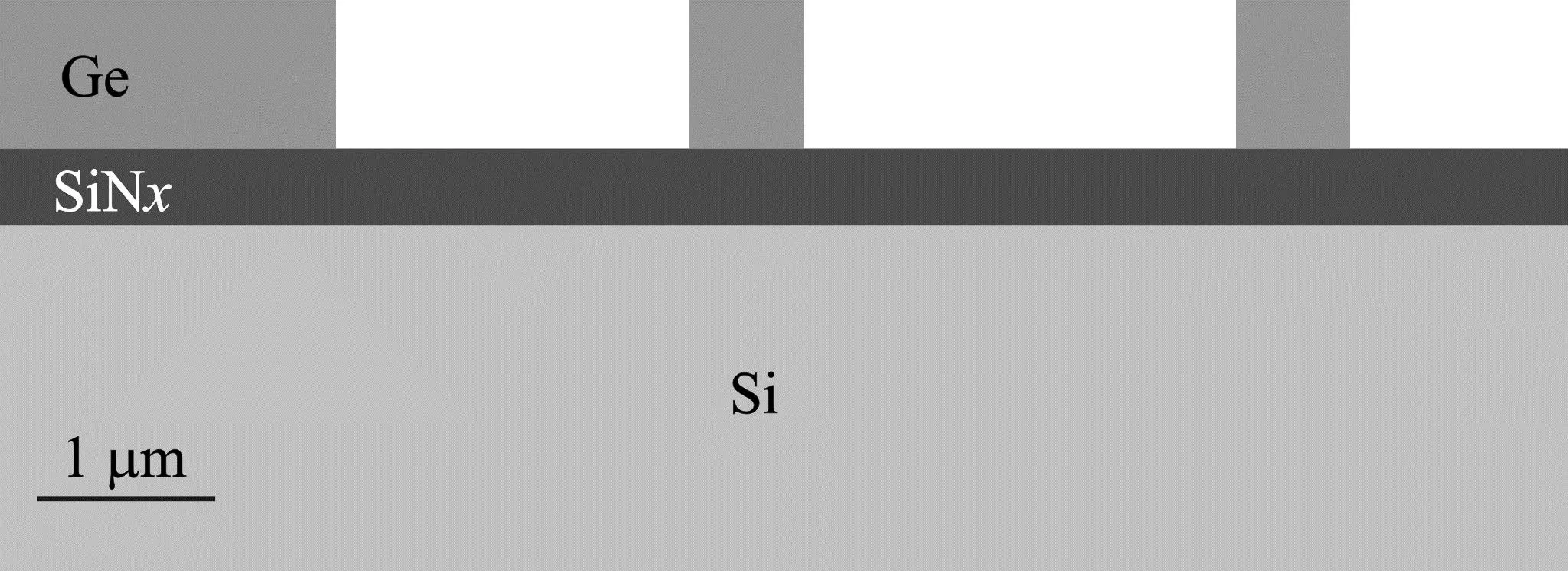

图3 SiGe波导波芯层蚀刻后截面Figure 3. Cross section after etching of SiGe waveguide wave core layer

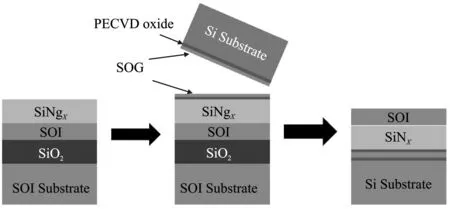

1.6 SON波导

Si3N4的折射率为2,该材料具有较高的光学非线性,并且在MIR非线性光的产生和芯片级生化传感的光子电路方面具有广泛应用。文献[29]通过沉积一个厚的Si3N4层并与另一个Si晶片键合,测量了制备的厚脊波导在波长为3.39 μm时,TE模和TM模的传播损耗分别为5.2±0.6 dB·cm-1和5.1±0.6 dB·cm-1。制备方法如图4所示,Si3N4上的Si脊波导具有高达7 μm的低损耗透射窗口,而且具有较低的反射系数,可以有效限制硅波导中的光场。因此在MIR波段,Si3N4取代SiO2作为覆盖层具有良好的应用前景,且基于SON波导的硅基器件能够在MIR范围内实现良好的带宽特性。文献[30]在2.0~5.4 μm的波长范围下,设计了具有5层的SON条型波导,并模拟了由此产生的2D和3D SON带隙等离子体模式。通过模拟在2.0~5.4 μm的波长范围内,具有Si/Si3N4/Si/Si3N4/Ag这5层波导结构的“带隙等离子体模式”,该实验得到了TM模在不同厚度的Si、Si3N4层的传输损耗,并最终得到具有5层SON波导结构的TM模的传输损耗为0.11±0.17 dB·cm-1,而5层的带隙等离子体波导TM模的传输损耗为0.07±0.16 dB·cm-1。

图4 氮化硅上的制造工艺Figure 4. Manufacturing process on silicon nitride

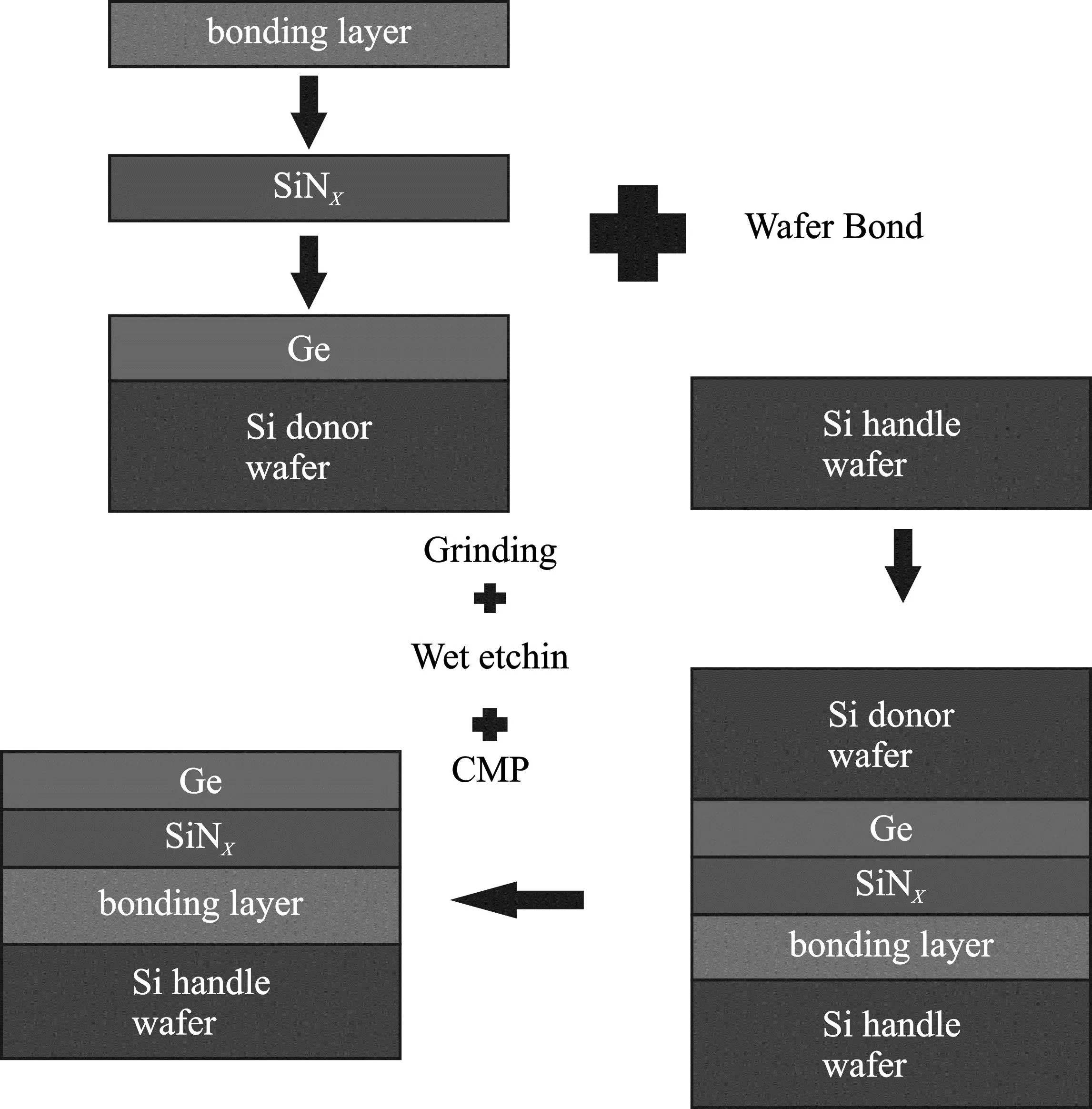

1.7 GON波导

异质Si/III-V光子学[31-33]是一个具有潜力的光子集成平台,其结合了Si和III-V平台的优点,在该平台上可实现多种高性能的无源和有源光学器件。文献[34~35]提出了一种在Si3N4上长Ge的GON波导。该实验证明了GON结构比Ge/Si堆叠结构更紧凑、折射率差值更大。工艺流程如图5所示,第1层是生长在Si上的Ge的外延层,Ge层上沉积了Si3N4,第2层是氧化硅晶片。键合后,第1片晶片上的Si衬底被去除,通过化学机械抛光(Chemico-Mechanical Polishing,CMP)去除Ge表面上的缺陷和Si/Ge混合层,提高了Ge层质量,另外需要抛光来调整Ge层最终的厚度。在半径为5 μm的器件上实现了0.14 dB·cm-1的弯曲损耗,并在3.8 μm波长下测量得到波导损耗为3.35 dB·cm-1,说明通过改进波导制造工艺可以进一步减少波导损耗。

图5 GON制作工艺流程Figure 5. GON production process

文献[36]在GON平台上制造了一个螺旋波导传感器。如图6所示,证明了在相同传播损耗下,GON比GOS平台具有更好的性能,这是因为GON在波长为3.73 μm时具有高折射率差(Δn=2.1),弯曲波导即使在小半径下也能实现低弯曲损耗。高折射率差使GON可以进一步拓展其工作波长。该实验设计了一种具有高倏逝场的GON波导,可以提高器件的灵敏度,实验中测量到丙酮中IPA(Isopropanol)浓度最低的GON为5%,GOS为16%,证明了在MIR传感应用平台使用GON的可行性。

图6 GON平台波导截面Figure 6.GON platform waveguide section

表1列出了近年来基于不同材料的中红外光波导的性能参数。由于中红外波长更长,因此适用于通信波段的220 nm SOI平台不再适用于中红外器件。使用400 nm和500 nm的SOI平台虽然拓展了MIR的传输范围,但随着用于隔离光模与基板的BOX越厚,该结构与微电子学不兼容。MIR SOI平台最低的传输损耗为3.4 dB·cm-1。SOS平台的优势在于机械支撑性的基底工艺复杂度低,衬底折射低,消除了衬底泄漏问题,缺点在于制备硬基底更具有挑战性。SON波导具有宽透明窗口、机械支撑型基板以及兼容性良好的特点,但是其需要晶片粘合和额外的基底制备工艺,缺乏商业用的基底。GOS具有较宽的透明窗口,且制造工艺简单,但缺点是Ge和Si之间大晶格失配、高表面粗糙度、高密度的螺纹位错、Ge和Si的折射率数差小以及瞬变传感灵敏度低。Si3N4波导具有宽透明窗、低损耗以及高折射率差等优点,易与其他光子结构结合,缺点在于其也需要晶片键合和衬底制备工艺,而且Si3N4和Si之间的晶格失配、表面粗糙度高以及位错密度高。渐变SiGe具有宽透明窗口和低线程的位错密度的优点,适用于光学模式限制和色散的柔性波导工程,缺点在于其要求缓冲层厚度大、制造成本高。对比不同的MIR材料平台中可以发现,在研究更长波段时,Ge波导可成为一个较热门的研究方向。从实验结果来看,富锗SiGe波导的低损耗也具有广阔的应用前景。

表1 不同材料平台的中红外光波导Table 1. Mid infrared waveguide of different material platforms

2 中红外光波导结构

SOI光子学的研究主要集中在通信波段,近年来陆续报道了较多关于MIR波段的研究。先前关于SOI的研究表明,具有较长工作波长范围的SOI波导易受到BOX的透明窗口的限制。为了避免该问题,除了使用一些其他替代材料,还可以实施波导工程来改进器件的结构。降低硅基波导传输损耗的另一种方法是去除底部包层的SiO2来创建悬浮波导。利用该方法可以扩展SOI平台的工作波长,并将Si的全透明窗口用于MIR波段。

2.1 SGOS波导多孔硅上硅波导

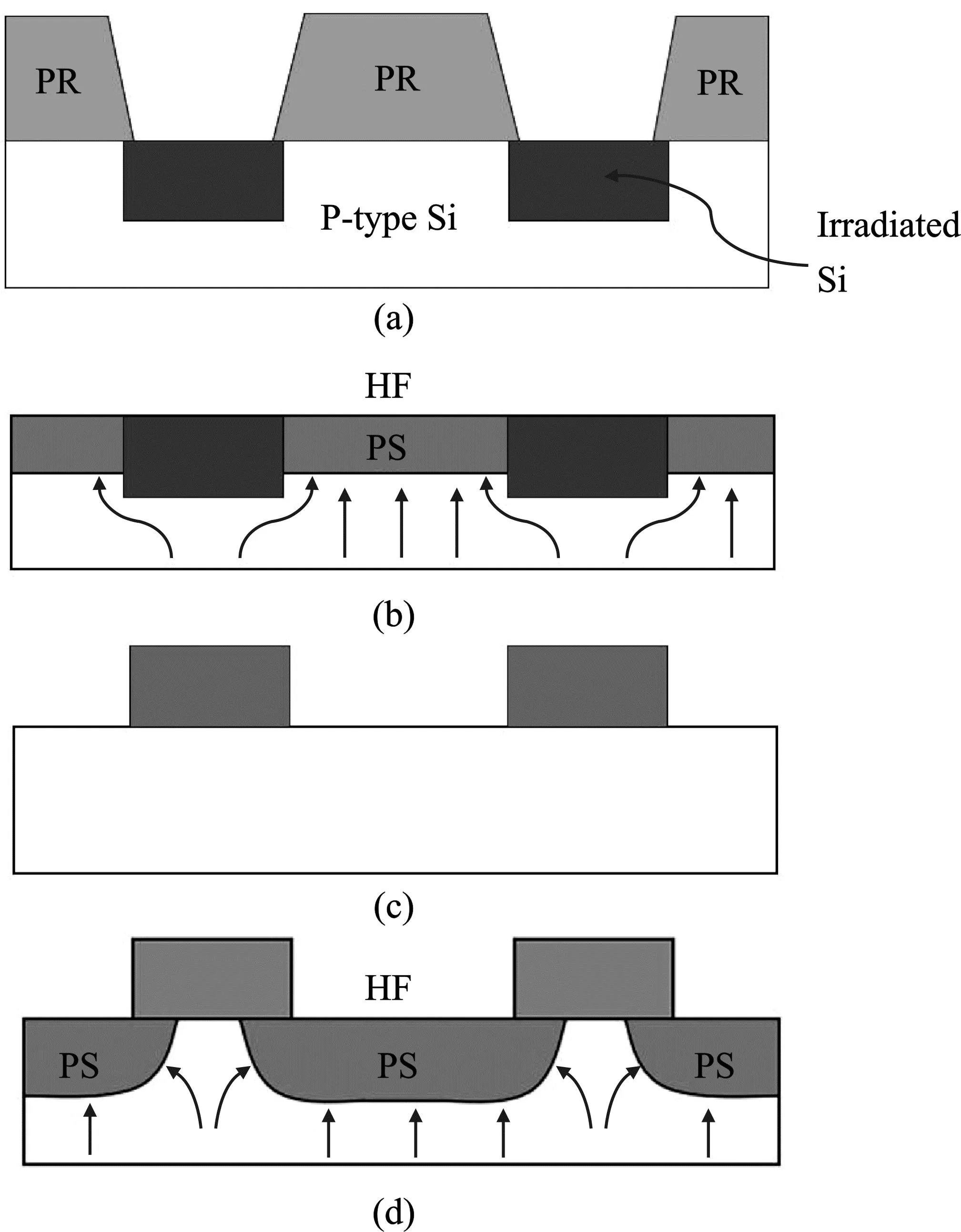

多孔硅上硅波导利用空气或多孔硅取代氧化物包层,工艺步骤如图7所示。文献[37]报道了一种工作在3.39 μm波长下,传输损耗为3.9 dB·cm-1的多孔硅上硅波导。传输损耗较高的原因可能是表面粗糙度和在其制造中使用了低电阻率的Si,可以通过对样品氧化从而减小传输损耗,使其值约为1 dB·cm-1。具体的工艺流程是在P型硅上沉积UV图案,进行辐照和掩模后在HF水溶液中进行电化学蚀刻,然后再进行多次刻蚀。

图7 硅在多孔硅波导制作过程(a)P型硅上沉积的UV图案(b)进行辐照和掩模后在HF水溶液中进行电化学蚀刻(c)样品浸入稀释的KOH溶液中除未辐照区域形成的剩余结构(d)在HF下进行二次电化学蚀刻Figure 7.Manufacturing process of silicon in the fabrication of porous silicon waveguide(a)The UV pattern deposited on P-type silicon (b)Electrochemical etching in HF aqueous solution after irradiation and mask (c)The sample is immersed in diluted KOH solution except for the remaining structure formed in the unirradiated region (d)Secondary electrochemically etched at HF

2.2 Undercut结构

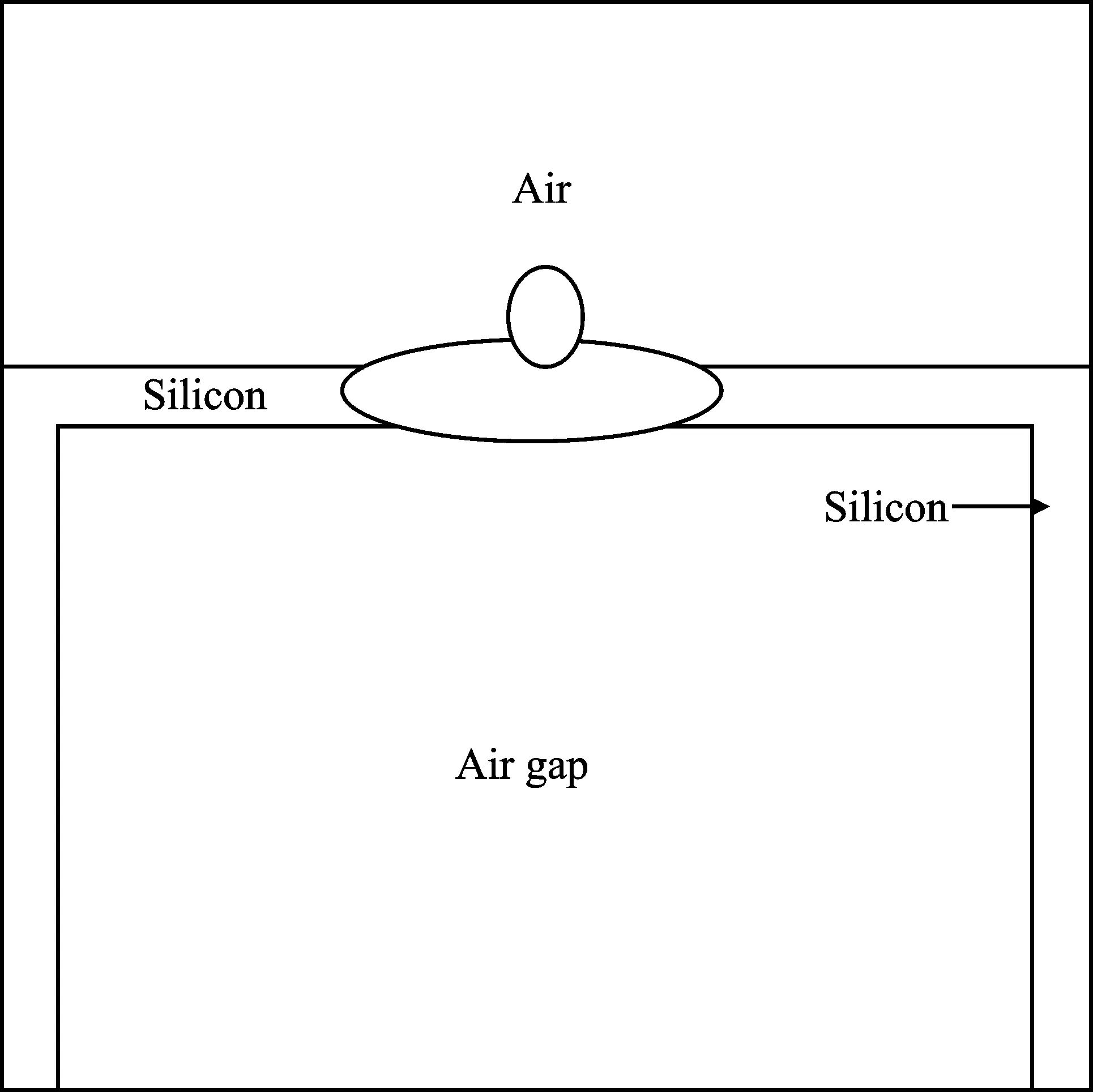

文献[38]提出了如图8所示的具有Undercut结构的LMIR波导。采用从波导背面去除SiO2衬底的方法来降低器件的传输损耗,实验测得该结构在波长为10.6 μm时的传输损耗依然较大,主要是由于硅在该波长已有6 dB·cm-1的损耗。在背面掏空时,由于波导背面均匀性不良引入了额外的损耗。该结构虽然能够降低损耗,但是背向刻蚀工艺难度大且器件较薄,易断裂。

图8 硅基带气隙的脊波导Figure 8. A silicon-based ridge waveguide with an air gap

2.3 Pedestal结构

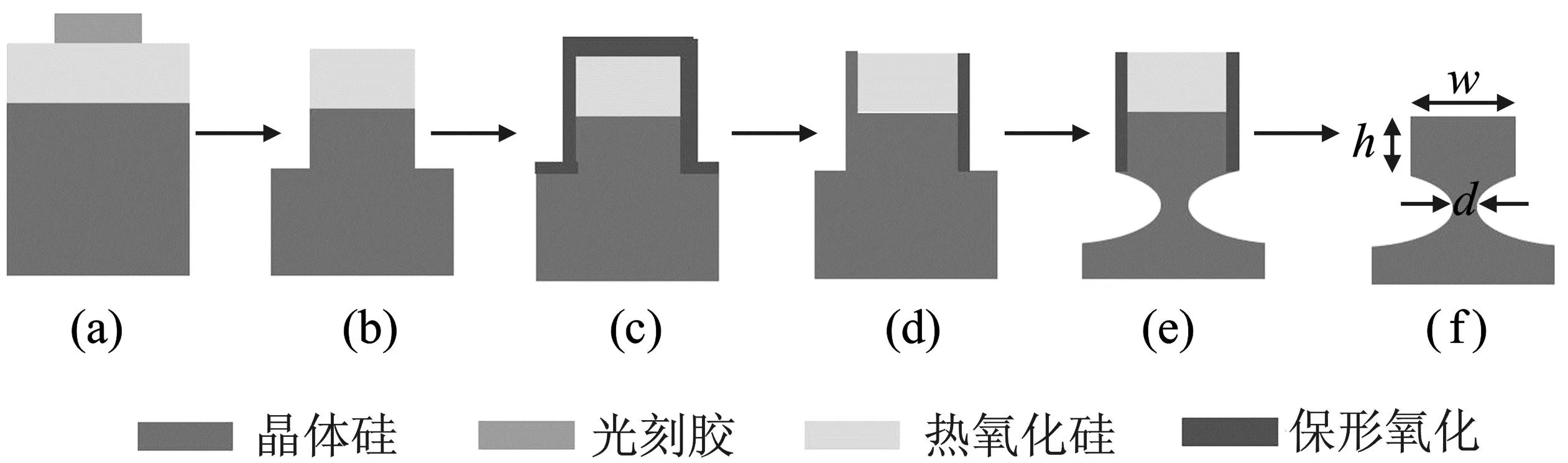

图9为硅支架结构(Silicon Pedestal)[39]的制作方法。通过掩膜将硅层侧壁向内刻蚀,形成一个具有硅支架支撑的硅波导,即衬底不再是SiO2,而是空气。实验测得在波长为3.7 μm时,传输损耗为2.7 dB·cm-1,在波长大于5 μm时,损耗相较于SiO2衬底可以减小10 dB·cm-1以上。

图9 Silicon Pedestal结构制造过程(a)采用光刻技术在硅片上生成波导和分束器的图形 (b)利用电感耦合等离子体反应离子蚀刻将图案依次转移到SiO2和Si层 (c)使用等离子体增强化学气相沉积在样品上沉积了一层薄的氧化层 (d)使用ICP-RIE蚀刻 (e)使用SF6气体刻蚀硅波导边缘 (f)用缓冲氧化物腐蚀移除氧化物Figure 9. Silicon Pedestal structure manufacturing process (a)Patterns of waveguide and splitter are generated on oxide-on-silicon wafer by photolithography (b)Patterns are transferred sequentially into SiO2 and Si layers using ICP-RIE (c)A thin oxide layer is conformally deposited on the sample using PECVD (d)Oxide isanisotropically and preferentially etched back using ICP-RIE (e)Undercut of silicon waveguide using SF6 gas as (f)Oxideisremoved by buffered oxide etch

基座波导由单晶Si和由HF刻蚀的SiO2基座组成。因为TE10模式在波导中间固有的弱光场在较大程度上可以减少SiO2衬底的吸收损耗,故基座波导中使用TE10模式来实现。

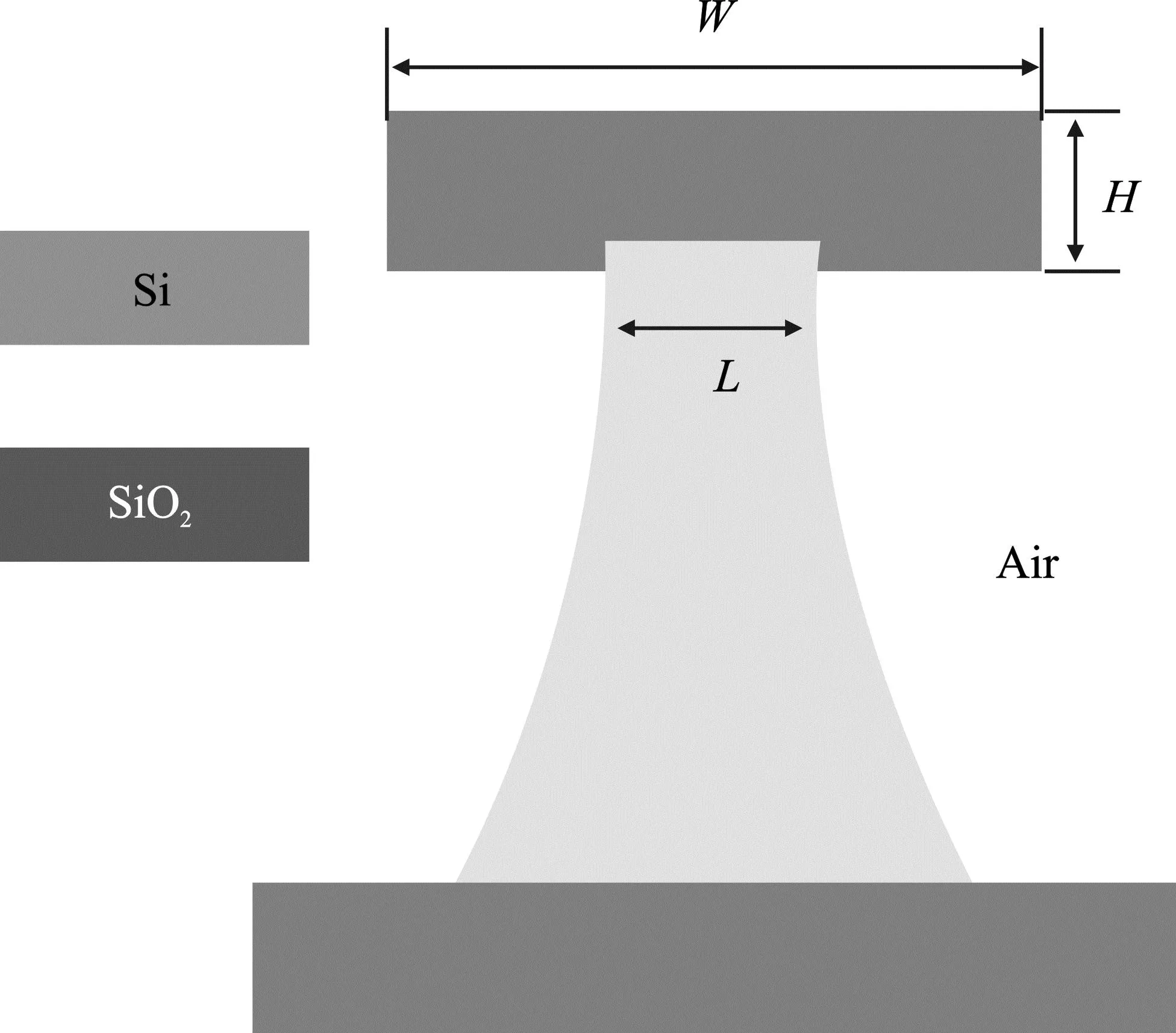

如图10所示,基片为3 μm厚的SiO2,低损耗基座波导由Si和SiO2基座组成。通过改变W、H和L等参数可实现低损耗传输。SiO2基座波导在4.8 μm处,TE00和TE10模式的传输损耗分别为0.170 dB·cm-1和0.024 dB·cm-1;在7.1 μm波长处则分别为4.85 dB·cm-1和0.53 dB·cm-1。与TE00模式相比,使用TE10模式可以减少波导的传输损耗。TE10模式可以激发波导中的基模,使耦合效率大于94%[40]。低传输损耗、高耦合效率和便于制造等优点使基座SOI器件在中红外波段的应用中具有广阔的应用前景。

图10 基座波导结构Figure 10. Base waveguide structure

图11 带空气包层的0.5 MeV质子freestanding结构横截面[41]Figure 11. Cross section of 0.5 MeV proton freestanding structure with air cladding[41]

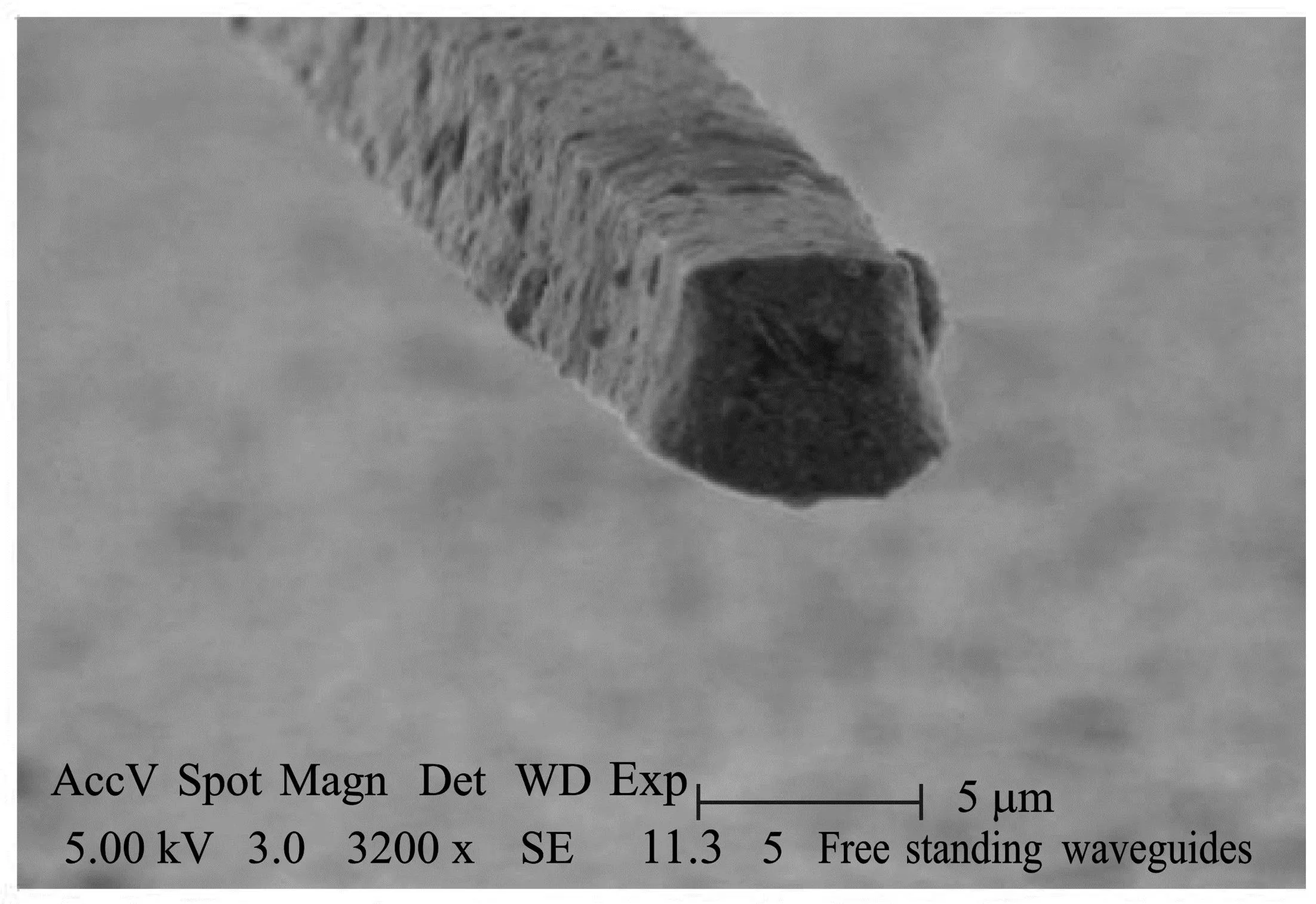

2.4 Freestanding结构

Freestanding结构的波导通过质子束直写(Proton Beam Writing,PBW)方法制作,其工艺步骤为:先通过0.5 MeV的高能质子束曝光来制备形成支撑区,再用较低能量的质子束曝光制备形成波导区,最后利用腐蚀液将其多余部分去掉形成悬浮波导结构。去掉高吸收损耗的SiO2后,波导周围都是空气,大幅减小了波导的传输损耗。文献[41]表明对于长10 nm的波导,只需要5个宽度为1 μm的支撑柱。实验测得波导的传输损耗为13~14 dB·cm-1,造成高损耗的原因主要是由于高能量的质子引起的缺陷和波导表面粗糙,可以通过热氧化和退火工艺的方法来解决该问题。

2.5 Suspended结构

文献[42]报道了一种工作波长为7.67 μm的悬浮波导结构,在TE模式下波导的传播损耗为3.1±0.3 dB·cm-1,这是首次报道的在7.67 μm波长下工作的低损耗硅波导。悬浮波导由亚波长光栅支撑,该光栅提供横向光学约束,同时允许进入BOX层,以便使用HF酸对其进行湿法刻蚀处理。使用亚波长光栅概念设计的悬浮硅波导可以在硅的MIR透明窗口中使用,具有潜在的传感应用前景。文献[43]开发了工作在MIR波长下的悬浮硅波导,其可以覆盖硅的全透明窗口(最高可达8 μm波长),该平台在分子指纹区传感领域具有广阔的应用前景。实验测得在3.8 μm波长工作时,该波导的传输损耗仅为0.82 dB·cm-1,而在7.7 μm工作时传输损耗高达3.1 dB·cm-1。基于SOI材料的悬浮脊波导通过HF酸溶液腐蚀掉波导正下方的BOX,消除了BOX的影响,使SOI材料的低损耗工作波长覆盖到MIR和远红外波段(25~200 μm)。

文献[44]提出了一种横向悬浮光栅硅波导。由于硅层覆盖了整个波导,并且孔洞更接近波导芯层,所以当光与物质之间相互作用时,该结构更加稳定,更适用于传感。实验测得在7.7 μm波长下横向光栅悬浮Si波导的传输损耗低至0.8 dB·cm-1,弯曲损耗为20.005 dB·cm-1。图12(a)为基于GOS的悬浮波导,图12(b)为基于Ge-on-SOI (GOSI)的悬浮波导。GOS悬浮脊波导的一个标准方法是在GOS上创建一个脊波导,在其周围蚀刻孔,使用四甲基氢氧化铵(Tetramethy lammonium Hydroxide,TMAH)去除下面的Si。悬浮GOSI波导采用改进的方法,首先通过减压化学气相沉积(Reduced Pressure Chemical Vapor Deposition,RPCVD)在薄的SOI晶片上生长Ge;然后通过光刻形成Ge波导在脊两侧蚀刻出孔;最后使用HF和TMAH分别去除SiO2和薄Si层。所制作的基于GOSI衬底的悬浮脊波导在7.7 μm波长下的损耗为2.65 dB·cm-1。

(a)

2.6 LOCOS结构

文献[37]设计制备了LOCOS结构的波导,如图13所示。起始材料为p型晶片,用热氧化法对晶片进行薄化,然后在缓冲HF中蚀刻,将1 500 nm厚覆盖层厚度降低到650 nm左右。采用CVD沉积40 nm的SiO2层和80 nm的Si3N4掩膜层,然后通过光刻和等离子体刻蚀Si3N4层,采用湿刻蚀后,在未掩膜的沟槽区域产生410 nm厚的SiO2层。最后,去除Si3N4层,在氧化沟道间留下光波导。工作波长为3.39 μm时,波导的传输损耗为1.4 dB·cm-1。

图13 LOCOS波导结构Figure 13. LOCOS waveguide structure

2.7 等离子体结构

通过高掺杂硅可以实现可调谐性等离子体共振。由于等离子体器件在较长波长下具有低损耗的优点,等离子体和Ⅳ族材料的结合具有广阔的应用前景。将等离子体波导器件的截面尺寸降低到亚波长范围可以进一步降低传输损耗,从而为波导放大器、多波长光源等有源器件的片上集成提供了可能性。文献[45]对掺杂硅在MIR范围内制备的各种新型波导进行了详细研究,发现波导在MIR中具有纳米级约束的等离子体模式。使用如图14(a)所示的槽结构和如图14(b)所示的矩形壳结构“挤压”模场实现长距离传播。在这两种结构中,光都被限制在波导之间的间隙中。相比于传统的全内反射波导,槽和矩形结构在MIR波段具有良好的应用前景,槽波导和矩形波导分别提供的一维约束和二维约束使这些结构成为传感应用的理想选择。此外,对缝隙和矩形波导的色散研究显示出负色散区,利用该区域可为超导材料应用、特殊传输以及慢光和快光等应用提供思路。

(a)

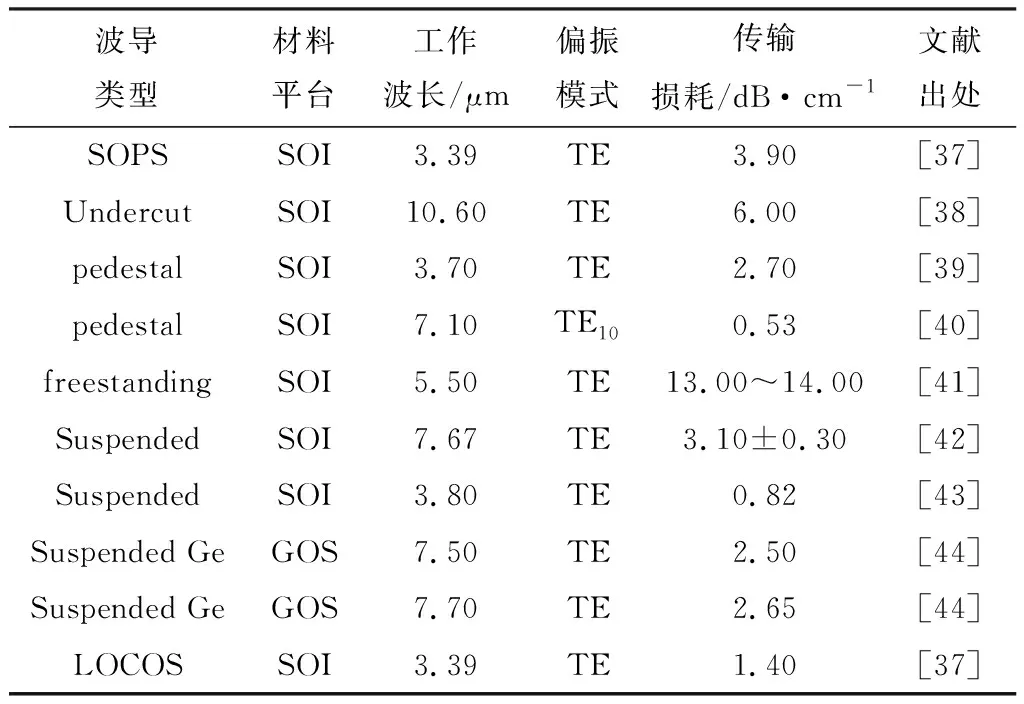

表2为基于不同结构平台的中红外光波导的性能参数。SOI悬浮脊波导与传统光子结构具有良好的兼容性,但机械稳定性差,透明窗口受光栅效应和横向泄漏的限制,需要额外的蚀刻工艺。SOI亚波长光栅波导结构紧凑,需要蚀刻波导结构,但是该结构的几何形状受到稳定性限制,透明度窗口受到光栅效应和横向泄漏限制。基座波导便宜且易获得基底强光学约束,但是几何设计灵活性差,且存在与传统光子结构的不兼容性。通过不同MIR结构平台可以发现,当去除部分SiO2时,硅波导结构的改变进一步拓宽MIR波长的应用范围,增加了设计难度和制造复杂度,从而限制了MIR波长的实际应用范围。

表2 不同结构平台的中红外光波导Table 2. Mid infrared waveguides of different structure platforms

3 结束语

本文综述了国内外近年来对MIR波段的低损耗硅基光波导的制备工艺及其损耗的研究进展。MIR硅基光波导具有广阔的应用前景, SOI技术作为低成本的硅晶膜具有的重要作用。此外,晶体硅具有稳定性、高光学非线性、易于加工和低成本等优点,其能够在其他基底(SOS、GOS、GOSI、SOS、GOS、SGOS、SON、SON)上取得成功,以适应更广泛的波长,材料平台覆盖的波长范围为2.2~11 μm。另一方面,几何形状的波导已经发展成为许多悬浮结构,例如SGOS、Undercut、Pedestal、Freestanding、Suspended、LOCOS,其工作波长大多在3~7 μm,其性能可能受到侧壁粗糙度或光刻缺陷限制。更厚的波导可以增加MIR工作带宽,防止传输的光波与包层的相互作用,但这会降低器件的灵敏度和效率。由于中红外波段硅基光波导材料本身的局限性以及工艺制造等方面仍面临较多问题,因此需要建立更好的波导工程和制造工艺。在MIR波段范围内,这些平台上的基本光子组件具有广阔的发展前景,但高密度集成和多功能系统仍然是需要解决的问题。随着电信领域的光子电路日益复杂,在实际应用中,MIR硅光子学平台的广泛应用取决于该技术的复杂性以及低损耗性。在现有材料平台上,进一步提高器件性能,例如降低传播损耗、增加Q因子等,可以有效促进器件的集成密度从而获得更优异的性能。