先进制程芯片在轨飞行验证通用系统设计

2024-01-08王红霞刘鸿瑾张绍林马远航于薇薇付宝玲刘迎辉张雷浩

王红霞,刘鸿瑾,*,张绍林,,李 宾,徐 建,马远航,于薇薇,付宝玲,刘迎辉,邓 峥,张雷浩

(1.北京轩宇空间科技有限公司,北京 100104; 2.北京控制工程研究所; 3.中国空间技术研究院:北京 100094)

0 引言

空间环境充满来自各种高能粒子和射线的辐射,辐射效应可能导致某些航天器集成电路(IC)芯片的失效。并且随着IC 芯片进入纳米级体硅CMOS 先进制程节点后,总电离剂量(TID)效应对芯片的影响逐步降低,而单粒子效应(SEE)随制程技术节点的缩小越发明显[1]。研究表明,MOSFET的本征抗总剂量能力已经超过100 krad(Si)[2],而先进纳米级工艺芯片的单粒子翻转(SEU)阈值较低(≤0.5 MeV·cm2/mg),质子直接和非直接电离都可能导致此类芯片的SEU[3]。且随着IC 芯片尺寸的缩小,晶体管本征增益下降,电源电压降低,导致可用电压范围缩小,高精度、高线性国产宇航模拟集成电路设计难度骤升,在抗辐射加固、电路结构优化、版图设计质量提升和功耗降低等方面面临巨大挑战[4]。

在轨飞行验证是验证在空间环境下先进制程芯片适用性和可靠性的有效方法,是提高其技术成熟度、验证其地面抗辐射测评方法有效性的重要手段[5]。针对不同种类的芯片,若单独进行在轨飞行验证,会占用卫星平台大量资源,增加系统复杂性。因此,本文提出支持多任务的高可靠性、可更换模块的在轨飞行验证通用系统,来完成对多种类、多型号先进制程芯片的试验验证。

先进制程芯片在轨飞行验证通用系统旨在获取待试芯片在真实空间环境中的运行数据,对芯片开展空间环境适应性分析,进行辐射效应机理研究,以完善芯片的在轨使用策略,提高芯片的技术成熟度和空间应用可靠性。本文给出了该通用系统设计以及典型芯片在轨飞行验证结果。

1 任务要求

试验任务包括:

1)完成16 nm FinFET、28 nm 亿门级FPGA、高速DAC 等10 类20 余款国产芯片的在轨飞行验证,获取芯片的在轨飞行工作数据,开展芯片的空间适用性分析。

2)通过在轨飞行验证,开展芯片的空间应用故障模式和辐射效应机理研究,完善其在轨使用策略,推动国产先进制程芯片抗辐射加固技术的发展。

此外,系统应支持在轨软件升级和可重构系统设计,即通过航天员或机械臂在轨组装、更换试验单元功能模块以及故障诊断与处理,实现在轨任务升级与维护,定期开展芯片的宇航适应性验证。

2 系统总体设计

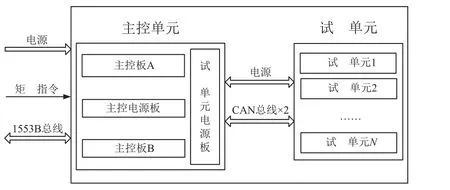

为满足在轨可重构、可升级维护的要求,先进制程芯片在轨飞行验证通用系统作为空间站搭载设备,基于“可更换模块”设计理念,采用“主控单元+试验单元”的架构,组成框图如图1 所示[6],主要技术指标如表1 所示。

表1 先进制程电子元器件在轨飞行验证通用系统主要技术指标Table 1 Specifications of the universal system for flight verification of advanced process chips

图1 先进制程芯片在轨飞行验证通用系统组成框图Fig.1 Block diagram of the universal system for flight verification of advanced process chips

主控单元作为系统控制的核心单元,为保证系统在轨运行的可靠性,选用抗辐射等级芯片,采取双冗余冷备份硬件设计及软件容错方案。主控单元对外通过1553B 外总线与数管系统进行通信,1553B 接口为经典冗余热备份设计,具有A、B 两条通道,在单通道故障情况下,可以将总线切换到另外一条通道上。主控单元与试验单元通过CAN内总线获取各个试验单元上待试芯片的在轨飞行试验数据。该系统充分利用CAN 总线的可扩展性,可将节点扩充至110 个,以方便航天员定期在轨更换试验单元模块,开展芯片的在轨适应性验证任务[7]。

试验单元相对独立,通过CAN 内总线与主控单元通信,其数量可灵活增减。各试验单元实时监测所搭载的待试芯片的在轨工作健康状态,并周期性上传至主控单元;主控单元对所有试验单元的待试元器件数据进行统一管理,并由1553B 总线下传至地面控制系统。每个试验单元均能完成十几款待试芯片的飞行验证工作。本系统搭载的各试验单元待试芯片分类如表2 所示。

本系统采用标准机、电、热接口,机箱为立式长方体,整个设备采用模块化设计,相邻两模块间通过耳片互连,具有良好的互换性。试验单元只需满足±12V 供电,两路CAN 总线传输,下行遥测速率小于200 byte/s,即可搭载于该平台上完成芯片验证。

在该系统的研制过程中,为确保验证的有效性,地面测试中对单板即整机均进行了高低温摸底试验,并与芯片设计厂商沟通,共同确定了各元器件的测试阈值和判据。

3 关键技术

3.1 主控单元容错设计

主控单元由主控单元电源板、主控板A、主控板B 和试验单元电源板组成,通过外部输入的直接指令实现当班单机电源的切换。主控单元管理单机内各试验单元健康状态并与数管系统进行数据交换,同时,接收数管系统发送的遥控指令、卫星轨道参数、星时数据等,采集验证系统所有试验单元中多款待试芯片的在轨飞行数据,并将遥测数据打包传送给数管系统,实现对待试芯片在轨工作状态的实时监测。

主控单元的逻辑功能与内外接口如图2 所示。

3.2 在轨可更换试验单元设计

试验单元统一采用“主控FPGA+待试器件”的硬件架构,主控FPGA 选用Flash 型A3PE3000,程序进行三模冗余(TMR)设计,保证主控FPGA 运行的可靠性。主控FPGA 配置存储、刷新芯片,上电后自动加载位流,每隔一段时间自动刷新位流,以确保主控芯片程序运行的可靠性。待试FPGA 中将80%的BRAM 配置成存储单元。

以试验单元A 为例,其组成框图如图3 所示[6]。采集到的28 nm 亿门级FPGA 在轨运行数据包括:

图3 试验单元A 硬件设计框图[6]Fig.3 Hardware design: block diagram of test unit A[6]

1)例化DDR3 控制器,28 nm 亿门级FPGA 负责将数据写入MRAM 存储器。然后连续读MRAM存储器内容并比较(当检测到错误时,需要再读一次MRAM 存储器并比较);如果第二次比较结果依然有错,则表示MRAM 存储器内数据发生SEU,否则认为数据通路发生SEU。

2)电流异常增大,功能失效,重配后电流没有恢复正常,电源复位后功能正常,则判定器件发生单粒子锁定(SEL)。

3)长时间在轨运行中,如电源复位后仍无法运行,则判定发生TID 效应导致功能失效。

测试结束后,通过CAN 总线将测试数据传给主控单元。最后通过遥测平台将数据下传到地面。

3.3 实时数据管理机制

验证系统的主控部分采用实时数据管理机制,由国产SpaceOS 星载操作系统管理各种主控单元资源,为应用软件提供多任务调度机制。应用软件的各项任务在系统软件的调度下并发运行而互不干扰。实时任务调度如表3 所示。新装载试验单元模块只要遵守主控单元的采样频率及遥测包格式要求,即可实现与主控单元通信的无缝对接。

表3 应用软件的任务列表Table 3 List of tasks for the application software

主控单元启动后,操作系统协调各任务有序执行。系统数据管理流程如图4 所示。

图4 系统数据管理流程图Fig.4 Flowchart of data management of the system

任务1:查询1553B 指令。主控处理器每90 ms 查询接收1 次数管系统发来的遥控指令,同时将遥控指令、空间站轨道参数、空间站数据等存到本机存储器。

任务2:任务分发。主控处理器解析1553B 遥控指令,转换为内总线指令。考虑到内总线指令的重要性,首先识别内总线指令的有效性,再将有效的内总线指令存储至指令接收链表中。

任务3:获取各试验单元数据。主控单元首先判断指令发送链表有无待发送给试验单元A 的有效指令:若有,则将有效指令通过内总线发送至试验单元A;试验单元A 将待试芯片的检测信息存储至本地后,按照总线协议,打包返给主控单元。若无,则依次判断后续试验单元发送指令链表内有无有效指令待发送,直至获取所有试验单元的待测元器件在轨检测数据。主控处理器对每个试验单元均设置2 组链表,包括1 个内总线指令发送链表和1 个内总线指令回复链表。在单个试验单元内,这2 个链表独立于其他试验单元,有效降低了试验单元间业务逻辑的耦合度。主控处理器对这2 个链表的管理包括系统启动自检后的创建链表,试验任务结束后的链表空间自动释放、异常指令剔除、试验单元检测数据的校验等,以确保待试元器件遥测数据传输的高效、可信。

任务4:打包遥测数据。将内总线指令回复链表内检测的待测元器件工作状态及试验数据按照单机与数管系统的外总线协议,打包成标准1553B 遥测帧,供数管系统按周期提取。

任务5:系统管理。主控处理器执行定时“喂狗”、内存循环自检以及重要技术参数保护等。

试验单元向主控处理器发送的信息包括:待试芯片工作状态、电源电流以及表面温度;28 nm 亿门级FPGA 的SEU、SEL 等;16 nm FinFET 的SEU等;高性能DAC 的SEFI、SEL、输出精度等参数。

4 在轨飞行验证结果及分析

本系统面向空间站定期开展芯片科学试验验证。为提前验证系统设计的可靠性,2021 年3 月12 日,该系统搭乘“实践九号”卫星升空[8],成功开展了国产先进制程芯片的在轨飞行试验。卫星被送入近地点高度200 km 的地球同步转移轨道,进入椭圆轨道后,在远地点点燃星上变轨发动机,经多次变轨后,顺利进入预定轨道。

在轨测试表明,此验证系统模拟量遥测正常、遥控指令执行正常、各试验单元试验数据下行正常,功能和性能满足研制要求,可为其将来在中国空间站的应用奠定了基础。

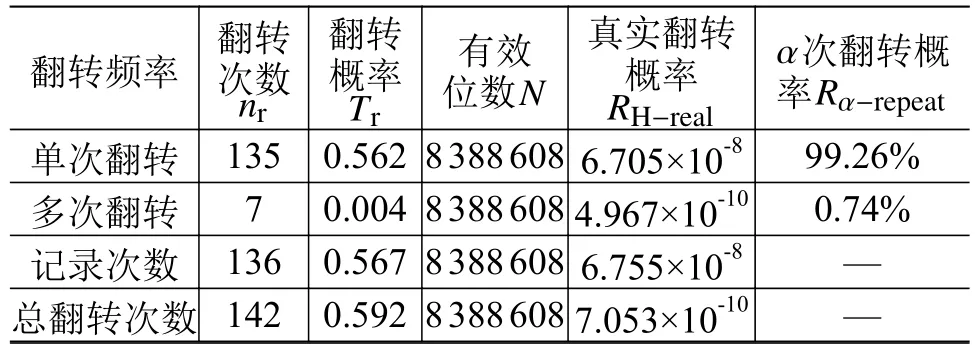

表4 为验证系统采集到的16 nm FinFET 1 个月的SEU 数据。该芯片将BRAM 配置成存储单元,存储单元的输入、输出、地址、时钟、使能、复位等信号都连接到主控FPGA 上。试验开始后,主控FPGA 复位待试FPGA,使能BRAM 写,将数据写入BRAM 进行初始化;激励数据为不同测试图形码(0x0000、0xFFFF、0x5A5A),每1 min 从BRAM中读取1 次数据并比较,连续读取并且比较2 次,如同一bit 的数值均与前次不同,则判断BRAM 发生了SEU 事件。

表4 16 nm FinFET 1 个月的SEU 数据Table 4 SEU data of 16 nm FinFET within one month

经分析:该芯片为非堆叠芯片,芯片内存储器由平铺式标准单元晶体管构成,短时间内同一地址发生多bit 翻转概率非常小。受读取速度和BRAM存储空间大小的影响,主控FPGA 每1 min 才完成所有BRAM 地址空间数据的遍历读取,1 次记录周期内的多次翻转数据可视为该器件1 min 内的累积SEU 次数。为提高系统采集SEU 次数的实时性,在保证试验单元模块正常开展其他试验的基础上,应尽量缩短待试芯片数据遍历读取周期,使试验数据更为真实。

在空间特定辐照环境中,非平衡载流子的漂移、扩散、寄生双极放大等效应会影响SRAM 型FinFET 的Fin 敏感区域。当Fin 敏感区域收集到足够的电荷,就会产生SEU[9]。根据卫星所处特定轨道待试芯片的SEU 数据,可分析单位时间内SEU 概率、在轨真实SEU 概率、多位翻转概率等(参见表5)。

表5 16 nm FinFET 6 个月的SEU 数据统计Table 5 SEU data statistics of 16 nm FinFET within six months

通过本系统得到待试芯片在轨真实SEU 概率RH-real,结合地面辐射模拟试验的SEU 概率RH,进行辐射效应机理研究。在空间辐射效应地面模拟试验中,预测器件的SEU 概率,通常依据重离子SEU概率计算模型

来计算RH,其中: Φ是与原子序数Z、质量数A、能量E及立体角有关的粒子通量; σ是有效翻转截面;L是重离子的线性能量传输(LET)值; ∅、θ分别是航天器飞行的球面坐标系统的方位角和极角。

空间辐射环境中粒子具有种类多、能量范围宽(每核子keV~10 GeV)、4π 立体角全向入射等特点[10]。目前地面模拟试验以粒子LET 作为评估辐射效应等效参量的重要指标,未考虑粒子种类和能量的差异,以及入射角对SEE 和预估方法的影响,存在局限性。比较芯片RH-real和RH计算模型,分析对芯片SEE 的影响因素有:1)16 nm 制程节点下,粒子从不同侧面入射时带来的边界效应的影响;2)器件内掺杂浓度、外加偏置、温度等因素,使粒子穿过时形成“漏斗效应”,促使节点电压翻转;3)倾斜入射产生的电荷径迹对相邻两个或多个敏感节点的影响。

此外,从表5 在轨飞行验证得到的16 nm FinFET的BRAM 发生SEU 的统计数据可知,SRAM 型FinFET 内部的BRAM 存储资源较容易发生单bit SEU。这可能是由于芯片内存储单元受辐照后,反相器开关阈值减小,漏电流增大,导致FPGA 的配置存储器抗翻转能力降低,SEU 截面增大[11]。由此,需进一步完善此类SRAM 型FPGA 芯片在轨飞行使用策略,如通过EDAC 检二纠一、三取二,或通过配置刷新芯片定时刷新等。

5 结束语

本文设计的先进制程芯片在轨飞行验证通用系统采用在轨可更换模块,共实现了10 类、20 余款国产先进制程芯片的在轨飞行验证,解决了多种国产先进制程芯片在空间辐射环境中的多样化验证问题,支持航天员定期在轨更换试验模块,完成新的空间辐照环境验证任务,实现芯片验证任务的在轨升级。系统已在卫星上初步搭载并且已获得芯片在轨真实SEU 概率,结合芯片地面等效重离子注量率下的辐照试验结果,推算出先进制程芯片在特定轨道环境、空间电场下入射重离子LET 值、SEU 概率等,开展了空间应用故障模式和辐射效应机理研究,助力探索不同工艺条件下的芯片空间SEU 特性,完善芯片在轨使用策略,为提高芯片技术成熟度和空间应用可靠性奠定基础,为提升国产先进制程芯片的研制能力并实现其自主可控提供了有力支撑。