基于FPGA 的HDB4 设计与实现

2023-12-31王善斌孟庆志

王善斌,孟庆志

(山东理工大学计算机科学与技术学院,山东淄博 255200)

在实际的数字基带通信系统中,为了减少码间串扰和噪声干扰使信息能够在基带中顺利传输,一般将不归零码(NRZ)信号编码成适合基带传输的码元信号。由于噪声干扰和其他原因,如取果在接收的数字序列中出现较长的连零,便可能导致定时信息的消失,使正常的数据接收失效,这是数字通信系统不能容忍的。在传输码的选择中,常常需要设计出满足信道各种特性的码型,其中,HDB3编码因为其优点较多且改进了AMI编码关于“连零”问题而成为常见的码型之一。HDB3的编码规则变化在当检测到4个连零时,会加入破坏字节。但编码后连零数只有3个,导致编码效率和传输效率过低。本文基于此,旨在通过FPGA设计出一种HDB4的编码,增加了对零的“容忍度”,增加了编码和传输的效率。HDB4具有如下特点:①不含直流,且低频分量少;②具有丰富的定时信息,利于提取定时信号;③功率谱主瓣宽度变小,提高了频带利用率;④具有检错能力;⑤编译码简单,传输时延小等。

1 HDB4 编码模块设计

1.1 HDB4 编码设计原理

HDB4 的基本原理同HDB3 基本一样,数据“1”正负交替,当检测到连零状态后,插入破坏节,其整体数据“V”码单独交替,“1”码和“B”码交替。HDB4 码的编码规则为:①取代。当信息遇到5 个连“0”二进制信息码用取代节“0000V”或“B000V”代替。取代的原则:简记为“V 奇数V”,即2 个“V”码之间“1”码的个数为奇数。②加符号。“V”码与前一非零码相同,其他相反。③画波形。HDB4 码波形的占空比为0.5。

HDB4 的编码主要分为三大模块,插入“V”码模块,负责“V”码的插入,并将信号进行“拓展”,1 位数据变为2 位数据;插入“B”码模块,对数据“1”进行计数,通过奇偶来判断是否需要插入“B”码,并在合适的时候插入;极性变换模块,将传输过来的信号进行类AMI编码。HDB4 设计的总体框架如图1 所示。

图1 HDB4 框架

1.2 插入“V”码

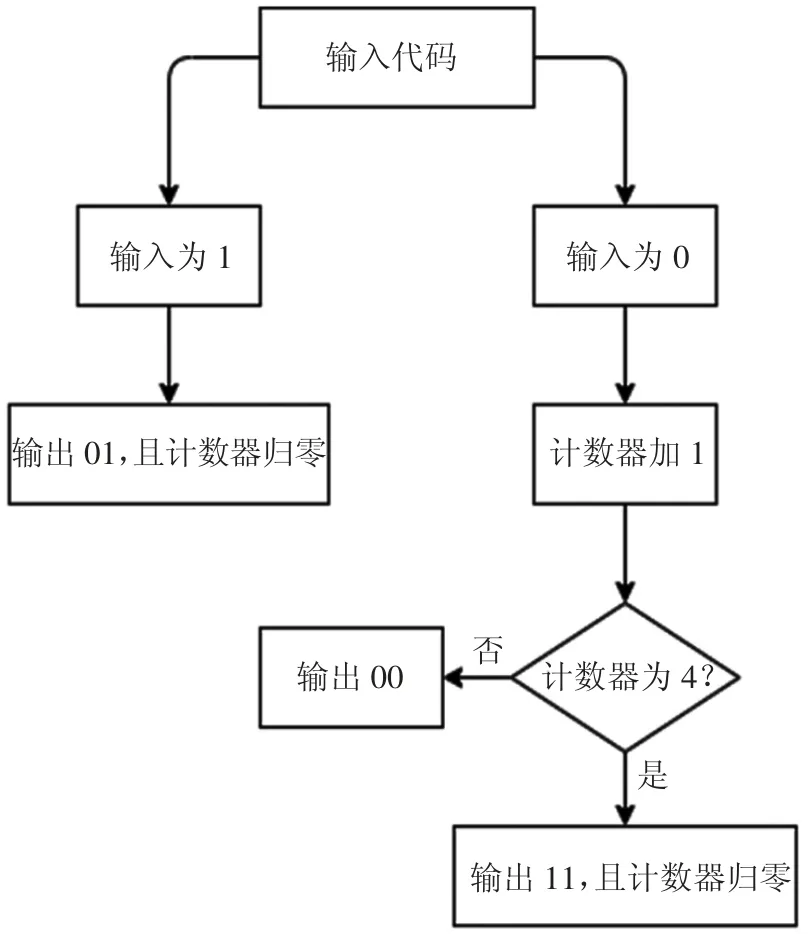

插入“V”码是数据传输的第一步过程。其基本设计流程如图2 所示。

图2 插入“V”码流程

输入数字信号后,根据输入的数据分别执行不同的程序。当输入为“1”时,令输出为“01”,并将检测连零数的计数器归零。如果输入为“0”时,则同时执行计数器加1 操作和计数器的判断操作,当检测到计数器计数为4 时,此时已经输入为第五个零,将第五个数据输入为零的输出设为11,并将计数器清零,其他情况则输出00。

经过此模块的数据比原数据均多一位,数字信息0 对应着00 和代表“V”码的11,数字信息1 对应着01。

1.3 插入“B”码

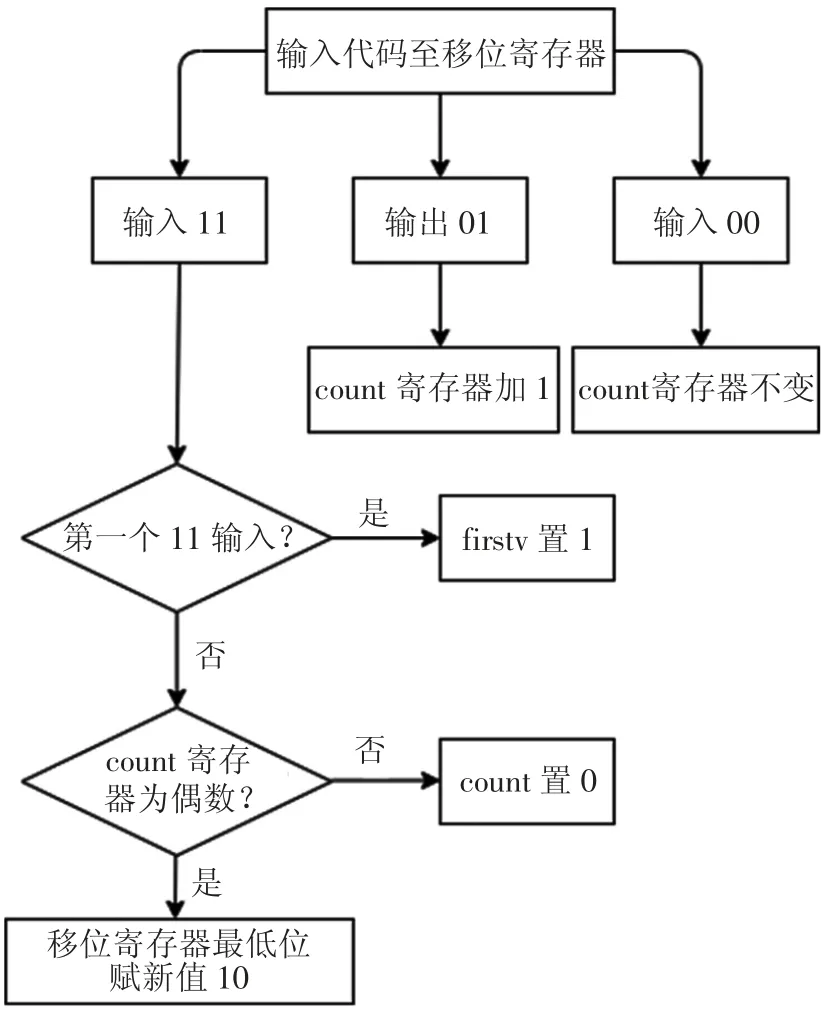

插入“B”码是数据传输的第二步过程。其基本设计流程如图3 所示。

图3 插入“B”码流程

这里采用5 位移位寄存器是根据HDB3 码编码规则的特点决定的,经插“V”后,连零串中的第5 个“0”变成“V”码,代码中的连零个数最多是4 个,而插入“B”码的操作是把在由“0”码变成“V”码之前的第一个非零码之后的“0”变换成“B”码,由此可见,得整个过程中信息数一定不超过5 个“0”,因此只需要5 个一位寄存器就可以通过输入状态来决定是否应插入“B”码。将信息代码中输出的信号一位一位地放进自己定义好的移位寄存器中,接下来进行判断:如果输入的是“00”,则自己设的判偶寄存器count 保持不变,5 个移位寄存器正常往后存信号;如果输入的是“01”,则判偶寄存器count 加1,5 个移位寄存器正常往后存信号;如果输入的是“11”,判断是否为第一个“11”输入,如果是,则将标志寄存器firstv 置为1,5 个移位寄存器正常往后存信号,如果不是,则判断判偶寄存器count 是否为偶数,如果不是,则将判偶寄存器count 置0,5 个移位寄存器正常往后存信号,否则,将这5 位移位寄存器的最低位寄存器赋值为“10”(这里面的“00”代表0,“01”代表“1”,“11”代表“V”)。

1.4 极性变换

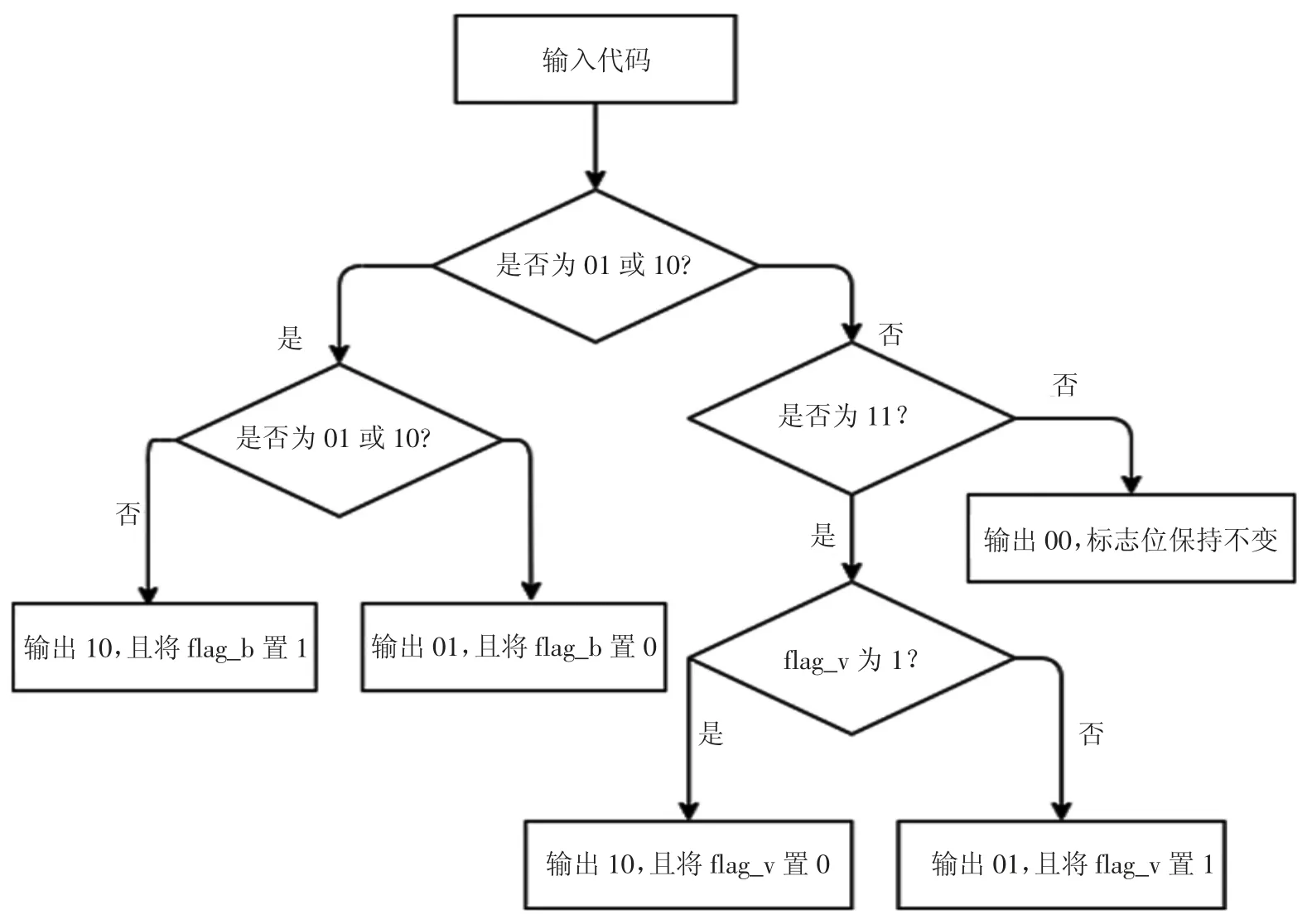

将信号双极性变换是数据传输的第三步过程。其基本设计流程如图4 所示。

图4 双极性变换流程

将插“B”码后的信号一位一位输入进去,判断是否为“01”或“10”码,如果是则判断标志位flag1b 是否为1,如果是,则输出“01”并且将flag_b 置0,若不是,则输出“10”,并将flag_b 置1;如果判断不是“01”或“10”码,则判断输入是否为“11”,如果不是则输出“00”,保持标志位flag 不变,如果是,则判断flag_v 是否为1,不是则输出“01”,是则输出“10”(此输出中的“10”代表正电平,“01”代表负电平,“00”代表零电平)。

2 HDB4 译码模块设计

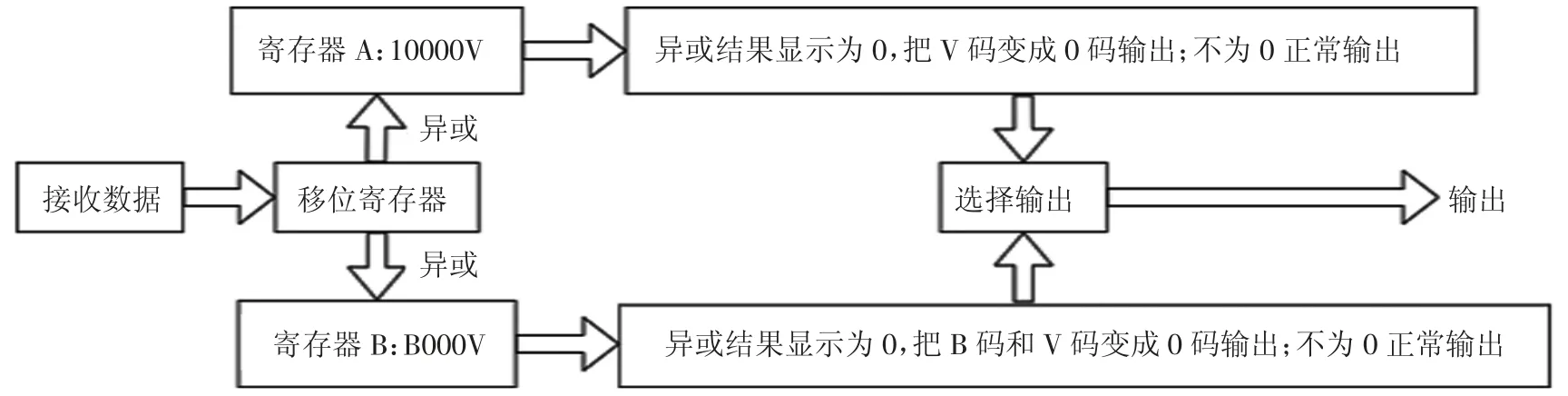

2.1 译码器的设计原理

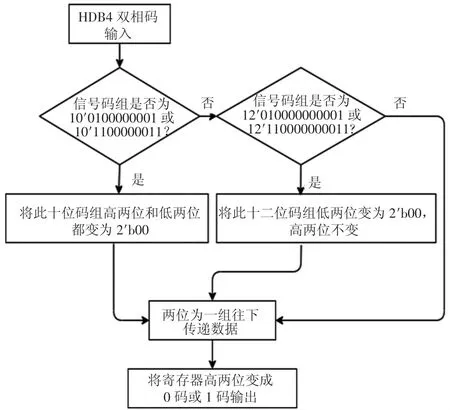

HDB4 的译码原理主要为发现取代节然后把取代节替换为5 个连零。其具体实现如下:在接收端收到的数据经过移位寄存器分别与寄存器A(存储“10000V”)和寄存器B(存储“B000V”)相异或,结果为零把“10000V”改成“100000”、把“B000V”改成“00000”输出。异或结果不为零正常输出。其译码原理方框图如图5 所示。在FPGA 收到已经译好的HDB3 码(双相码)后,根据是否为“XX 00 00 00 00 XX”或“ XX 00 00 00 XX ”的码型来进行扣“V”扣“B”的操作,最后在输出时将双相码转换为0 和1 码输出出去,方框图如图5 所示。流程图如图6 所示。

图5 译码器设计方框图

图6 译码器设计流程图

2.2 译码器相关主要代码分析

if((data [9:0]==10'b0100000001)||(data [9:0]==10'b1100000011))

begin

data[1:0]〈=messagein;

//messagein 为输入双相码信息

data[3:2]〈=2'b00;

data[5:4]〈=data[3:2];

data[7:6]〈=data[5:4];

data[9:8]〈=data[7:6];

data[11:10]〈=2'b00;

end//对B000V 码型进行扣B 扣V 操作

if((data[11:0]==12'b010000000001)||(data[11:0]==12'b110000000011))

begin

data[1

:0]〈=messagein;

data[3:2]〈=2'b00;

data[5:4]〈=data[3:2];

data[7:6]〈=data[5:4];

data[9:8]〈=data[7:6];

data[11:10]〈=data[9:8];

end//对10000V 码型进行扣V 操作

case(data[11:10])

2'b00:begin temp〈=1'b0; end

2'b01,2'b11:begin temp〈=1'b1; end

default:begin temp〈=1'bz; end

endcase

//将寄存器高两位转换成0 码或1 码并输出

3 FPGA 总体设计与仿真结果

3.1 FPGA 的总体设计

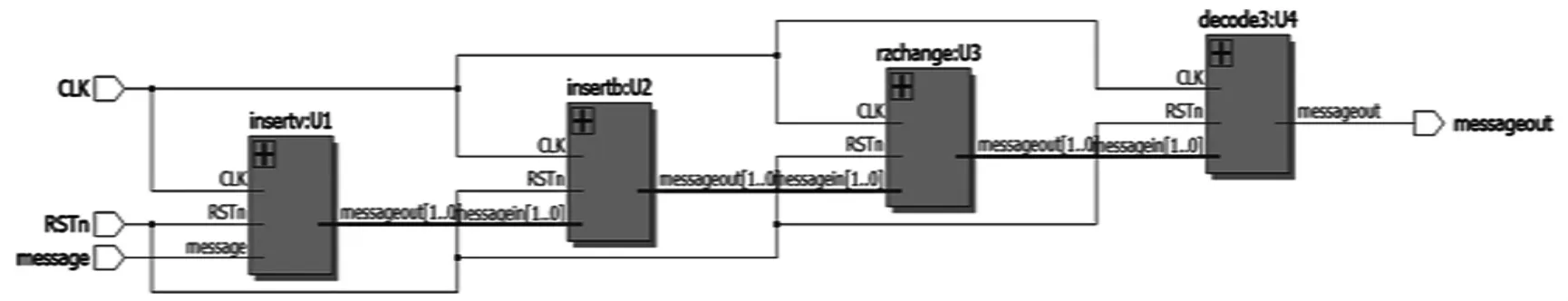

HDB4 编码原理RTL 框图如图7 所示,输入为一位的消息信号、时钟信号以及复位信号,经插V 模块、插B 模块、双极性变换模块以及译码模块这4 个模块后输出一位的译码信号。

图7 HDB4 编码原理RTL 框图

3.2 HDB4 编译码模块仿真分析

下面对该HDB4 模块进行仿真验证,仿真时钟设置为32 MHz,先进行复位再开始进行消息的传输,传输是在时钟的每个上升沿进行的(也就意味着一个时钟发送一个消息)。在总模块开始时,输入信息为“1000010000110000000011”,图8 中,第一行为时钟信号;第二行为复位信号;第三行为消息信号;第四行为插V 后的信号;第五行为插B 后的信号;第六行为双极性变换后的信号;第七行为译码后的信号。

图8 综合模块仿真图

4 结论

本文所设计的HDB4 编码模块简单易懂,在数字处理上利用FPGA 相较于单片机具有很高的灵活性,其可以集成到不同的通信系统中,提高系统设计的速度。

在本次设计之中也有一些需要注意的地方,比如写仿真文件在时钟信号最开始的时候一定要设置为1,否则将会在复位结束时比正常情况多发一个时钟的信息导致消息错乱;在译码传输数据时如果要对数据进行改动的话要直接对该寄存器的传输数据对象的寄存器进行改动,否则时序会错位,导致译码错误。