一款K 及KU 波段混频环的设计与实现

2023-12-28孙高勇张加程任浩铭

孙高勇,张加程,任浩铭

(中国电子科技集团公司第十三研究所,河北 石家庄 050051)

0 引 言

频率源广泛应用于雷达、电子对抗、通信等收发系统,其指标的好坏直接影响整个系统性能。按照频率的产生方式,频率源可分为锁相式频率源和直接合成式频率源。直接合成式频率源主要采用倍频和混频方式产生,在相位噪声指标方面有明显优势[1]。相位噪声是频率合成器的一个极为重要的指标,降低相位噪声是频率合成器的主要设计任务[2]。为满足电子系统对低相位噪声、低杂散、小频率步进以及小体积的要求,设计并制作了一款K 及KU 波段混频环,最终实物测试性能优良。

1 方案设计

设计一款K 及KU 波段混频环,输出频率为16 ~20 GHz,步进频率为100 MHz,相位噪声为-111 dBc/Hz@1 kHz, 杂散为-60 dBc, 体积为48 mm×40 mm×10 mm。该混频环主要包括主环和副环,主环的功能为产生16 ~20 GHz、步进为100 MHz的本振信号;副环的功能为产生14 ~17 GHz、步进为1 GHz 的射频信号。混频环通过将信号从高频段混频到低频段进行锁相的方式来降低相位噪声。

1.1 低相位噪声设计

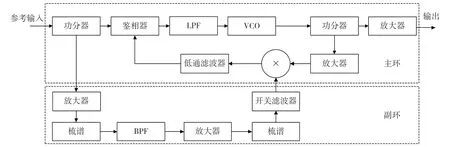

混频环的原理框架如图1 所示,其相位噪声主要由主环相位噪声、副环相位噪声综合决定。一般综合考虑频率步进、相位噪声、频率切换时间等技术指标,通过设计主环环路带宽来满足混频环的远近端相位噪声。

图1 混频环的原理框架

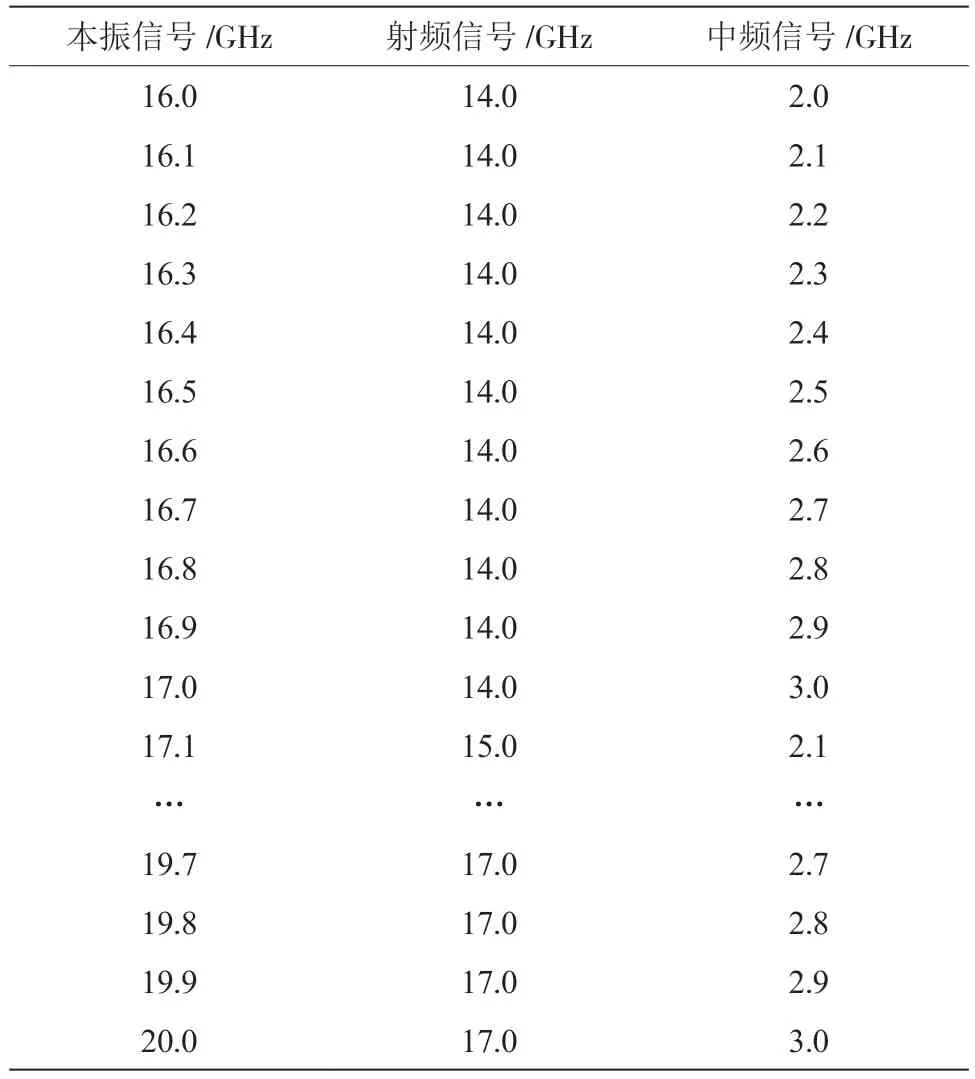

该混频环内部的频率变换关系如表1 所示,其中f中频信号=f本振信号-f射频信号。主环信号作为混频的本振信号,副环信号作为混频的射频信号,混频环通过16 ~20 GHz 主环信号与14 ~17 GHz 副环信号混频到2 ~3 GHz 的中频频段进行锁相,降低相位噪声。

表1 混频环内部的频率变换关系

1.1.1 副环电路低相位噪声设计

混频环通过2 级梳谱的方式产生副环信号,即100 MHz 输入信号经过1 级梳谱、滤波、放大后产生1 GHz 信号,1 GHz 信号再经过另外1 级梳谱、滤波、放大后产生14 ~17 GHz、步进为1 GHz 的信号。

在频率源中,利用梳谱信号发生器所产生的各次谐波,通过频率合成可得到点数很多的稳定频率输出,应用到雷达、通信、测量遥控以及仪器中[3]。从实现梳状谱倍频的方法上来看,由早期的非线性电阻二极管倍频发展到晶体三极管、变容二极管、阶跃恢复二极管倍频等。阶跃恢复二极管是对PN 结材料和结构采取特殊措施而设计的一种电容开关或变容管。在外加大信号交流电压的激励下,阶跃二极管呈现2 种阻抗状态,具有电容开关特性[4]。该产品中的梳谱电路原理为利用阶跃二极管的非线性特点产生丰富的谐波,达到倍频的目的。副环输出频率为17 GHz时,相位噪声最差,仿真曲线如图2 所示,相位噪声为-114 dBc/Hz@1 kHz。

1.1.2 主环电路低相位噪声设计

压控振荡器(Voltage Controlled Oscillator,VCO)产生的16 ~20 GHz 信号分为2 路,一路经过放大输出,另外一路经过放大后作为混频器的本振信号,与副环信号混频到2 ~3 GHz 频段进行锁相。其中VCO采用GaAs HBT 工艺,具有闪烁噪声低和热稳定好的特点[5]。

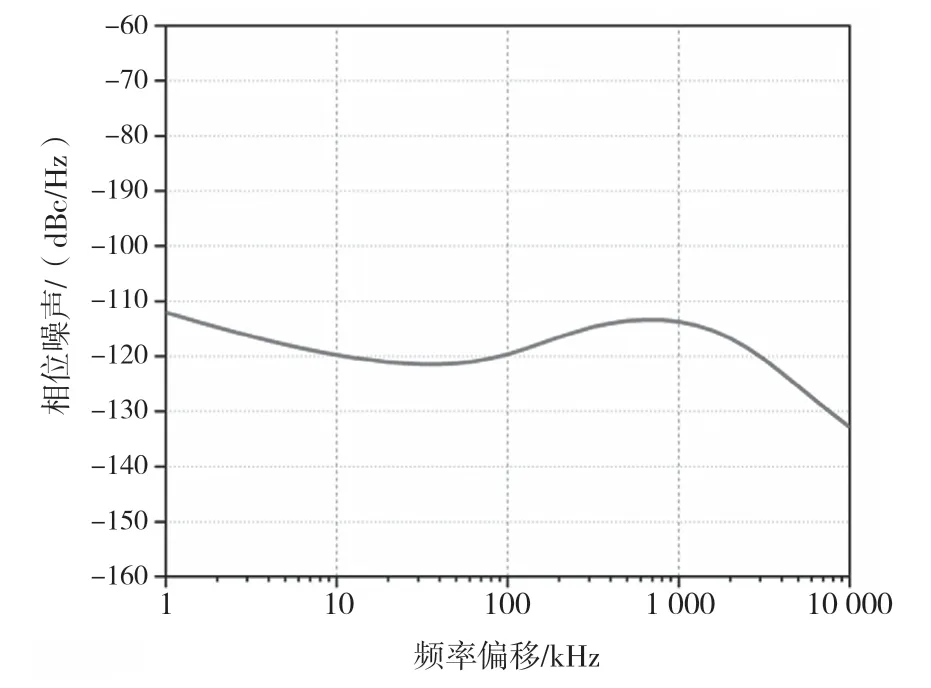

主环采用数字锁相方式,用于数字锁相的鉴相器在整数普通模式下具有-230 dBc/Hz 的归一化相位噪声;采用100 MHz 鉴相频率,混频环输出为20 GHz 时相位噪声最差,如图3 所示,其值为-112dBc/Hz@1 kHz。

图3 主环相位噪声仿真曲线

1.2 低杂散设计

混频环杂散按照传输路径,主要分为链路上产生的杂散、空间串扰产生的杂散。

1.2.1 链路上产生的杂散优化设计

为了优化链路上产生的杂散,主要采取以下几种措施。选择本振射频隔离度高、混频杂散特性合适的混频器;主环信号经过放大器后作为混频器的本振,用放大器反向隔离副环信号;主环信号与副环信号混频后,通过低通滤波器滤除高频分量,再取其差频作为主环鉴相器的射频信号;综合相位噪声、频率切换时间等指标,采用4 级有源环,并选取合适的环路带宽,降低鉴相泄露;对各器件供电电源进行充分的隔离滤波,防止电源串扰。

1.2.2 空间串扰产生的杂散优化设计

混频环内部同时存在主环信号、副环信号、中频信号,需要对不同的信号进行隔离处理,防止不同信号空间串扰。该产品结构通过压框将主环信号、副环信号、中频信号进行分腔,并且每个隔腔进行单独封盖处理,减小不同信号空间串扰。

2 测试结果

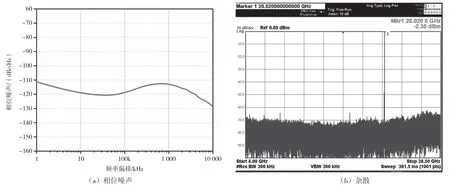

混频环的测试结果如图4 所示。由测试结果可知,该混频环的输出频率为16 ~20 GHz,步进频率为100 MHz,相位噪声为-111 dBc/Hz@1 kHz,杂散为-60 dBc。其中,混频环-111 dBc/Hz@1 kHz 的相位噪声实测值较图3 中主环-112 dBc/Hz@1 kHz的相位噪声仿真值恶化1 dB,这是由于图2 中副环-114 dBc/Hz@1 kHz 的相位噪声未优于图3 中主环-112 dBc/Hz@1 kHz 的相位噪声6 dB 以上,混频过程相位噪声恶化导致的,后续可根据测试结果优化副环相位噪声。

图4 混频环测试结果

3 结 论

设计研制的混频环,输出频率为16 ~20 GHz,步进频率为100 MHz,相位噪声为-111 dBc/Hz@1 kHz,杂散为-60 dBc,能够电子系统的低相位噪声低杂散应用需求。后续根据测试结果,将进一步优化相位噪声。