适用于车载网络的1553 总线通信模块设计

2023-12-24武宏吉陈凌珊

武宏吉,陈凌珊

(201620 上海市 上海工程技术大学 机械与汽车工程学院)

0 引言

随着汽车无人驾驶技术的迅速发展,汽车数据传输量越来越大,对车载网络的性能提出了更高的要求。当前车载网络使用的CAN 总线传输速率最高为1 Mb/s,无法满足未来车载网络的需求。同时CAN 总线使用的是电传输,容易被电磁干扰,不能满足完全无人驾驶技术高可靠性的要求[1]。

FC-AE-1553(简称1553)总线是在MILSTD-1553B 总线的基础上诞生的,作为军用总线标准,具备极高的传输速率与传输带宽,双冗余的拓扑结构与光纤传输的物理介质也使它拥有较高的传输稳定性[2]。与CAN 总线相比,1553 总线的优势在于速率快、可靠性高,缺点是成本高,实时性差[3]。如果将1553 总线应用到车载网络中,在关键链路使用1553 通信,在非关键链路使用CAN 通信,可以显著提高通信速度与可靠性,同时又不会大幅提高成本[4]。对于1553 总线和CAN 总线的转换,商伟峰[5]提出了基于FPGA 芯片的实现方法,其优点是具有高内聚性,可以减少板卡面积,降低开发成本;缺点是灵活性小,只能使用硬编码实现。

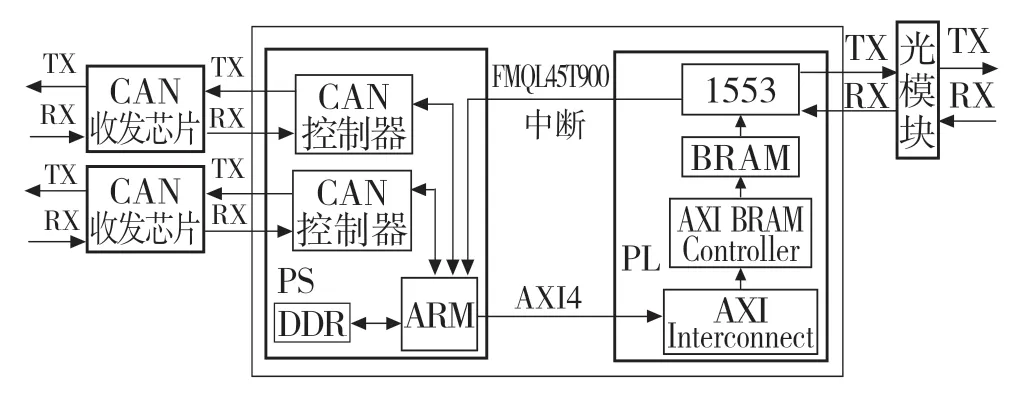

基于目前的设计方法,本文提出使用APSoC芯片实现CAN 与1553 的转换。相较于FPGA,APSoC 具有更高的灵活性,支持软硬件结合开发,降低了研发难度,并可以运行操作系统提高总线转换性能。选用复旦微公司的FMQL45T900 APSoC芯片作为总线通信模块的核心实现部分,该芯片分为PS 与PL 两大部分,PS 部分包括ARM 核心与2个CAN 控制器,运行锐华实时操作系统实现CAN通信以及内存管理[6];PL 部分类似FPGA 芯片,用于实现1553 总线功能[7]。利用PS 与PL 之间的AXI 通道实现CAN 与1553 的转换。

1 系统框架

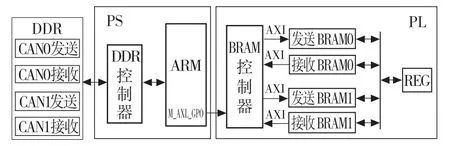

总线通信模块系统框图如图1 所示,该模块功能分为2 个方向,分别是CAN 转1553 与1553转CAN。CAN 转1553 方向:CAN 收发芯片收到CAN 总线上的数据,处理后发送到与其相连的CAN控制器。CAN 控制器收到数据后会发送中断信号给ARM 处理器,ARM 处理器上运行锐华系统,系统收到中断信号后会触发中断服务函数,将CAN 控制器收到的数据放入提前规划好的内存空间中[8]。当CAN 数据进入内存空间后,预先设计的系统线程会将CAN 数据从内存通过AXI 通道转移到PL 部分的BRAM 中,并配置相应的寄存器告诉1553 模块本次传输的数据大小与数据位置,最后1553 模块会将BRAM 中的CAN 数据打包成1553 格式发送到光模块中,光模块完成光电转换功能,将转化完成的1553 数据发送出去。

图1 总线通信模块系统框图Fig.1 Bus communication module system block diagram

1553 转CAN 方向:1553 模块首先收到光模块传送过来的数据,对数据进行处理,将1553 数据帧中包含的CAN 帧抽取出来,保存到指定的BRAM 中,同时配置相应的寄存器,发送中断信号给ARM 处理器。ARM 处理器根据寄存器中的信息判断CAN 数据存放的位置与大小,通过AXI 通道传输到DDR 当中。之后系统线程会对CAN 数据进行解析,并发送到指定的CAN 控制器中,完成1553 总线到CAN 总线的转换过程。

2 CAN 功能设计

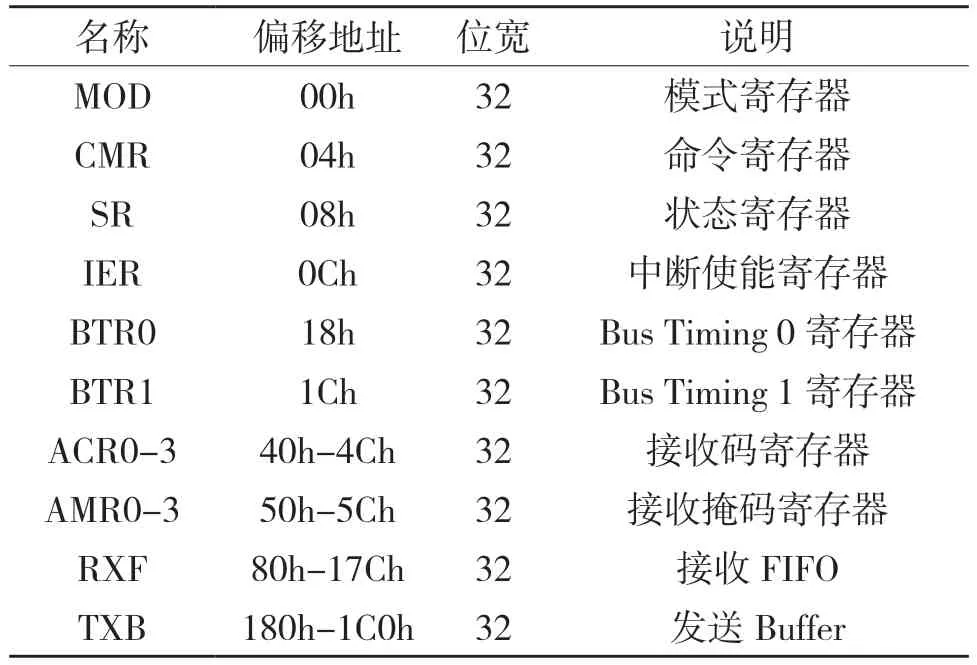

CAN 功能基于FMQL45T900 的CAN 控制器与锐华实时操作系统开发,CAN 控制器的寄存器手册如表1 所示。

表1 CAN 控制器寄存器手册Tab.1 CAN controller register manual

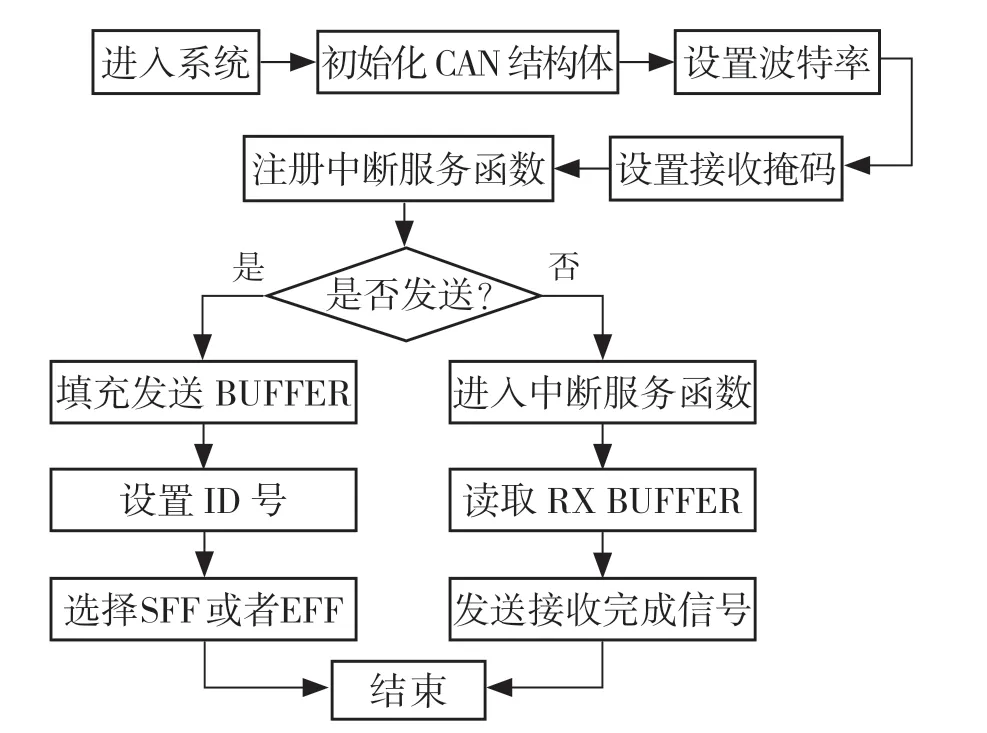

通过操作系统对MOD、CMR、SR、BTR 等寄存器进行操控以实现CAN 通信功能。进入系统后,首先为CAN 控制器抽象出2 个结构体用于表示CAN 的各个寄存器功能,然后根据2 个CAN 控制器的基地址为结构体进行指针赋值,让它们产生实际意义。根据需求对结构体进行初始化,配置波特率并进入正常工作模式,再设置接收掩码[9],最后为CAN 控制器注册中断服务函数,当CAN 控制器接收到数据时,系统会自动调用中断函数将数据放置到指定内存位置。CAN 控制器的整体工作流程如图2 所示。

图2 CAN 软件工作流程Fig.2 CAN software workflow

在发送部分,本次设计使用了2 种数据帧,分别是SFF(标准帧)与EFF(扩展帧),前者的ID 号为11 位,后者的ID 号为29 位,ID 号越小表示该帧的优先级越高,为了避免ID 号干扰测试结果,固定ID 号为0X400[10]。

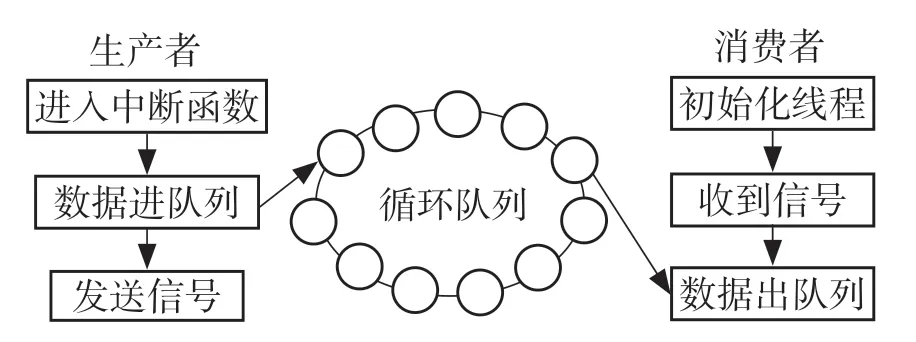

在接收部分,因为CAN 的中断触发速率较快,而将CAN 数据从内存搬运到BRAM 的速率较慢,为了解决这个问题,采用了生产者—消费者模型,如图3 所示。首先在内存中创建1 个循环队列用于存放数据,循环队列上每个单元可以存放1 个CAN 帧。当CAN 控制器收到数据后,系统调用中断服务函数,中断服务函数再调用进队列函数,将数据放到循环队列的单元中,并记录这个单元的位置,之后再利用锐华系统中的信号量机制,使用系统函数sem_post 给消费者线程发送信号。在CAN工作之前,先使用系统函数pthread_create 注册1个消费者线程,该线程会一直循环等待生产者给其发出的信号,当收到信号后调用出队列函数,将节点中的CAN 数据取出,同样也记录节点的位置,一般这个节点不会和生产者使用的节点重合。如果循环队列的节点已经被用完,则生产者会覆盖最原始的数据,并通知消费者,让其从被覆盖节点的下一个节点取出数据。通过这种模型,可以很好地解决数据接收过快导致无法及时处理的问题。

图3 生产者-消费者模型示意图Fig.3 Schematic diagram of producer-consumer model

3 1553 功能设计

3.1 1553 硬件设计

为支持1553 光纤信号多路收发功能,光模块选用中航光电的HTA8537-MD-T002YY,该模块支持12 路并行光收发一体,中心波长850 nm,单通道传输速率为10.312 5 Gbps,具备I2C 通信监控功能,使用3.3 V 单电源供电,原理图如图4 所示。

图4 HTA8537-MD-T002YY 原理图Fig.4 Schematic diagram of HTA8537-MD-T002YY

为了防止光模块状态异常导致损坏,使用I2C通信对其进行温度与电压监控,电压转换公式为

温度转换公式如式(2),温度为可正可负的有符号值。

3.2 1553 逻辑设计

在1553 协议中,共存在3 种信息单元,分别是命令帧、数据帧与状态帧。命令帧一般由NC 节点发出,用于控制NT 节点,数据帧用于各个节点之间传输数据,状态帧一般用于NT 节点向NC 节点反馈自己的状态,使NC 节点可以发出正确的命令[11]。1553 协议规定了10 种传输格式,本次设计实现了3 种最常见的格式,分别是NC-NT、NTNC、NT-NT。

(1)NC-NT 传输:NC 先给NT 发送命令帧,告知NT 节点即将给其发送数据,然后再发送数据帧,最后NT 节点向NC 节点反馈一个状态帧,告知其数据接收情况;(2)NT-NC 传输:NC 先给NT 节点发送命令帧,询问NT 节点是否有数据要发送,如果NT 节点有数据,会先给NC 节点发送一个状态帧表明即将发送数据,最后发送数据帧;(3)NT-NT 传输:NC 节点先给主NT 节点发送命令帧,询问其是否有数据要发送给从NT 节点。如果有,主NT 节点会发送给从NT 节点命令帧,让从NT 节点准备接收数据,然后再发送数据帧。最后主NT 节点会发送状态帧给NC 节点,告知本次传输已经结束。

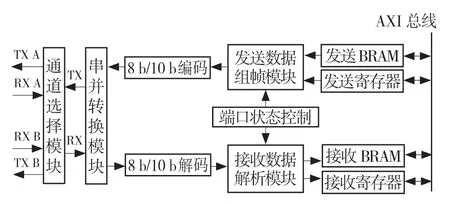

1553 模块功能框图如图5 所示。根据1553 协议的冗余设计要求,1553 模块收发有A 和B 两个通道,默认选择A 通道。如果A 通道出现故障,则立即切换到B 通道收发数据。如果两个通道同时出现故障,则向处理器报告错误。串行数据速率为2.125 Gb/s,串并转换模块按照该速率将串行数据转换成10位宽的并行数据以满足编解码的需求,编码与解码模块通过查表的方式实现8 b/10 b 编解码。端口状态控制一直监控解码模块的输出数据,如果监控到1553 协议规定的原语序列,状态机则会根据当前状态进行跳转,输出对应的原语直到端口链接成功。发送数据组帧模块会根据发送寄存器的控制去读取发送BRAM 中的数据,按照FC 帧的格式为其添加上SOF、帧头、CRC 以及EOF,完成组帧过程然后发送出去。接收数据解析模块会一直监控解码模块的输出信号,当检测到SOF 时,说明有数据进入,开始接收数据一直检测到EOF 停止。解析模块先进行帧处理,去除SOF、CRC 与EOF,然后将剩余的数据写入接收BRAM,同时配置接收寄存器,告知处理器此次接收数据的大小与位置。

图5 1553 模块功能框图Fig.5 1553 module function block diagram

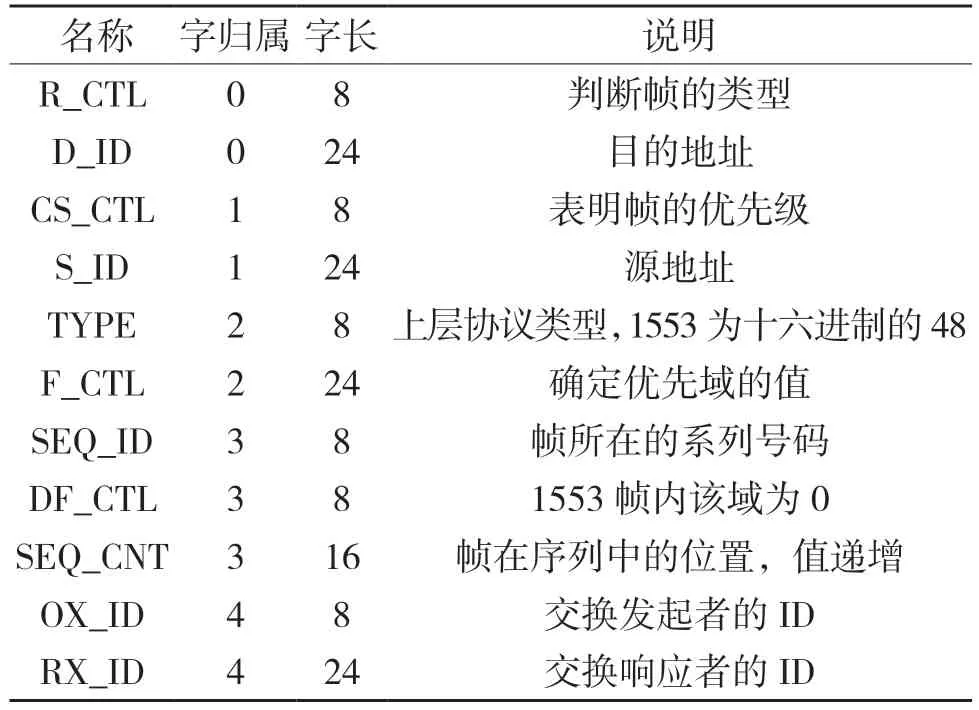

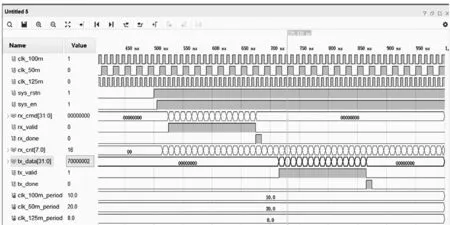

1553 的功能基于Vivado 软件使用verilog 语言进行开发,在进行实 际测试之前,先对1553 模块进行波形仿真以验证功能是否正常,仿真结果如图6所示。共设计了3 种速率的时钟125、100、50 M以适应不同的要求,当sys_en 信号被拉高后,NT节点进入工作状态,rx_cmd 为NC 节点发送给NT节点的命令帧,命令帧的字长为32 位,帧头部分的数据包含了帧类型、目标节点ID、源节点ID、优先级、序列位置等信息,共有12 字,本次设计所使用的命令帧帧头部分组成如表2 所示。

表2 命令帧帧头(部分)Tab.2 Command frame header (partial)

图6 NT 节点仿真结果Fig.6 NT node simulation result

NT 节点会解析这些信息,然后根据NC 节点的指令发送状态帧给NC 节点,状态帧的字长也为32 位,帧头前6 字和命令帧一样,另有两字的可选帧头用于NT-NT 的传输中,本次仿真并未使用,tx_data 表示NT 节点反馈给NC 节点的带有数据的状态帧,共12 字。当rx_valid 信号拉高时,提示PL 部分的其它功能模块rx_cmd 的信号有效,tx_valid 信号同理。当NT 节点完成了数据的接收或发送后,会将rx_done 或tx_done 信号拉高1 个脉冲,用于通知PS 部分传输已经完成。NC 节点向NT 节点发送命令帧询问其是否有数据要发送给NC节点,NT 节点反馈给NC 节点一个包含数据的状态帧,仿真结果符合预期。

4 1553 与CAN 总线的转换设计

CAN 控制器收到的数据会存放到PS 部分的内存中,1553 功能模块收到的数据会存放到PL 部分的内存中,为了实现1553 总线与CAN 总线的转换,核心任务是实现PS 内存与PL 内存之间的交互。PS 部分的内存使用DDR 内存芯片,PL 部分使用了BRAM 软核内存。BRAM 是由Xilinx 公司推出的IP 核,是PL 部分的存储器阵列,PS 和PL通过对BRAM 进行读写操作实现数据的交互[12]。BRAM 的优点是空间大小可灵活配置,成本低,适用于数据地址不连续、长度不规则的情况,同时因为BRAM 是软核IP,使用成本比内存芯片低。BRAM 是按照4 字节寻址,与1553 协议的字长相同,所以使用BRAM 去存储1553 数据开发难度较小。PS 部分通过DDR 控制器去读取DDR 中的数据,通过AXI 接口去操控BRAM 控制器,进而去控制BRAM 的读写,可以实现内存之间的交互,内存设计示意图如图7 所示。

图7 内存设计示意图Fig.7 Memory design diagram

在PS 的DDR 内存中,预留出4 块空间分别用于两路CAN 的收发,这4 块内存都有与其对应的BRAM。在CAN 转1553 的方向,前文中设计的消费者线程会将CAN 数据从DDR 内存搬运到发送BRAM 中,同时配置REG 寄存器,告知1553 模块数据存放的位置与大小,1553 模块对数据进行处理,完成CAN 转1553。在1553 转CAN 的方向,当1553 模块将接收到的数据储存到接收BRAM 中,同时根据数据的大小与储存位置配置寄存器,最后发送1 个中断信号给处理器,通知其准备接收数据。处理器在接收到中断信号后,从接收BRAM 中将数据搬运到相对应的DDR 内存空间,之后CAN 控制器对数据进行处理,完成1553 转CAN。

5 功能测试

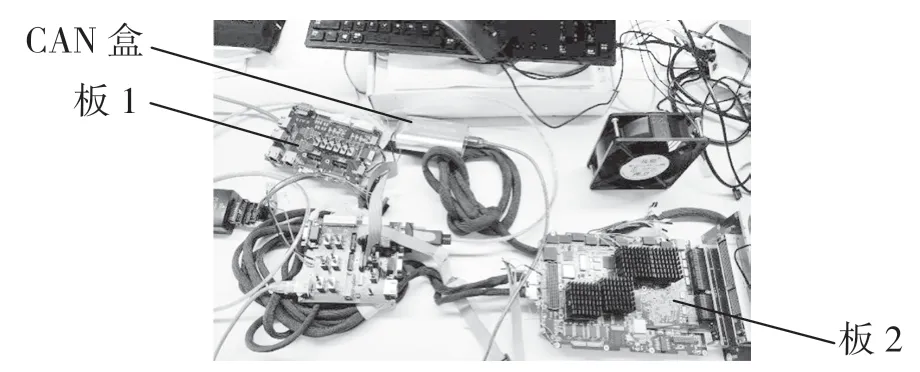

本次设计的总线通信模块实物图如图8 所示。板1 用于连接串口、网口、JTAG、CAN 接口等,板2 是转换模块的核心处理板,板1 与板2 用J63A 接口连接,测试所用的CAN 盒用于转换模块与上位机之间的CAN 通信。

图8 总线通信模块实物图Fig.8 Picture of communication module

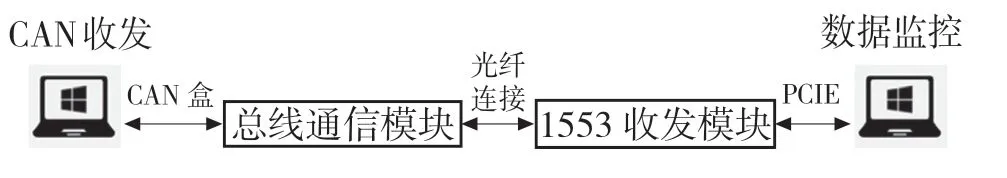

本次测试环境示意如图9 所示。CAN 收发上位机通过控制CAN 盒发送CAN 报文,总线通信模块收到CAN 报文后,将其转换为1553 报文格式的光纤信号发送到1553 收发模块,1553 收发模块不具备总线转换功能,只能收发1553 数据,通过PCIE 与数据监控上位机连接。1553 收发模块收到数据后发送给数据监控上位机,数据监控上位机运行1553 软件,可以监控1553 数据的收发情况,至此完成CAN 到1553 的转换测试。反方向,数据监控上位机控制1553 收发模块主动发送数据,则可以完成1553 到CAN 的转换测试。总线通信模块发送数据则作NC 节点,接收数据则作NT 节点。

图9 测试环境示意图Fig.9 Schematic diagram of test environment

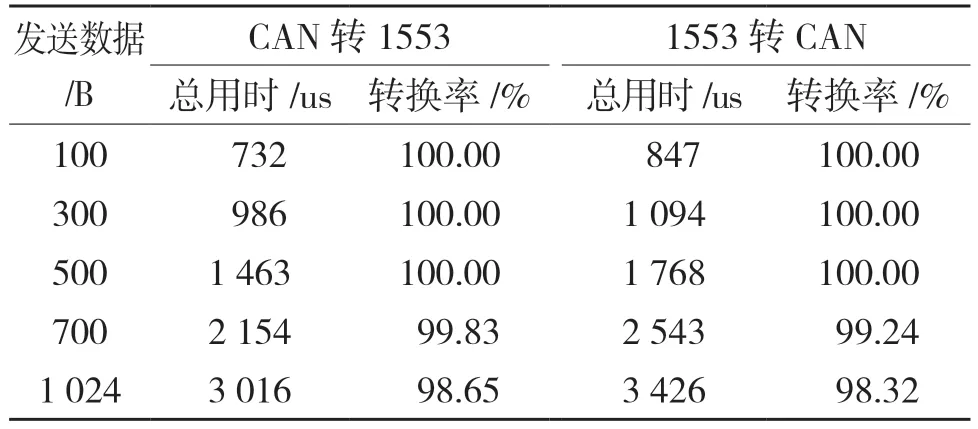

实验测试了多组不同大小的数据转换,结果如表3 所示。通过测试结果可以看出,在数据小于500 B 时,通信模块可以正常实现总线转换;当数据大于500 B 时,通信模块会出现小部分数据转换失败的现象,原因是数据量过大造成通道堵塞,进而引发数据丢失。

表3 总线转换测试结果Tab.3 Bus conversion test result

6 结论

(1)本文设计的通信模块可以实现CAN 与1553 的转换功能;

(2)APSoC 芯片应用于总线转换功能时,具有灵活性高、开发难度低、可软硬件结合的特点;

(3)将1553 总线应用于车载网络中,可极大提高车载网络的通信速率;

(4)目前该通信模块还不适用于大数据量的转换,需要进一步进行改进,扩宽数据通道。