一种基于FPGA 和STM32 双核的波形识别及参数测量装置设计

2023-12-08翁芸李伟

翁芸,李伟

(宁波职业技术学院,浙江宁波,315800)

0 引言

在仪器仪表中,经常需要测量信号的频率、幅值、失真度、占空比等参数,并根据这些参数来分辨信号的种类,测量的精度和识别的准确率是衡量仪器仪表性能高低的重要指标。

用单片机作为测量核心是目前的主流,其存在设计简单、成本低廉等优点,但因受单片机硬件资源的限制,产品的性能很难提升,也不利于升级换代。而随着芯片制造工艺的不断发展及市场需求量不断增加,FPGA 芯片的性能得到飞速的提升,价格也趋于稳定。FPGA 芯片由于其具有高度灵活、可扩展的特点,能够以更低的成本实现产品性能的提升和升级,受到市场的青睐。本文以FPGA 和STM32F4单片机为核心,设计一款波形识别及参数测量装置,测试该装置的性能并验证方案的可行性,为以后的类似产品研发打下基础。

1 系统方案设计

本装置主要组成为直流供电模块、信号调理电路、A/D 转换模块、过零比较电路、FPGA 信号采样及处理模块、STM32 主控模块、显示电路,各部分连接关系如图1 所示。

图1 系统结构框图

信号调理电路采用集成程控放大器,具备放大和衰减的功能,无须多路模拟开关,系统根据预测交流信号的幅值大小设定放大倍数,被测信号经过两级程控放大和一级同相放大后,波形已达到最佳测量幅值范围,再送至A/D 模块进行模数转换,可提高测量精度。

高速A/D 转换模块则将调理好后的交流信号转变成数字信号送至FPGA,为有效消除共模干扰信号,本设计采用差模转换方式。

FPGA 模块采用cyclone IV 系列EP4CE10F17C8 芯片,控制高速ADC 模块进行数据采集,通过高速并行口,配合FPGA内部的高速RAM,可轻松实现大于20MHz的采样速率,该模块除高速采集A/D 信号外,还要精确测量被测信号的频率,测量信号是通过过零比较电路得到。FPGA 将采集到的A/D 值和频率值通过FMC 接口传送给STM32 单片机。

STM32 主控模块采用STM32F429 单片机,根据按键值发送频率测量和数据采样启停控制信号,并利用自身强大的计算能力对采样到的数据进行RMS、FFT 等多种运算,得到被测信号的峰峰值、有效值、占空比、失真度等参数,并根据以上参数判断出波形类别,最终将波形及参数显示在液晶显示屏上。

显示模块选用电容串口液晶显示屏,串口的液晶显示屏功耗比较低,节能环保,只需要触摸,而不需要压力来产生信号,使用方法灵活、使用寿命长、显示高彩色保真、高亮、高对比度,其适用范围广,与传统显示屏相比,画面效果更佳。

2 硬件电路设计

■2.1 信号放大电路设计

为满足50mV ≤VPP ≤10V 宽幅值信号采样需求,信号放大部分采用AD603 集成程控放大器。程控放大电路主要由三个部分构成,分别是第一级调偏电路及AD603 程控放大电路、第二级调偏电路及AD603 程控放大电路、末级放大电路。为了使通带内输出平坦,在第一级和第二级之间加入低通滤波。图2 为AD603 程控放大电路原理图。

图2 AD603程控放大电路原理图

两级AD603 的增益控制引脚直接短接,实现增益的同步设置;末级运放可以根据实际需要来设计放大电路增益,放大电路类型是同相输入比例放大,由R6 和R5 的比值来确定增益值,本模块默认放大2 倍。电路增益通过STM32 内部D/A 控制,其输出电压经电平平移后生成VG信号,输出增益与VG 的关系为G(db)=80VG+20,VG 取值±500mV。

■2.2 A/D 转换模块电路设计

A/D 转换模块包括信号调理与A/D 转换电路两个部分,A/D 转换采用TI 公司的高速12bit、最大采样速率65MSPS的芯片AD9226。其硬件结构框图如图3 所示,包括信号输入接口、衰减电路、信号调理电路和高速A/D 芯片等。

图3 A/D 转换模块结构框图

信号输入电压范围为-5V~+5V,即峰峰值≤10Vpp。电压调理电路转换公式为:VAD=-(1/5)VIN+2。当输入信号VIN=+5V的时候,输入到A/D 的信号VAD=1V;当输入信号VIN=0V的时候,输入到A/D 的信号VAD=2V;当输入信号VIN=-5V的时候,输入到A/D的信号VAD=3V;模块转换后的数字量D 和输入VIN之间的关系为:D=2048 -(1/5)VIN× 2048。A/D转换模块原理图如图4所示。

图4 A/D 转换模块原理图

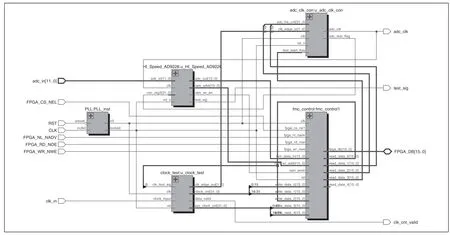

■2.3 FPGA 模块顶层设计

FPGA 模块是本项目的核心,需要完成频率测量和波形采样两大任务,其顶层设计如图5 所示,共有5个模块组成,分别是PLL 模块、频率测量模块、ADC 时钟控制模块、AD9226控制模块和FMC 控制模块。

图5 FPGA 顶层设计图

PLL 锁相环模块用于生成高频时钟信号,通过调用IP核完成,输入时钟50M,输出时钟信号为150M,供其他模块电路使用。

频率测量模块(clock_test)采用等精度频率测量法,该模块受STM32 控制,当clk_test_sig 为高电平时开始测量,测得的值通过FMC 模块传送至单片机,为保证A/D 采样时序与被测信号同步,该模块还为ADC 时钟控制模块提供被测信号的同步时钟信号(clk_edge_out)。

ADC 时钟控制模块(adc_clock_con)用于产生被测信号的128 倍频时钟信号,该时钟信号需与被测信号的过零点同步,以确保每次采样信号的初始相位一致,便于后期数据处理及计算,频率控制值是STM32 通过FMC 接口传送给FPGA。倍频后的时钟信号(adc_clk)直接送至A/D 转换电路,作为该模块的驱动时钟信号。

AD9226 控制模块(HI_Speed_AD9226)用于将采集到的A/D 值保存到FPGA 内部高速RAM 中,需根据ADC 时钟控制模块提供的信号(adc_test_flag)同步采集,一次测量数据采集结束后,生成数据有效信号,通知STM32 读取数据。

FMC(fmc_control)控制模块用 于FPGA 和STM32 的高速通信,内部设有5 个数据读写通道和一个1024*16 高速RAM,5 个数据读写通道可以双向传递控制命令和数据,而RAM 只用于单向数据传送,FPGA 负责写入,STM32 只能将数据读出。

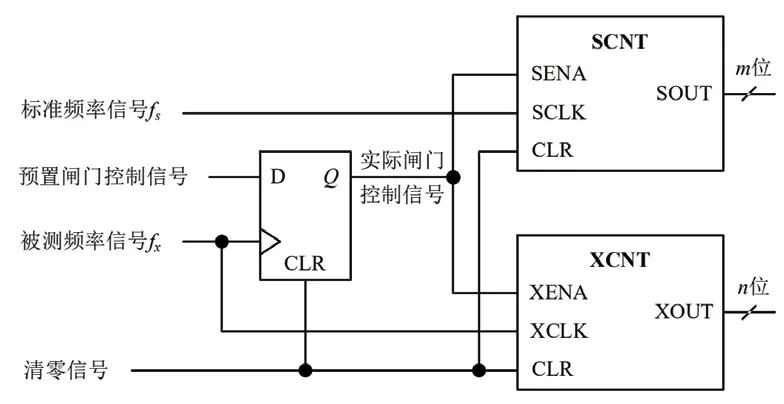

2.3.1 频率测量模块设计

频率测量常用的方法有直接测频法、直接测周法和等精度测量法。因被测信号的频率范围较宽(1Hz~50kHz),为保证测量精度,本设计采用等精度测量法,原理框图如图6 所示。

图6 等精度测频原理图

频率测量主要由FPGA 完成,测量启动信号即预置门控信号由STM32 发送给FPGA,只需发送一个短脉冲即可,FPGA 收到信号后首先检测被测信号的上升沿,检测到以后立刻开启门控定时器,生成0.5 秒实际门控信号,并同时开启SCNT 和XCNT 两个计数器,分别对标准信号fs 和被测信号fx 进行计数,当0.5 秒门控时间到了以后,FPGA 再次检测被测信号的上升沿,检测到以后立刻停止SCNT 和XCNT 两个计数器并将数据锁存在Ns 和Nx 寄存器中,同时生成频率测量数据有效信号,通知STM32 读取数据并进行计算,被测频率计算公式为:fx=(Nx/Ns)×fs。

2.3.2 信号采集模块设计

AD9226 单路高速A/D 模块是在芯片时钟的上升沿进行数据的采集,根据设计要求,对于不同频率的被测信号,都要采集128 个点,所以采样频率始终是被测频率的128 倍,这个频率控制值由STM32 根据被测信号的频率计算获得,通过FMC 接口传送给FPGA,然后下达采样开始命令。

FPGA 检测到采样开始命令后,把过零比较电路生成的方波信号的上升沿作为同步信号,控制A/D 转换模块按照被测信号频率的128 倍频速率连续采样128 个点(为消除倍频系数误差产生的影响,实际采样192 个点),并把采样数据按顺序存储到FPGA 内部RAM 中。采样结束后,FPGA 通过FMC 双向通道通知STM32 读取数据,STM32检测到信号后,按顺序读取FPGA 内部RAM 中的数据并存放至自己的内存中,以供后面的参数计算使用。FPGA 信号采集时序图如图7 所示。

图7 FPGA 信号采集时序图

3 软件设计

■3.1 主流程图

STM32 单片机主要完成按键检测、测量命令发送、数据计算、波形识别及LCD 屏显示等功能,其流程图如图8 所示。

图8 STM32 主流程图

■3.2 波形识别及参数测量算法

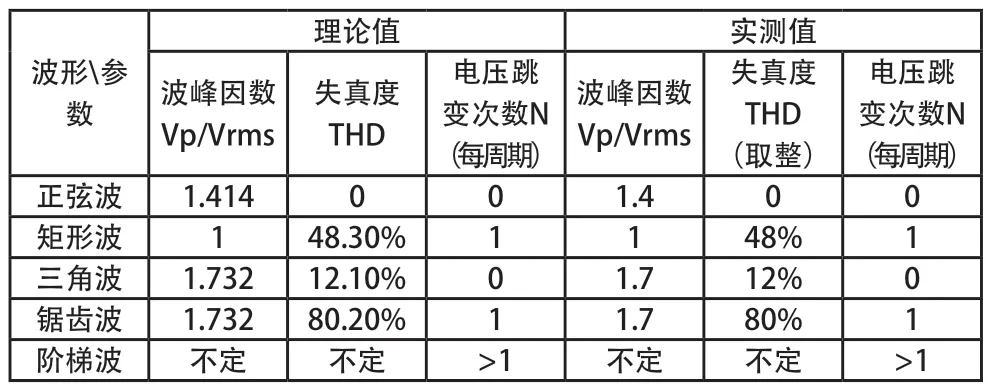

波形识别最常用方法为波峰系数识别法(峰值与有效值的比值),可以分辨出矩形波、正弦波和三角波,但光靠波峰系数一个参数还是无法分辨更多的波形,比例锯齿波、阶梯波等,本设计采用波峰系数、失真度、电压跳变次数三个参数综合分析法,可以有效分辨以上所有波形。

波形识别前先要对采样数据进行必要的处理和计算,根据上面同步信号可知,过零信号为采样起始点,所以两个相邻上穿(或下穿)零轴之间的数据即为一个完整周期数据,把这些数据提取出来用于各参数计算。需要注意的是,正常的话一个完整周期应该是128 个点,如果不是,说明倍频值计算存在误差,需要对系统主时钟或采样点数进行调整,不然计算参数时会产生较大误差。另外,之所以取128 个点,一是为了提高测量精度,二是为满足STM32 单片机FFT 运算要求。如果要测量更高的频率信号,可以适当降低采样点数,但必须是2 的n 次方。

所有参数的计算都由STM32 单片机完成,F4 系列单片机具有基于ARM Cortex M4 的高性能32 位微控制器,并且采用DSP 和FPU 指令,可以高效完成有效值和FFT 运算,计算速度和精度都达到设计要求,根据实际测试,各参数值与理论值非常接近,完全达到精确辨别波形要求。各波形波峰系数、失真度和电压跳变次数的理论参数值与实测参数值如表1 所示。

表1 各波形参数理论值与实测值

本装置按照先波峰系数、再失真度、后电压跳变次数识别顺序,只要各参数的比较阈值选择合理,识别成功率达到100%。

4 实验测试结果

最后经多次实测,频率、峰峰值及波形识别的测试结果如表2 所示。

5 结论

本设计充分发挥FPGA 高速并行性能和STM32 单片机强大计算能力,通过两者的协同工作,能精确测量周期性信号的幅值、频率、失真度等参数,误差远小于1%,并能根据测得的数据判断不同波形,正确率达100%,完全达到设计预期效果,本设计对于未来开发高性能的电子测量设备具有一定的借鉴意义。